SHENZHEN AV-DISPLAY CO., LTD

深圳秋田视佳实业有限公司

地址:深圳市华侨城东部工业区文昌街东北 C-7 栋

电话:(086)0755-26919178 传真: (086)0755 -26911092

网址:<u>Http://www.av-display.com.cn</u>

**Customer Approval:**

SHENZHEN AV-DISPLAY CO.,LTD

Address:North East C-7 Building, Wenchang Street Eastern District, OCT, ShenZhen, China

TEL: (086)0755-26919178 FAX: (086)0755-26911092

Http://www.av-display.com.cn

## **SPECIFICATION FOR LCM MODULE**

**MODULE NO.: CBS084A00-TJN DOC.REVISION: 00**

|                              | SIGNATURE | DATE        |

|------------------------------|-----------|-------------|

| PREPARED BY<br>(RD ENGINEER) |           | Jun-29-2005 |

| PREPARED BY<br>(QA ENGINEER) |           |             |

| CHECKED BY                   |           |             |

| APPROVED BY                  |           |             |

### **DOCUMENT REVISION HISTORY**

| Version | DATE        | DESCRIPTION | CHANGED BY |

|---------|-------------|-------------|------------|

| 00      | Jun-29-2005 | First issue |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

|         |             |             |            |

### **CONTENTS**

| 1. Functions & Features             | 2     |

|-------------------------------------|-------|

| 2. Mechanical specifications        | 2     |

| 3. Block diagram                    | 2     |

| 4. Dimensional Outline              | 3     |

| 5. Pin description                  | 4     |

| 6. Display RAM Mapping              | 4~5   |

| 7. Functional Description           | 6     |

| 8. Maximum absolute limit           | 7     |

| 9. Electrical characteristics       | 7~9   |

| 10. Timing Characteristics          | 9~10  |

| 11. Control and display command     | 11~12 |

| 12. Electro-Optical characteristics | 13    |

| 13. Quality Specifications          | 13~22 |

#### SHENZHEN AV-DISPLAY CO., LTD

#### 1. FUNCTIONS & FEATURES

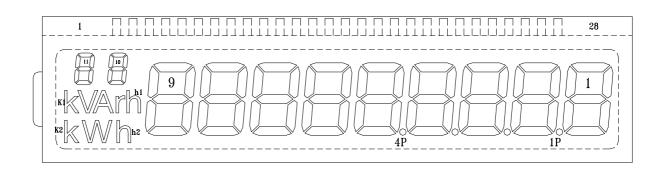

1.1. Format :7-segment Characters+ICONS : TN / Positive, Reflective Mode 1.2. LCD mode

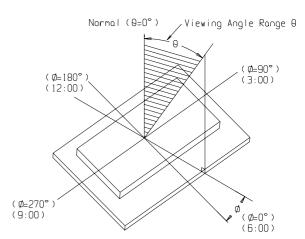

1.3. Viewing direction : 12 o'clock

1.4. Driving scheme : 1/4 Duty cycle, 1/3 Bias

1.5. Power supply voltage  $(V_{DD})$ : 4.5 V

1.6. VLCD supply voltage : 4.0V (adjustable for best contrast)

1.7. Operation temp : -20~70 1.8. Storage temp : -30~80 1.9. LCM operation current : I 1.5mA

#### 2. MECHANICAL SPECIFICATIONS

2.1. Module size :66.0mm(L)\*26.0mm(W)\*Max5.0mm (H)

2.2. Viewing area :62.0mm(L)\*11.0mm(W)

2.3. Weight : Approx.

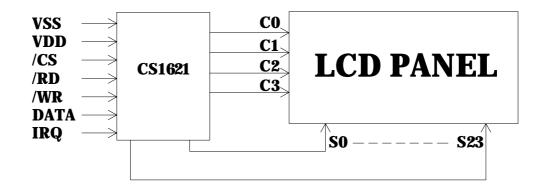

#### 3. BLOCK DIAGRAM

Figure 1. Block diagram

### 4. DIMENSIONAL OUTLINE

### **5. PIN DESCRIPTION**

#### INTERFACE:

| NO. | ITEM | DESCRIPTION                                      |

|-----|------|--------------------------------------------------|

| 1   | /CS  | Chip selection input with pull-high resistor     |

| 2   | /RD  | RADE clock input with pull-high resistor         |

| 3   | /WR  | WRITE clock input with pull-high resistor        |

| 4   | DATA | Serial data input/output with pull-high resistor |

| 5   | VSS  | Ground                                           |

| 6   | VDD  | Positive power supply                            |

| 7   | /IRQ | Time base or WDT over flow flag                  |

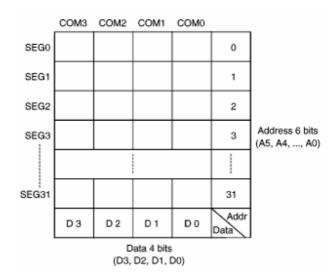

### 6. Display RAM Mapping

|       | Com3       | Com2 | Com1 | ComO |    |

|-------|------------|------|------|------|----|

| Seg0  | K1         | H1   | Α    | W    | 0  |

| Seg1  | V          | K2   | R    | H2   | 1  |

| Seg2  | 11A        | 11F  | 11E  | 11D  | 2  |

| Seg3  | 11B        | 11G  | 11C  |      | 3  |

| Seg4  | 10A        | 10F  | 10E  | 10D  | 4  |

| Seg5  | 10B        | 10G  | 10C  |      | 5  |

| Seg6  | 9A         | 9F   | 9E   | 9D   | 6  |

| Seg7  | 9B         | 9G   | 9C   |      | 7  |

| Seg8  | 8A         | 8F   | 8E   | 8D   | 8  |

| Seg9  | 8B         | 8G   | 8C   |      | 9  |

| Seg10 | 7A         | 7F   | 7E   | 7D   | 10 |

| Seg11 | 7B         | 7G   | 7C   |      | 11 |

| Seg12 | 6A         | 6F   | 6E   | 6D   | 12 |

| Seg13 | 6B         | 6G   | 6C   |      | 13 |

| Seg14 | 5 <b>A</b> | 5F   | 5E   | 5D   | 14 |

| Seg15 | 5B         | 5G   | 5C   |      | 15 |

| Seg16 | 4A         | 4F   | 4E   | 4D   | 16 |

| Seg17 | 4B         | 4G   | 4C   | 4P   | 17 |

| Seg18 | 3A         | 3F   | 3E   | 3D   | 18 |

| Seg19 | 3B         | 3G   | 3C   | 3P   | 19 |

| Seg20 | 2A         | 2F   | 2E   | 2D   | 20 |

| Seg21 | 2B         | 2G   | 2C   | 2P   | 21 |

| Seg22 | 1A         | 1F   | 1E   | 1D   | 22 |

| Seg23 | 1B         | 1G   | 1C   | 1P   | 23 |

#### 7. Functional Description

#### 7.1 Display memory -- RAM

The static display memory (RAM) is organized into 32x4 bits and stores the displayed data. The contents of the RAM are directly mapped to the contents of the LCD driver. Data in the RAM can be accessed by the READ, WRITE, and READ-MODIFY-WRITE commands. The following is a mapping from the RAM to the LCD pattern:

#### 7.2 Command Format

The CS1621 can be configured by the S/W setting. There are two mode commands to configure the CS1621 resources and to transfer the LCD display data. The configuration mode of the CS1621 is called command mode, and its command mode ID is 100. The command mode consists of a system configuration command, system frequency selection command, a LCD configuration command, a tone frequency selection command, a timer/WDT setting command, and an operating command. The data mode, on the other hand, includes READ, WRITE, and READ-MODIFY-WRITE operations. The following are the data mode IDs and the command mode ID:

| Operation         | Mode    | ID  |

|-------------------|---------|-----|

| READ              | Data    | 110 |

| WRITE             | Data    | 101 |

| READ-MODIFY-WRITE | Data    | 101 |

| COMMAND           | Command | 100 |

The mode command should be issued before the data or command is transferred. If successive commands have been issued, the command mode ID, namely 100, can be omitted. While the system is operating in the non-successive command or the non-successive address data mode, the CS pin should be set to "1" and previous operation mode will be reset also. Once the CS pin returns to "0" a new operation mode ID should be issued first.

#### **8. MAXIMUM ABSOUTE LIMIT**

| Supply Voltage0.3V~5.5V                                  | Storage Temperature50°C~125°C  |

|----------------------------------------------------------|--------------------------------|

| Input VoltageV <sub>SS</sub> -0.3V~V <sub>DD</sub> +0.3V | Operating Temperature25°C~75°C |

<sup>\*</sup>Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

#### 9. ELECTRICAL CHARACTERISTICS

#### **D.C.** Characteristics

Ta=25

| Symbol            | mbol Parameter           |          | Test Conditions       | Min. | т    | Max. | Unit |

|-------------------|--------------------------|----------|-----------------------|------|------|------|------|

| Symbol            | Parameter                | $V_{DD}$ | Conditions            | Min. | Тур. | Max. | Unit |

| $V_{\mathrm{DD}}$ | Operating Voltage        | _        | _                     | 2.4  | _    | 5.2  | V    |

| I                 | One-making Courses       | 3V       | No load/LCD ON        | _    | 150  | 300  | μA   |

| IDD1              | Operating Current        | 5V       | On-chip RC oscillator | _    | 300  | 600  | μА   |

| Inna              | Operating Current        | 3V       | No load/LCD ON        | _    | 60   | 120  | μΑ   |

| $I_{DD2}$         | Operating Current        | 5V       | Crystal oscillator    | _    | 120  | 240  | μΑ   |

|                   | Connating Current        | 3V       | No load/LCD ON        | _    | 100  | 200  | μA   |

| $I_{DD3}$         | Operating Current        | 5V       | External clock source | _    | 200  | 400  | μA   |

|                   | St Il C                  | 3V       | No load               | _    | 0.1  | 5    | μA   |

| ISTB              | Standby Current          | 5V       | Power down mode       | _    | 0.3  | 10   | μA   |

|                   | It I V-lt                | 3V       | DATA, WR. CS. RD      | 0    | _    | 0.6  | V    |

| V <sub>IL</sub>   | Input Low Voltage        | 5V       | DATA, WK, CS, RD      | 0    | _    | 1.0  | V    |

| VIH               | Torrest History Maltanes | 3V       | DATA, WR. CS. RD      | 2.4  | _    | 3.0  | V    |

| VIH               | Input High Voltage       | 5V       | DATA, WK, CS, KD      | 4.0  | _    | 5.0  | V    |

|                   | DATA, BZ. BZ. IRQ        | 3V       | V <sub>OL</sub> =0.3V | 0.5  | 1.2  | _    | mA   |

| $I_{OL1}$         | DATA, BZ, BZ, IRQ        | 5V       | Vol=0.5V              | 1.3  | 2.6  | _    | mA   |

| Іоні              | DATA, BZ. BZ             | 3V       | SV VoH=2.7V           |      | -0.8 | _    | mA   |

| 10H1              | DATA, DZ, BZ             | 5V       | Von=4.5V              | -0.9 | -1.8 | _    | mA   |

| Tota              | LCD Common Sink          | 3V       | VoL=0.3V              | 80   | 150  | _    | μA   |

| Iol2              | Current                  | 5V       | V <sub>OL</sub> =0.5V | 150  | 250  | _    | μA   |

| Lorus             | LCD Common Source        | 3V       | V <sub>OH</sub> =2.7V | -80  | -120 | _    | μA   |

| IOHS              | Current                  | 5V       | VoH=4.5V              | -120 | -200 | _    | μА   |

| Tour              | LCD Segment Sink         | 3V       | Vol=0.3V              | 60   | 120  | _    | μA   |

| Iot3              | Current                  | 5V       | Vol=0.5V              | 120  | 200  | _    | μA   |

| Louis             | LCD Segment Source       | 3V       | V <sub>OH</sub> =2.7V | -40  | -70  | _    | μA   |

| I <sub>OH3</sub>  | Current                  | 5V       | V <sub>OH</sub> =4.5V | -70  | -100 | _    | μA   |

| D                 | Dull bish Desister       | 3V       | DATA, WR. CS. RD      | 40   | 80   | 150  | kΩ   |

| $R_{PH}$          | Pull-high Resistor       | 5V       | DATA, WK, CS, KD      | 30   | 60   | 100  | kΩ   |

Figure 3. DC Characteristics

### SHENZHEN AV-DISPLAY CO., LTD

#### 2. A.C. Characteristics

Ta=25

| Symbol                          | Donomoton                                                                                                         |                                            | Test Conditions       | Min.   | Two                     | Max. | Unit |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------------|--------|-------------------------|------|------|

| Symbol                          | Parameter                                                                                                         | V <sub>DD</sub>                            | Conditions            | WIIII. | Тур.                    | wax. | Omt  |

| £                               | Suntana Clark                                                                                                     | 3V                                         | On this DC soulleton  | _      | 256                     | _    | kHz  |

| fsys1                           | System Clock                                                                                                      | 5V                                         | On-chip RC oscillator | _      | 256                     | _    | kHz  |

| £                               | System Cleak                                                                                                      | 3V                                         | Crystal oscillator    |        | 32.768                  | _    | kHz  |

| f <sub>SYS2</sub>               | System Clock                                                                                                      | 5V                                         | Crystal oscillator    | _      | 32.768                  | _    | kHz  |

| f                               | Sustana Clark                                                                                                     | 3V                                         | External clock source | _      | 256                     | _    | kHz  |

| f <sub>SYS3</sub>               | System Clock                                                                                                      | 5V                                         | External clock source | _      | 256                     | _    | kHz  |

|                                 |                                                                                                                   |                                            | On-chip RC oscillator | _      | f <sub>SYS1</sub> /1024 | _    | Hz   |

| fLCD                            | LCD Clock                                                                                                         |                                            | Crystal oscillator    | _      | f <sub>SYS2</sub> /128  | _    | Hz   |

|                                 |                                                                                                                   |                                            | External clock source | _      | fsys3/1024              | _    | Hz   |

| tcom                            | LCD Common Period                                                                                                 | _                                          | n: Number of COM      | _      | n/fLCD                  | _    | s    |

| fclk1                           | Serial Data Clock (WR pin)                                                                                        | 3V                                         | Duty cycle 50%        | _      | _                       | 150  | kHz  |

| ICLKI                           | Serial Data Clock (WK pili)                                                                                       | 5V                                         | Duty tytle 30%        | _      | _                       | 300  | kHz  |

| f <sub>CLK2</sub>               | Serial Data Clock (RD pin)                                                                                        | rial Data Clock (PD pin) 3V Duty ovala 50% | Duty cycle 50%        |        | _                       | 75   | kHz  |

| 1CLK2                           | Serial Data Clock (KD pill)                                                                                       | 5V                                         | Duty cycle 30%        | _      | _                       | 150  | kHz  |

| ftone                           | Tone Frequency                                                                                                    | _                                          | On-chip RC oscillator | _      | 2.0 or 4.0              | _    | kHz  |

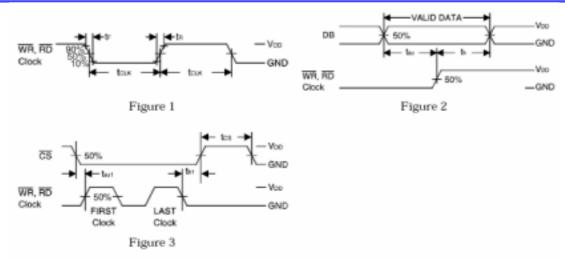

| tcs                             | Serial Interface Reset Pulse<br>Width (Figure 3)                                                                  | _                                          | CS                    | _      | 250                     | _    | ns   |

|                                 |                                                                                                                   | 3V                                         | Write mode            | 3.34   | _                       | _    |      |

| tclk                            | WR, RD Input Pulse Width                                                                                          | οv                                         | Read mode             | 6.67   | _                       | _    | μs   |

| ICLK                            | (Figure 1)                                                                                                        | 5V                                         | Write mode            | 1.67   | _                       | _    | 116  |

|                                 |                                                                                                                   | 3 V                                        | Read mode             | 3.34   | _                       | _    | μs   |

| to to                           | Rise/Fall Time Serial Data                                                                                        | 3V                                         |                       |        | 120                     |      | ns   |

| t <sub>R</sub> , t <sub>F</sub> | Clock Width (Figure 1)                                                                                            | 5V                                         | _                     |        | 120                     |      | 115  |

| t                               | Setup Time for DATA to WR,                                                                                        | 3V                                         |                       |        | 120                     |      | ns   |

| t <sub>su</sub>                 | RD Clock Width (Figure 2)                                                                                         | 5V                                         | _                     |        | 120                     |      | 115  |

| th                              | Hold Time for DATA to WR,<br>RD Clock Width (Figure 2)                                                            | 3V                                         | _                     | _      | 120                     | _    | ns   |

|                                 | , 0                                                                                                               | •                                          |                       |        |                         |      |      |

| t <sub>su1</sub>                | Setup Time for $\overline{CS}$ to $\overline{WR}$ , $\overline{RD}$<br>Clock Width (Figure 3)                     | 3V                                         | _                     | _      | 100                     | _    | ns   |

|                                 |                                                                                                                   | •                                          |                       |        |                         |      |      |

| thi                             | Hold Time for $\overline{\text{CS}}$ to $\overline{\text{WR}}$ , $\overline{\text{RD}}$<br>Clock Width (Figure 3) | 3V<br>5V                                   | _                     | _      | 100                     | _    | ns   |

#### SHENZHEN AV-DISPLAY CO., LTD

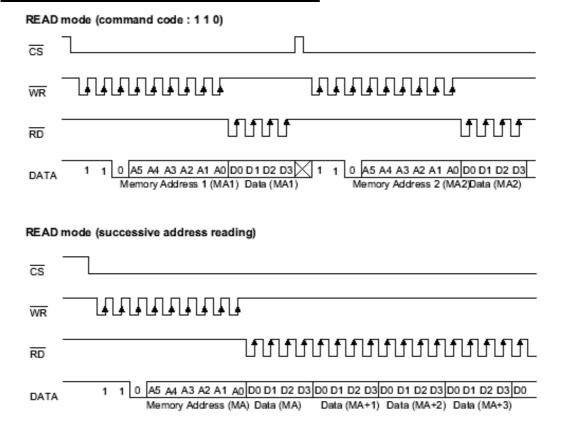

#### 10. TIMING CHARACTERISTICS

| WRITE | Command mode (command code : 1 0 0) mode (command code : 1 0 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| cs    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

| WR    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _          |

| DATA  | 1 0 1 A5 A4 A3 A2 A1 A0 D0 D1 D2 D3 1 0 1 A5 A4 A3 A2 A1 A0 D0 D1 D2 Memory Address 1 (MA1)Data (MA1) Memory Address 2 (MA2)Data (MA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D3<br>2)   |

| WRITE | mode (successive address writing)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

| cs    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| WR    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>₽</b> L |

| DATA  | 1 0 1 A5 A4 A3 A2 A1 A0 D0 D1 D2 D3 Memory Address (MA) Data (MA) Data (MA+1) Data (MA+2) Data (MA+3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D0         |

| READ- | Note: It is recommended that the host controller should read in the data from the DATA line between the rising edge of the RD line and the folling edge of the next RD line MODIFY-WRITE mode (command code: 101)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

| CS    | <b>1</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

| WR    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| RD    | וער דינוער דינוער                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | IJ         |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| DATA  | 1 0 1 A5 A4 A3 A2 A1 A0 D0 D1 D2 D3 D0 D1 D2 D3 1 0 1 A5 A4 A3 A2 A1 A0 D0 D1 Memory Address 1 (MA1)Data (MA1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

|       | 1 0 1 A5 A4 A3 A2 A1 A0 D0 D1 D2 D3 D0 D1 D2 D3 1 0 1 A5 A4 A3 A2 A1 A0 D0 D1  Memory Address 1 (MA1)Data (MA1) Data (MA1) Memory Address 2 (MA2)Data (MODIFY-WRITE mode (successive address accessing)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

|       | Memory Address 1 (MA1)Data (MA1) Data (MA1) Memory Address 2 (MA2)Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| READ  | Memory Address 1 (MA1)Data (MA1) Data (MA1) Memory Address 2 (MA2)Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| READ. | Memory Address 1 (MA1)Data (MA1) Data (MA1) Memory Address 2 (MA2)Data (MA1)Data (MA1) | (MA2)      |

### SHENZHEN AV-DISPLAY CO., LTD

### 11. CONTROL AND DISPLAY INSTRUCTION

| Name                      | ID  | Command Code         | D/C | Function                                                                                             | Def. |

|---------------------------|-----|----------------------|-----|------------------------------------------------------------------------------------------------------|------|

| READ                      | 110 | A5A4A3A2A1A0D0D1D2D3 | D   | Read data from the RAM                                                                               |      |

| WRITE                     | 101 | A5A4A3A2A1A0D0D1D2D3 | D   | Write data to the RAM                                                                                |      |

| READ-<br>MODIFY-<br>WRITE | 101 | A5A4A3A2A1A0D0D1D2D3 | D   | READ and WRITE to the RAM                                                                            |      |

| SYS DIS                   | 100 | 0000-0000-X          | С   | Turn off both system oscillator<br>and LCD bias generator                                            | Yes  |

| SYS EN                    | 100 | 0000-0001-X          | С   | Turn on system oscillator                                                                            |      |

| LCD OFF                   | 100 | 0000-0010-X          | С   | Turn off LCD bias generator                                                                          | Yes  |

| LCD ON                    | 100 | 0000-0011-X          | С   | Turn on LCD bias generator                                                                           |      |

| TIMER DIS                 | 100 | 0000-0100-X          | С   | Disable time base output                                                                             |      |

| WDT DIS                   | 100 | 0000-0101-X          | С   | Disable WDT time-out flag<br>output                                                                  |      |

| TIMER EN                  | 100 | 0000-0110-X          | С   | Enable time base output                                                                              |      |

| WDT EN                    | 100 | 0000-0111-X          | С   | Enable WDT time-out flag<br>output                                                                   |      |

| TONE OFF                  | 100 | 0000-1000-X          | С   | Turn off tone outputs                                                                                | Yes  |

| TONE ON                   | 100 | 0000-1001-X          | С   | Turn on tone outputs                                                                                 |      |

| CLRTIMER                  | 100 | 0000-11XX-X          | С   | Clear the contents of time base generator                                                            |      |

| CLR WDT                   | 100 | 0000-111X-X          | С   | Clear the contents of WDT stage                                                                      |      |

| XTAL 32K                  | 100 | 0001-01XX-X          | С   | System clock source, crystal oscillator                                                              |      |

| RC 256K                   | 100 | 0001-10XX-X          | С   | System clock source, on-chip RC oscillator                                                           | Yes  |

| EXT 256K                  | 100 | 0001-11XX-X          | С   | System clock source, external clock source                                                           |      |

| BIAS 1/2                  | 100 | 0010-abX0-X          | С   | LCD 1/2 bias option<br>ab=00: 2 commons option<br>ab=01: 3 commons option<br>ab=10: 4 commons option |      |

| BIAS 1/3                  | 100 | 0010-abX1-X          | С   | LCD 1/3 bias option<br>ab=00: 2 commons option<br>ab=01: 3 commons option<br>ab=10: 4 commons option |      |

| TONE 4K                   | 100 | 010X-XXXX-X          | С   | Tone frequency, 4kHz                                                                                 |      |

| TONE 2K                   | 100 | 011X-XXXX-X          | С   | Tone frequency, 2kHz                                                                                 |      |

| TRQ DIS                   | 100 | 100X-0XXX-X          | С   | Disable IRQ output                                                                                   | Yes  |

#### SHENZHEN AV-DISPLAY CO., LTD

| Name   | ID  | Command Code | D/C | Function                                                                   | Def. |

|--------|-----|--------------|-----|----------------------------------------------------------------------------|------|

| IRQ EN | 100 | 100X-1XXX-X  | С   | Enable IRQ output                                                          |      |

| F1     | 100 | 101X-X000-X  | С   | Time base/WDT clock<br>output:1Hz<br>The WDT time-out flag after: 4s       |      |

| F2     | 100 | 101X-X001-X  | С   | Time base/WDT clock<br>output:2Hz<br>The WDT time-out flag after: 2s       |      |

| F4     | 100 | 101X-X010-X  | С   | Time base/WDT clock<br>output:4Hz<br>The WDT time-out flag after: 1s       |      |

| F8     | 100 | 101X-X011-X  | С   | Time base/WDT clock<br>output:8Hz<br>The WDT time-out flag after: 1/2 s    |      |

| F16    | 100 | 101X-X100-X  | С   | Time base/WDT clock<br>output:16Hz<br>The WDT time-out flag after: 1/4 s   |      |

| F32    | 100 | 101X-X101-X  | С   | Time base/WDT clock<br>output:32Hz<br>The WDT time-out flag after: 1/8 s   |      |

| F64    | 100 | 101X-X110-X  | С   | Time base/WDT clock<br>output:64Hz<br>The WDT time-out flag after: 1/16 s  |      |

| F128   | 100 | 101X-X111-X  | С   | Time base/WDT clock<br>output:128Hz<br>The WDT time-out flag after: 1/32 s | Yes  |

| TEST   | 100 | 1110-0000-X  | C   | Test mode, user don't use.                                                 |      |

| NORMAL | 100 | 1110-0011-X  | С   | Normal mode                                                                | Yes  |

Note: X : Don't care

A5~A0 : RAM addresses D3~D0 : RAM data

D/C : Data/command mode Def. : Power on reset default

All the bold forms, namely 1 10, 101, and 100, are mode commands. Of these, 100 indicates the command mode ID. If successive commands have been issued, the command mode ID except for the first command will be omitted. The source of the tone frequency and of the time base/WDT clock frequency can be derived from an on-chip 256kHz RC oscillator, a 32.768kHz crystal oscillator, or an external 256kHz clock. Calculation of the frequency is based on the system frequency sources as stated above. It is recommended that the host controller should initialize the HT1621 after power on reset, for power on reset may fail, which in turn leads to the malfunctioning of the HT1621.

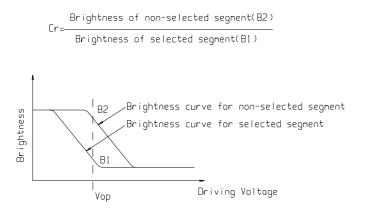

#### 12. ELECTRO-OPTICAL CHARACTERISTICS

| Item                | Symbol | Condition           | Min | Тур | Max | Unit |  |

|---------------------|--------|---------------------|-----|-----|-----|------|--|

| Operating Voltage   | Vop    | $Ta = -20^{\circ}C$ | 4.3 | 4.5 | 4.7 |      |  |

|                     |        | $Ta = 25^{\circ}C$  | 3.8 | 4.0 | 4.2 | V    |  |

|                     |        | $Ta = 70^{\circ}C$  | 3.3 | 3.5 | 3.7 |      |  |

| Response time       | Tr     | Ta = 25°C           |     | 185 |     | ms   |  |

|                     | Tf     | 1a – 25 C           |     | 200 |     | ms   |  |

| Contrast            | Cr     | $Ta = 25^{\circ}C$  |     | 4   |     |      |  |

| Viewing angle range | θ      | Cr 2                | -20 |     | +20 | deg  |  |

|                     |        |                     | -20 |     | +20 | deg  |  |

#### **13.QUALITY SPECIFICATIONS**

#### 13.1 Standard of the product appearance test

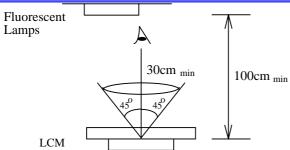

Manner of appearance test: The inspection should be performed in using 20W x 2 fluorescent lamps. Distance between LCM and fluorescent lamps should be 100 cm or more. Distance between LCM and inspector eyes should be 30 cm or more.

Viewing direction for inspection is 45° from vertical against LCM.

#### SHENZHEN AV-DISPLAY CO., LTD

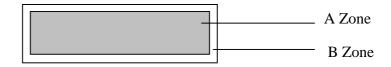

Definition of zone:

A Zone: Active display area (minimum viewing area). B Zone: Non-active display area (outside viewing area).

#### 13.2 Specification of quality assurance

AQL inspection standard

Sampling method: MIL-STD-105E, Level II, single sampling

**Defect classification** (Note: \* is not including)

| Classify |               | Item                         | Note | AQL  |

|----------|---------------|------------------------------|------|------|

| Major    | Display state | Short or open circuit        | 1    | 0.65 |

|          |               | LC leakage                   |      |      |

|          |               | Flickering                   |      |      |

|          |               | No display                   |      |      |

|          |               | Wrong viewing direction      |      |      |

|          |               | Contrast defect (dim, ghost) | 2    |      |

|          |               | Flat cable or pin reverse    | 10   |      |

|          | Non-display   | Wrong or missing component   | 11   |      |

|          |               | Black spot and dust          | 3    |      |

| Minor    | Display       | Line defect, Scratch         | 4    | 1.0  |

|          | state         | Rainbow                      | 5    |      |

|          |               | Chip                         | 6    |      |

|          |               | Pin hole                     | 7    |      |

|          |               | Protruded                    | 12   |      |

|          |               | Bubble and foreign material  | 3    |      |

|          |               | Poor connection              | 9    |      |

|          | Polarizer     | Poor connection              | 10   |      |

|          | Soldering     | Position, Bonding strength   | 13   |      |

|          | Wire          |                              |      |      |

|          | TAB           |                              |      |      |

### SHENZHEN AV-DISPLAY CO., LTD

#### Note on defect classification

| No. | Item                                                 | Criterion                                                |      |       |                                                                 |                            |

|-----|------------------------------------------------------|----------------------------------------------------------|------|-------|-----------------------------------------------------------------|----------------------------|

| 1   | Short or open circuit                                | Not allow                                                |      |       |                                                                 |                            |

|     | LC leakage                                           |                                                          |      |       |                                                                 |                            |

|     | Flickering                                           |                                                          |      |       |                                                                 |                            |

|     | No display                                           |                                                          |      |       |                                                                 |                            |

|     | Wrong viewing direction                              |                                                          |      |       |                                                                 |                            |

|     | Wrong Back-light                                     |                                                          |      |       |                                                                 |                            |

| 2   | Contrast defect                                      |                                                          | Refe | er to | approval san                                                    | nple                       |

|     | Background color deviation                           |                                                          |      |       |                                                                 |                            |

| 3   | Point defect, Black spot, dust (including Polarizer) | <u></u>                                                  |      |       | Point<br>Size                                                   | Acceptable Qty.  Disregard |

|     | (merading 1 oldrizer)                                | A                                                        |      | 0.    | φ <u>&lt;</u> 0.10<br>.10<φ 0.20                                | 3                          |

|     | (M. M. O                                             |                                                          |      |       | .20<\( \phi \ 0.25                                              | 2                          |

|     | $\phi = (X+Y)/2$                                     |                                                          |      | 0.    | .25<\( \phi \ 0.30                                              | 1                          |

|     |                                                      |                                                          |      |       | φ>0.30                                                          | 0                          |

|     |                                                      | Unit: mm                                                 |      |       |                                                                 |                            |

| 4   | Line defect,                                         | <u> </u>                                                 |      |       |                                                                 |                            |

|     | Scratch                                              | w                                                        |      | ı     | Line                                                            | Acceptable Qty.            |

|     | Scratch                                              | <b>←</b> >                                               | L    |       | 0.015 W                                                         | Disregard                  |

|     |                                                      | L                                                        | 3.0  | L     | 0.03 W                                                          | 2                          |

|     |                                                      |                                                          | 2.0  | L     | 0.05 W                                                          | 1                          |

|     |                                                      |                                                          | 1.0  | L     | 0.1 > W<br>0.05 <w< td=""><td>Applied as point defect</td></w<> | Applied as point defect    |

|     |                                                      | Unit: mm                                                 |      |       |                                                                 |                            |

| 5   | Rainbow                                              | Not more than two color changes across the viewing area. |      |       |                                                                 |                            |

| No | Item                                                                     | Criterion                                                                   |  |  |  |  |

|----|--------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|

| 6  | Chip  Remark: X: Length direction Y: Short                               | Acceptable criterion $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |  |  |  |  |

|    | direction  Z: Thickness direction  t: Glass thickness  W: Terminal Width | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                       |  |  |  |  |

|    |                                                                          | Acceptable criterion    X   Y   Z                                           |  |  |  |  |

|    |                                                                          | Acceptable criterion $\begin{array}{c ccccccccccccccccccccccccccccccccccc$  |  |  |  |  |

|    |                                                                          | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                       |  |  |  |  |

| No. | Item                                                        | Criterion                                                                                                                                                                                                                                           |  |  |  |  |

|-----|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7   | Segment pattern $W = \text{Segment width}$ $\phi = (X+Y)/2$ | (1) Pin hole $\phi < 0.10 \text{mm is acceptable.}$ $X$                                                                                                                                                                                             |  |  |  |  |

|     |                                                             | Point Size Acceptable Qty                                                                                                                                                                                                                           |  |  |  |  |

|     |                                                             | Unit: mm                                                                                                                                                                                                                                            |  |  |  |  |

| 8   | Back-light                                                  | <ul><li>(1) The color of backlight should correspond its specification.</li><li>(2) Not allow flickering</li></ul>                                                                                                                                  |  |  |  |  |

| 9   | Soldering                                                   | (1) Not allow heavy dirty and solder ball on PCB.  (The size of dirty refer to point and dust defect)  (2) Over 50% of lead should be soldered on Land.                                                                                             |  |  |  |  |

|     |                                                             | 50% lead                                                                                                                                                                                                                                            |  |  |  |  |

| 10  | Wire                                                        | <ol> <li>(1) Copper wire should not be rusted</li> <li>(2) Not allow crack on copper wire connection.</li> <li>(3) Not allow reversing the position of the flat cable.</li> <li>(4) Not allow exposed copper wire inside the flat cable.</li> </ol> |  |  |  |  |