- Out-of-Stock

Arria V GX FPGA Video Development System

free shipping in Poland for all orders over 500 PLN

If your payment will be credited to our account by 11:00

Each consumer can return the purchased goods within 14 days

Overview

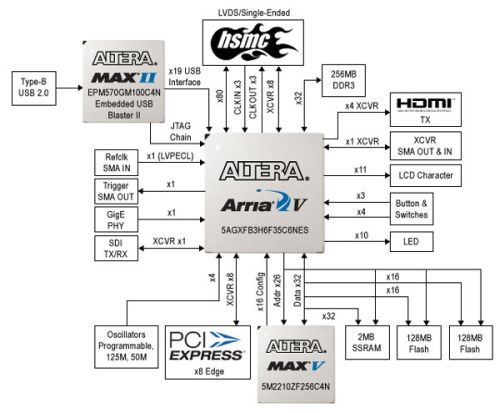

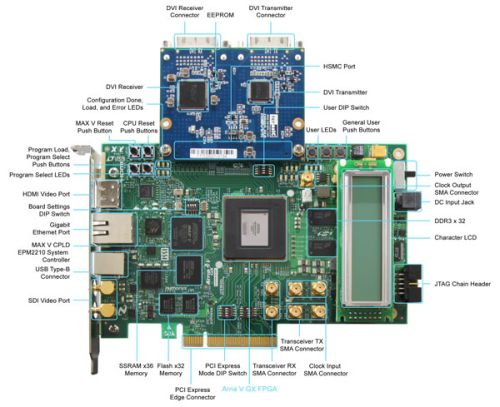

The Arria V GX FPGA Video Development System is an ideal video processing platform for high-performance, cost-effective video applications. The Arria II development kit features 256MB of SDRAM memory, HDMI, and SDI connections to form a perfect solution for imaging applications.

The DVI-HSMC daughter card part of the bundled package will allow developers to access high quality and high resolution video signals that can support resolution up to 1600x1200. A complete DVI video controller design with source code is provided.

Terasic recognized for its strong design expertise in high-end video, imaging and multimedia products have made available a video development package that targets video processing development. The platform can also allow users to experience advanced image processing designs incorporating VIP (Altera’s Video and Image Processing Suite MegaCore Functions).

Specification

Altera Arria V GX Video Development System

Terasic DVI-HSMC Card

Layout

Resources

Demo

DVI Video Development System Bundle

The Terasic DVI Development System bundles together the DVI daughter card and Altera development kit for cost-effective video development. All source code shown is included.

Code: K0111

No product available!

No product available!

No product available!

Freescale i.MX6 Quad, 1GHz, ARM Cortex-A9 Quad Core Processor, RAM 2 GB, Ethernet, HDMI, USB, Wi-Fi, Bluetooth RoHS

No product available!

No product available!

No product available!

No product available!

No product available!

Bitscope Micro is a miniature measuring instrument with a USB interface, it can act as an 8-channel logic analyzer (40MS / s, 3.3V or 5V) or a 2-channel oscilloscope (bandwidth up to 20MHz). In addition, Bitscope can generate a clock signal as well as sinusoidal, triangular, rectangular and saws

No product available!

No product available!

DevKit1207 Evaluation Kit including 3.5"LCD with touch panel (STM32F207IGT6)

No product available!

No product available!

No product available!

No product available!

No product available!

No product available!

Arria V GX FPGA Video Development System