TerasIC USB Blaster Download Cable (UBT) to w pełni zgodny z Altera USB Blaster programator JTAG/ISP dla układów CPLD i FPGA. Dzięki niezawodnej konstrukcji oraz odporności na zakłócenia stanowi uniwersalne narzędzie dla projektantów pracujących z układami programowalnymi Altera. TerasIC P0302

Lista produktów marki Terasic

Terasic – lider w technologii FPGA i układów programowalnych

Terasic to renomowany producent sprzętu komputerowego, specjalizujący się w rozwiązaniach opartych na FPGA (Field-Programmable Gate Array). Firma dostarcza wydajne platformy deweloperskie, moduły rozszerzeń, akceleratory obliczeniowe oraz rozwiązania dostosowane do zastosowań przemysłowych i edukacyjnych. Dzięki wieloletniej współpracy z Intel (dawniej Altera), Analog Devices oraz Micron Technology, produkty Terasic wykorzystywane są w zaawansowanych aplikacjach, takich jak sztuczna inteligencja, przetwarzanie sygnałów, automatyka przemysłowa oraz systemy wbudowane.

Dzięki szerokiej gamie produktów oraz kompleksowemu wsparciu technicznemu, rozwiązania Terasic znajdują zastosowanie zarówno w badaniach naukowych i edukacji, jak i w przemyśle oraz sektorze finansowym, gdzie FPGA pełnią kluczową rolę w handlu wysokiej częstotliwości (HFT).

Liczba produktów: 93

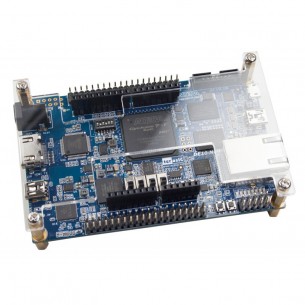

Zestaw startowy DE10-Nano Kit z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. Terasic P0496

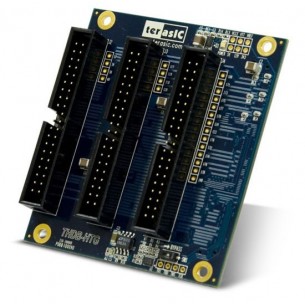

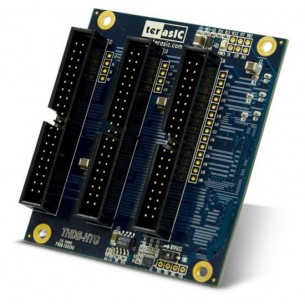

Karta HTG-M przeznaczona jest dla zestawów ewaluacyjnych z układami FPGA, które zostały wyposażone w złącze HSMC (High-Speed Mezzanine connector) lub HSTC (High-Speed Terasic Connector). Karta HTG posiada trzy złącza żeńskie (40-pinowe). Pozwala na konwersje wejść/wyjść HSMC do dwóch 40-pinowych złącz prototypowych lub złącza HSTC do trzech 40-pinowych złącz prototypowych. TerasIC P0024

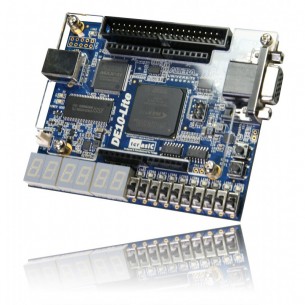

Terasic DE10-Lite Board to niskobudżetowa płytka deweloperska z układem FPGA Altera MAX 10. Płyta zawiera szereg komponentów umożliwiających naukę oraz tworzenie prototypów projektów opartych o układy FPGA

Terasic DE10-Lite Board to niskobudżetowa płytka deweloperska z układem FPGA Altera MAX 10. Płyta zawiera szereg komponentów umożliwiających naukę oraz tworzenie prototypów projektów opartych o układy FPGA. Terasic P0466

Wszechstronna i niezwykle popularna platforma do nauki oraz rozwoju projektów opartych o architekturę ARM + FPGA. Dzięki bogatemu wyposażeniu, dużej ilości pamięci, licznym interfejsom oraz wsparciu narzędzi firmy Intel/Altera, płytka doskonale sprawdzi się w edukacji akademickiej, badaniach naukowych oraz prototypowaniu zaawansowanych systemów wbudowanych i multimedialnych. To idealny wybór dla studentów, inżynierów i hobbystów chcących poznać pełne możliwości systemów SoC.DE1-SoC Development Kit

Platforma ewaluacyjna oparta na układzie FPGA Agilex™ 3, przeznaczona do pracy z procesorem RISC-V Nios® V firmy Altera. Zestaw umożliwia szybkie prototypowanie i naukę systemów wbudowanych dzięki gotowym przykładom oraz wbudowanemu programatorowi USB Blaster III. Oferuje interfejsy takie jak Gigabit Ethernet, HDMI, UART, microSD oraz liczne złącza GPIO i PMOD. TerasIC P0831

Płytka rozwojowa Terasic DE25-Nano z układem FPGA Agilex™ 5 i systemem HPS ARM Cortex-A76/A55 stanowi nowoczesną platformę dla aplikacji AI, przetwarzania wizyjnego i systemów wbudowanych. Bogaty zestaw interfejsów oraz pamięci, aktywne chłodzenie i kompaktowe wymiary pozwalają na wykorzystanie zarówno w prototypowaniu, jak i docelowych rozwiązaniach przemysłowych.

Kompaktowa i wydajna platforma FPGA oparta na układzie Altera Agilex 3 A3CZ135BB18AE7S, oferująca 135 110 elementów logicznych oraz pamięć M20K i MLAB do realizacji zaawansowanych projektów cyfrowych. Płytka wyposażona jest w 64 MB SDRAM, slot MicroSD, wyjście HDMI, port Gigabit Ethernet oraz wbudowany programator USB-Blaster III z USB-C, co umożliwia szybkie prototypowanie i debugowanie. Dzięki rozbudowanym wejściom/wyjściom, w tym GPIO, diodom LED, przełącznikom i złączom PMOD, Atum A3 Nano sprawdzi się w robotyce, elektronice konsumenckiej i przetwarzaniu obrazu. Platforma jest gotowa do pracy po podłączeniu zasilania 5 V, a do zestawu dołączono bezpłatną licencję oprogramowania Altera Quartus Pro Edition. Terasic Atum A3 Nano

[CENA EDUKACYJNA] Zestaw startowy/ewaluacyjny Terasic DE0-Nano Board dla układów FPGA Cyclone IV firmy Altera. Jeden z najmniejszych i najprostszych zestawów startowych dla układów FPGA, wyposażony w podstawowe peryferia, w tym programator-konfigurator JTAG.Obniżona cena (w stosunku do klasycznej wersji Terasic DE0-Nano) dotyczy wyłącznie szkół, uczelni, wykładowców, uczniów i studentów. P0082

Terasic DE1-SoC-MTL2 to rozbudowana i sprawdzona platforma dla inżynierów, studentów i zespołów R&D, którzy potrzebują wydajnego SoC FPGA z dotykowym interfejsem graficznym. Idealna do projektów, w których liczy się połączenie elastyczności FPGA z wygodą systemu Linux i nowoczesnym HMI.

Karta HTG-M przeznaczona jest dla zestawów ewaluacyjnych z układami FPGA, które zostały wyposażone w złącze HSMC (High-Speed Mezzanine connector) lub HSTC (High-Speed Terasic Connector). Karta HTG posiada trzy złącza męskie (40-pinowe). Pozwala na konwersje wejść/wyjść HSMC do dwóch 40-pinowych złącz prototypowych lub złącza HSTC do trzech 40-pinowych złącz prototypowych. TerasIC P0033

Wyświetlacz LCD alfanumeryczny 2x16 bez podświetlenia przeznaczony do zestawów firmy TerasIC (DE0, DE1, DE2 , DE2 -115). P0075

Adapter przeznaczony do łączenia płytek ze złączem PCIe z komputerem. Może obsługiwać interfejs PCIe Gen3 x4. Terasic P0492

Terasic Spider to sześcionożny robot kroczący z 18 serwomechanizmami sterowanymi przez płytkę Altera DE0-Nano-SoC łączącą układ FPGA oraz procesor ARM Cortex-A9. Zestaw zawiera złożonego robota oraz liczne akcesoria. P0425

Płytka TerasIC C5G (P0150) umożliwia rozwój zaawansowanych aplikacji FPGA wymagających wysokiej przepustowości i elastycznej komunikacji. Płytka sprawdza się w projektach badawczo-rozwojowych, telekomunikacyjnych i przemysłowych, gdzie istotne pozostają wydajność, dostęp do szybkich interfejsów oraz kompatybilność z narzędziami projektowymi Cyclone V.

Sterownik serwomechanizmów do zestawów FPGA TerasIC serii DE umożliwia sterowanie maksymalnie 24 serwomechanizmami. Dostarcza napięcie 6 V do zasilania serwomechanizmów. W zestawie serwomechanizm MG966R i taśma do połączenia z zestawem FPGA. P0288

TerasIC SDI HSMC to specjalistyczny moduł dla projektów FPGA w obszarze transmisji wideo, oferujący wsparcie dla standardów SDI i AES oraz pełną kompatybilność z platformami HSMC. Idealny do rozwoju rozwiązań nadawczych, analizatorów sygnału i profesjonalnych aplikacji wideo.

Terasic HDMI-FMC to karta rozszerzająca układy ewaluacyjny o możliwość wyświetlania oraz odbierania obrazu wideo przy pomocy złącz HDMI. Pozwalają wyświetlać obraz w rozdzielczości 4K@30FPS. Wspiera HDMI 1.4a. Terasic P0431

TerasIC LT24 to moduł z wyświetlaczem LCD 2,4-calowym o rozdzielczości 320 x 240 pikseli. Wyświetlacz wyposażony jest w panel dotykowy rezystancyjny. Wyświetlacz przeznaczony jest do użycia z zestawami uruchomieniowymi TerasIC ze złączem GPIO 2x20. P0185

Zestawy deweloperskie Terasic – elastyczność i wszechstronność

Jednym z kluczowych segmentów oferty Terasic są zestawy deweloperskie FPGA, które umożliwiają szybkie prototypowanie oraz testowanie nowych technologii cyfrowych. Do najczęściej stosowanych należą seria DE (np. DE10-Nano, DE1-SoC), Cyclone V, Stratix oraz Arria, które oferują wysoką moc obliczeniową oraz szeroką gamę interfejsów komunikacyjnych.

Płytki Terasic wyposażone są w porty HDMI, USB, Ethernet, GPIO oraz PCIe, co umożliwia ich wykorzystanie w różnorodnych projektach. Dzięki pełnej kompatybilności z popularnym środowiskiem Intel Quartus Prime, użytkownicy mogą tworzyć własne układy cyfrowe, testować algorytmy oraz rozwijać oprogramowanie dla systemów wbudowanych.

Moduły rozszerzeń i akceleratory FPGA – zwiększona moc obliczeniowa

Dla użytkowników poszukujących rozszerzonej funkcjonalności systemów FPGA, Terasic oferuje szeroki wybór modułów dodatkowych, takich jak przetworniki sygnałów, układy komunikacyjne, sensory oraz karty do akceleracji obliczeniowej.

W ofercie dostępne są również wydajne karty akceleracyjne PCIe, które umożliwiają zastosowanie FPGA w sztucznej inteligencji, analizie danych oraz przetwarzaniu obrazu i sygnałów. Wysoka przepustowość interfejsu PCI Express pozwala na błyskawiczne przetwarzanie dużych ilości danych, co jest kluczowe w aplikacjach wymagających minimalnych opóźnień.

Zestaw edukacyjny Terasic – idealne rozwiązanie dla uczelni i instytutów badawczych

Produkty Terasic są szeroko stosowane w edukacji i badaniach naukowych, gdzie umożliwiają naukę i rozwój systemów FPGA oraz architektury układów programowalnych. Dzięki łatwo dostępnej dokumentacji, wsparciu dla środowisk programistycznych oraz licznym przykładom kodu, zestawy tej marki pomagają w nauce przetwarzania sygnałów, sterowania systemami wbudowanymi oraz projektowania układów cyfrowych.

Dostępny w ofercie zestaw edukacyjny umożliwia studentom oraz inżynierom szybkie opanowanie podstaw FPGA oraz rozwój bardziej skomplikowanych projektów, dostosowanych do potrzeb nowoczesnych technologii.

Przemysłowe zastosowania Terasic – wydajność i niezawodność

Platformy Terasic wykorzystywane są nie tylko w edukacji, ale także w przemyśle i sektorze badawczym, gdzie FPGA pełnią kluczową rolę w systemach sterowania, automatyce przemysłowej, radarach oraz przetwarzaniu obrazu.

Dzięki wysokiej niezawodności i odporności na trudne warunki pracy, układy FPGA Terasic znajdują zastosowanie w takich dziedzinach jak lotnictwo, telekomunikacja oraz sektor energetyczny, gdzie wymagana jest duża moc obliczeniowa i minimalne opóźnienia.

Terasic – innowacja i zaawansowana technologia dla inżynierów

Dzięki wieloletniemu doświadczeniu oraz zaawansowanej technologii FPGA, Terasic stał się zaufanym partnerem dla inżynierów, naukowców i firm technologicznych na całym świecie. Bogata oferta zestawów deweloperskich, modułów rozszerzeń oraz kart akceleracyjnych sprawia, że produkty tej marki są niezastąpionym elementem nowoczesnych systemów opartych na układach programowalnych.

Niezależnie od tego, czy chodzi o sztuczną inteligencję, przetwarzanie sygnałów, systemy wbudowane czy sterowanie przemysłowe, Terasic dostarcza rozwiązania, które umożliwiają realizację najbardziej zaawansowanych projektów FPGA.