1 671,42 zł Netto

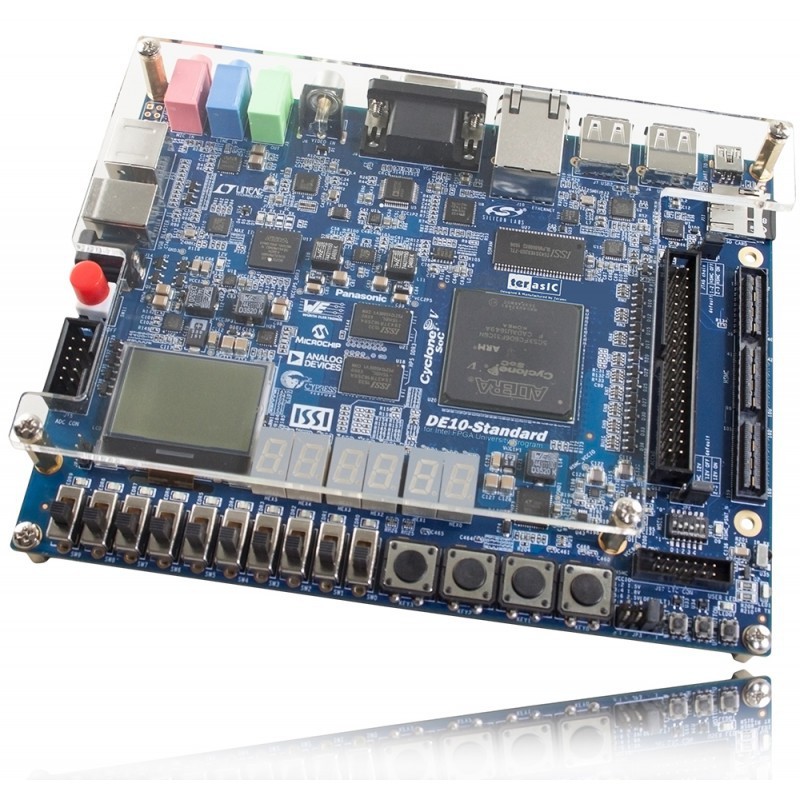

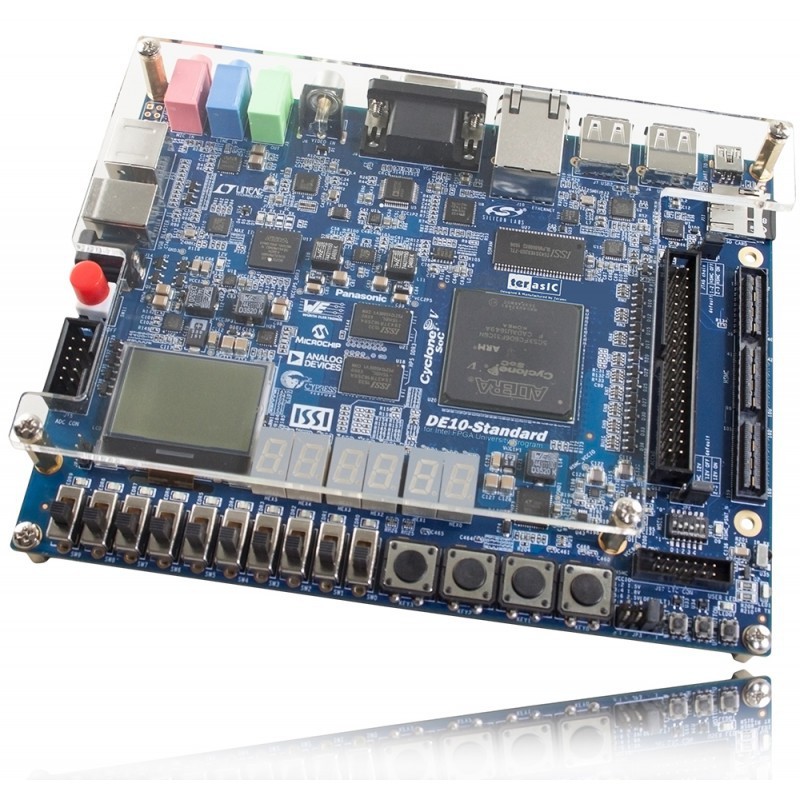

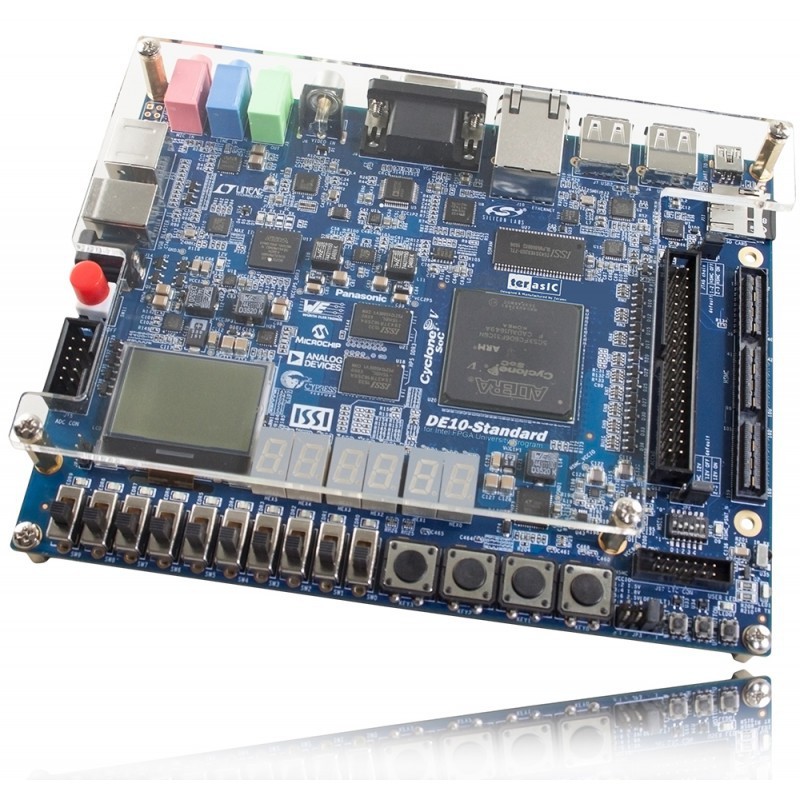

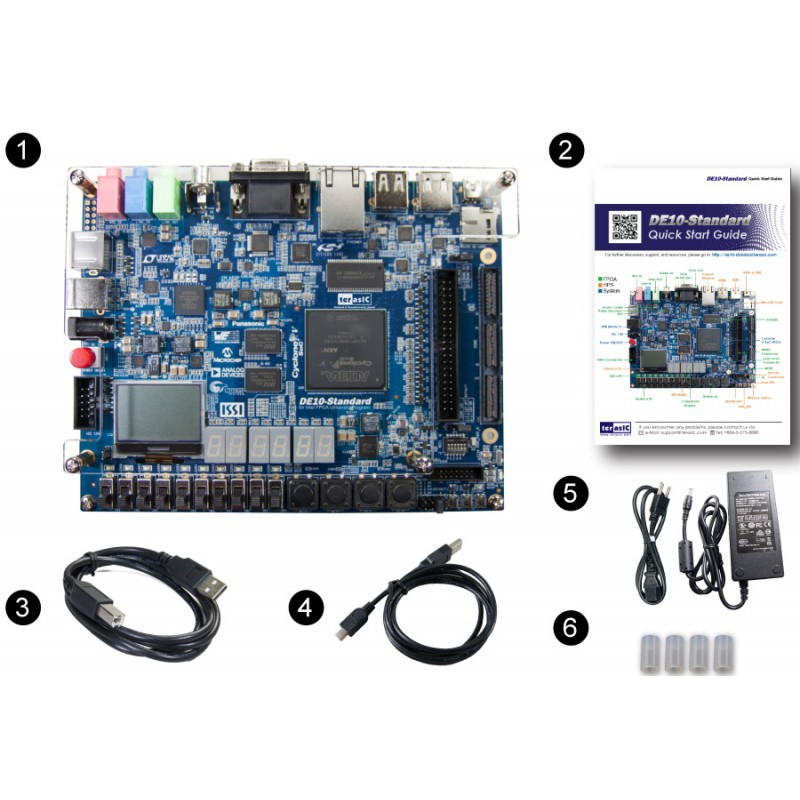

Zestaw startowy DE10-Standard z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. P0493

Oferta przeznaczona wyłącznie dla odbiorców akademickich (studentów i wykładowców wyższych uczelni)!

Składając zamówienie należy podać:

- imię i nazwisko użytkownika

- stanowisko

- adres e-mail użytkownika (adres e-mail musi być z domeny uczelni)

- pełną nazwę uczelni

- nazwę wydziału/instytutu/zakładu dydaktycznego

- adres uczelni

- stronę internetową uczelni

- telefon

- zastosowanie produktu

W uzasadnionych przypadkach zastrzegamy sobie prawo do odmowy zrealizowania zamówienia z oferty akademickiej.

Wszelkie zapytania można kierować na adres: sprzedaz@kamami.pl.

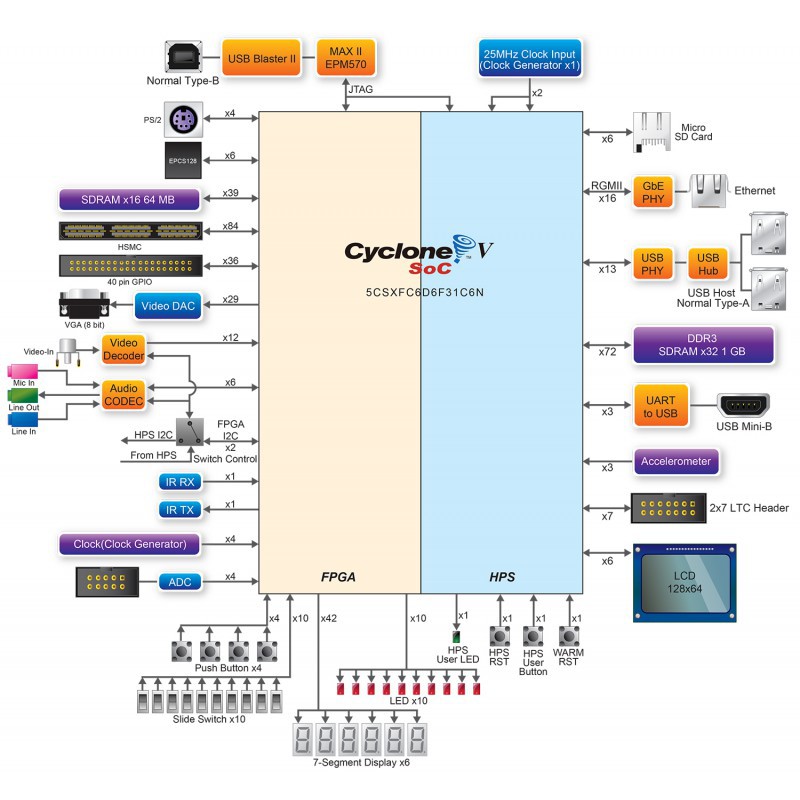

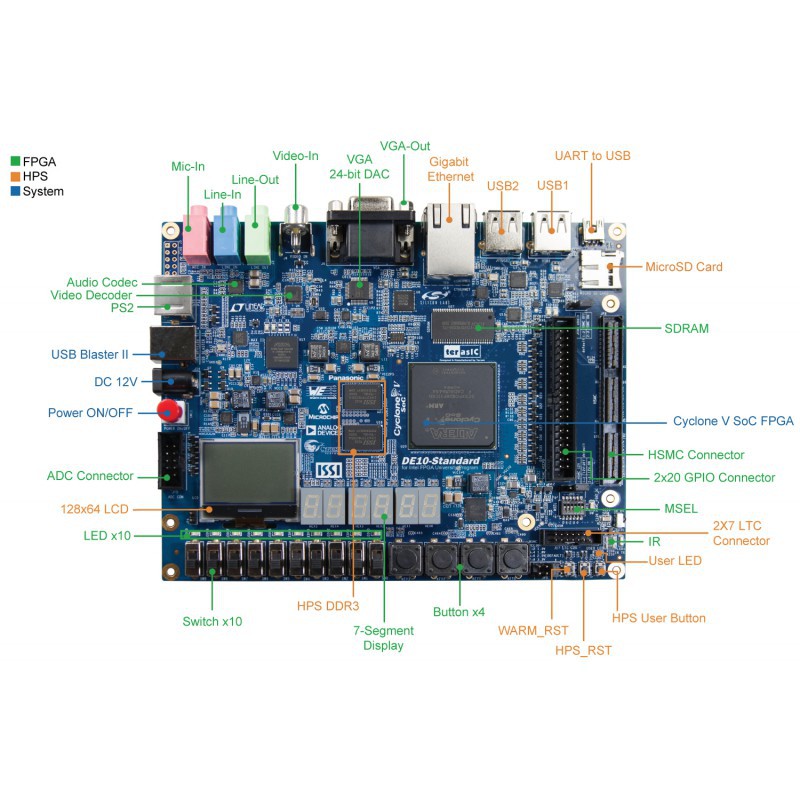

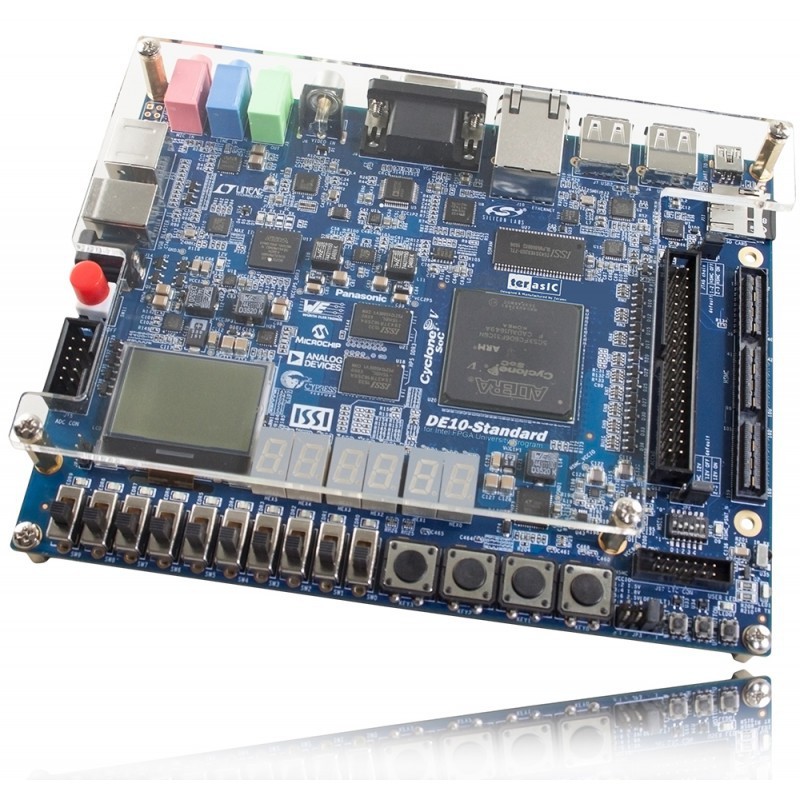

Terasic DE10-Standard to płytka deweloperska oparta na układzie Cyclone® V SE5CSXFC6D6F31C6N Zawiera ona układ programowalny FPGA, który ma 110 tyś elementów logicznych, oraz procesor oparty na architekturze ARM Cortex-A9 o częstotliwości pracy 925 MHz. Płytka dzięki wielu komponentom, jakimi są liczne diody LED, przyciski monostabilne, przełączniki suwakowe, USB-Blaster, SDRAM, akcelerometr, wyjście VGA oraz listwa wejść i wyjść cyfrowych, to idealne narzędzie do nauki programowania układów FPGA. Płytka również idealnie nada się do prototypowania projektów związanych z tą tematyką.

Zestaw DE10-Standard zawiera wiele przykładowych projektów oraz praca z nim pozwala na użycie wielu narzędzi programowych dla użytkowników. Wszystko to po to, aby łatwo rozwijać swoje aplikacje oparte właśnie na układach FPGA.

Producent BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Terasic DE10-Lite Board to niskobudżetowa płytka deweloperska z układem FPGA Altera MAX 10. Płyta zawiera szereg komponentów umożliwiających naukę oraz tworzenie prototypów projektów opartych o układy FPGA

Zestaw startowy DE10-Standard z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. P0493

Brak towaru

Zestaw startowy DE10-Nano Kit z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. Terasic P0496

Płyta bazowa FPGA z układem FPGA z rodziny MAX10 z 7", 5-punktowym wyświetlaczem multidotykowym. Oparty na układzie 10M50DAF484C6G. 512 Mb pamięci Flash, gniazdo miroSD, wejście Audio, Video, zasilanie 5 V/3 A.

Brak towaru

Terasic Spider to sześcionożny robot kroczący z 18 serwomechanizmami sterowanymi przez płytkę Altera DE0-Nano-SoC łączącą układ FPGA oraz procesor ARM Cortex-A9. Zestaw zawiera złożonego robota oraz liczne akcesoria. P0425

A-Cute Car Robotic Kit to kompletne 3-kołowe podwozie robota mobilnego wraz ze sterownikiem opartym o układ FPGA do samodzielnego programowania. P0467

Brak towaru

Terasic DE10-Lite Board to niskobudżetowa płytka deweloperska z układem FPGA Altera MAX 10. Płyta zawiera szereg komponentów umożliwiających naukę oraz tworzenie prototypów projektów opartych o układy FPGA. Terasic P0466

Terasic DE10-Lite Board to niskobudżetowa płytka deweloperska z układem FPGA Altera MAX 10. Płyta zawiera szereg komponentów umożliwiających naukę oraz tworzenie prototypów projektów opartych o układy FPGA

Sterownik serwomechanizmów do zestawów FPGA TerasIC serii DE umożliwia sterowanie maksymalnie 24 serwomechanizmami. Dostarcza napięcie 6 V do zasilania serwomechanizmów. W zestawie serwomechanizm MG966R i taśma do połączenia z zestawem FPGA. P0288

Moduł z kamerą przeznaczony do użycia z zestawami Terasic. Kamera posiada przetwornik o rozdzielczości 8 Megapikseli (3264 x 2448), do komunikacji wykorzystuje interfejs MIPI. Na module znalazł się również dekoder MIPI oraz układ HDMI-TX. Terasic P0449

Brak towaru

Zestaw startowy VEEK-MT2-C5SoC z układem System-on-Chip z rodziny Cyclone V SX SoC. W zestawie 7-calowy wyświetlacz, 8 megapikselową kamerę z autofocusem, czujnik światła, żyroskop, magnetometr oraz 3 osiowy akcelerometr. Terasic K0160

Brak towaru

Terasic ADC-SoC to płyta rozwojowa z układem programowalnym FPGA oraz dwukanałowym szybkim przetwornikiem ADC. Płyta bazuje na module Terasic DE0-Nano-SoC. Wbudowany przetwornik ADC wykorzystuje SMA jako interfejs wejściowy, posiada dwa kanały, oferuje rozdzielczość 14-bitową, i szybkość próbkowania do 150 MSPS Megasamples per Second). Terasic (P0435)

Brak towaru

Zestaw elementów przeznaczony dla zestawów ewaluacyjnych z układami programowalnymi z rodziny Cyclone V SoC FPGA, w którego skład wchodzą; 7-calowy wyświetlacz TFT z obsługą dotyku (5-punktów), 8 megapikselowa kamera z autofocusem oraz czujniki (światła, akcelerometr, żyroskop, magnetometr). Terasic P0494

Brak towaru

Terasic HDMI-FMC to karta rozszerzająca układy ewaluacyjny o możliwość wyświetlania oraz odbierania obrazu wideo przy pomocy złącz HDMI. Pozwalają wyświetlać obraz w rozdzielczości 4K@30FPS. Wspiera HDMI 1.4a. Terasic P0431

Terasic NET-FMC to karta rozszerzająca z Gigabajtowym Ethernetem oraz interfejsem FMC. Dzięki temu interfejsowi może być używana z zestawami firmy Terasic. Terasic P0481

Brak towaru

Zestaw startowy DE10-Standard z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. P0493

Zestaw startowy DE10-Standard z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. P0493

Brak towaru

Zestaw startowy DE10-Nano Kit z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. Terasic P0496

Brak towaru

Zestaw startowy DE10-Nano Kit z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. Terasic P0496

Zestaw startowy DE10-Standard z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. P0493