Terasic DE1-SoC-MTL2 (K0159) - DE1-SoC + 5 points multitouch display MTL2

Overview

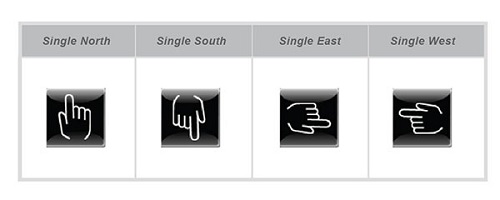

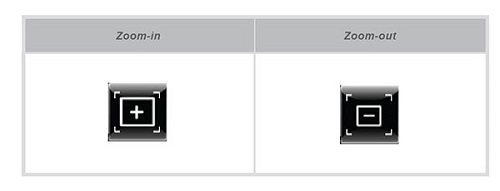

The DE1-SoC-MTL2 Development Kit is a comprehensive design environment with everything embedded developers need to create processing-based systems. The DE1-SoC-MTL2 delivers an integrated platform including hardware, design tools, and reference designs for developing embedded software and hardware platforms in a wide range of applications. The fully integrated kit allows developers to rapidly customize their processor and IP to best suit their specific application. The DE1-SoC-MTL2 features a DE1-SoC development board targeting Altera Cyclone® V SX SoC FPGA, as well as a capacitive LCD multimedia color touch panel which natively supports five points multi-touch and gestures.

The all-in-one embedded solution offered on the DE1-SoC-MTL2, in combination of a LCD touch panel and digital image module, provide s embedded developers the ideal platform for multimedia applications with unparallel processing performance. Developers can benefit from the use of FPGA-based embedded processing system such as mitigat ing design risk and obsolescence, design reuse, lowering bill of material (BOM) costs by integrating powerful graphics engines within the FPGA.

For SoC reference design in Linux for touch-screen display, please refer to the DE1-SoC-MTL2 Control Panel .

Specification

Layout

Demo

Kit Contents

Download

Producent BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. TerasIC T-Core P0633

Brak towaru

Platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. Wersja edukacyjna. TerasIC T-Core P0633

Brak towaru

Kompaktowy zestaw FPGA z układem Intel Arria 10 GX wyposażony w 8 GB pamięci DDR4-2133 oraz złącze komunikacyjne Thunderbolt 3. Może być zastosowany bezpośrednio na laptopach lub innych urządzeniach przenośnych. Terasic FLIK P0642

Brak towaru

Kompaktowy zestaw FPGA z układem Intel Arria 10 GX wyposażony w 8 GB pamięci DDR4-2133 oraz złącze komunikacyjne Thunderbolt 3. Może być zastosowany bezpośrednio na laptopach lub innych urządzeniach przenośnych. Wersja edukacyjna. Terasic FLIK P0642

Brak towaru

Moduł ewaluacyjny z procesorem Intel Stratix 10 SoC z elementami logicznymi 2800K. Moduł posiada pamięć DDR4 SDRAM (do 64 GB), wbudowany USB-Blaster II, Ethernet, microSD, miniUSB oraz złącza FMC/FMC+ do rozbudowy. TerasIC Apollo S10 SoM Board (P0630)

Brak towaru

Zestaw deweloperski z modułem Apollo S10 oraz płytą bazową. Wyposażony w procesor Intel Stratix 10 SoC z elementami logicznymi 2800K, posiada pamięć DDR4 SDRAM (do 64 GB), wbudowany USB-Blaster II, Ethernet, microSD, miniUSB oraz złącza QSFP i USB typ C. TerasIC Apollo Developer Kit (P0671)

Brak towaru

Zestaw startowy FPGA z układem Intel Stratix 10 SX. Moduł posiada zintegrowane urządzenia nadawczo-odbiorcze, które przesyłają dane z prędkością do 28,3 Gb/s, dzięki czemu DE10-Pro jest w pełni zgodny z wersją 3.0 standardu PCI Express. DE10-Pro oferuje szybką pamięć równoległą Flash i cztery pamięci SO-DIMM, które mają 4 GB DDR4 SDRAM. Terasic P0627

Brak towaru

Zestaw startowy FPGA z układem Intel Stratix 10 SX. Moduł posiada zintegrowane urządzenia nadawczo-odbiorcze, które przesyłają dane z prędkością do 28,3 Gb/s, dzięki czemu DE10-Pro jest w pełni zgodny z wersją 3.0 standardu PCI Express. DE10-Pro oferuje szybką pamięć równoległą Flash i cztery pamięci SO-DIMM, które mają 8 GB DDR4 SDRAM. Terasic P0629

Brak towaru

Zestaw z płytką FPGA Terasic DE10-Nano oraz modułem WiFi. Przeznaczony do projektów wykorzystujących FPGA do pracy w chmurze. TerasIC P0700

Brak towaru

Płytka ewaluacyjna z układem Intel Agilex SoC z 1400 tys. elementów logicznych. Moduł ma dwa gniazda pamięci DDR4 SO-DIMM (do 32 GB), złącze QSFP28, PCIe Gen 4x16, wbudowany USB-Blaster II oraz złącza FMC/FMC+ do rozbudowy. TerasIC Apollo Agilex SOM (P0714)

Brak towaru

Płytka rozwojowa FPGA Altera Cyclone IV EP4CE6E22C8N w zestawie z płytką bazową. Waveshare OpenEP4CE6-C Standard

Brak towaru

Płytka rozwojowa FPGA Altera Cyclone IV EP4CE6E22C8N w zestawie z płytką bazową i modułami rozszerzeń. Waveshare OpenEP4CE6-C Package A

Brak towaru

Płytka rozwojowa FPGA Altera Cyclone IV EP4CE6E22C8N w zestawie z płytką bazową i modułami rozszerzeń. Waveshare OpenEP4CE6-C Package B

Brak towaru

Płytka deweloperska z układem FPGA ALTERA Cyclone IV EP4CE6E22C8N. Waveshare CoreEP4CE6

Brak towaru

Zestaw rozwojowy z układem FPGA Altera MAX10 (10M16DA) z wbudowaną pamięcią Flash i złączami rozszerzeń interfejsu IO. Numato Lab NLFA1001A

Brak towaru

Zestaw rozwojowy z układem FPGA Altera MAX10 (10M50DA) z wbudowaną pamięcią Flash i złączami rozszerzeń interfejsu IO. Numato Lab NLFA1002B

Brak towaru

DE1-SoC + 5 points multitouch display MTL2