- Obecnie brak na stanie

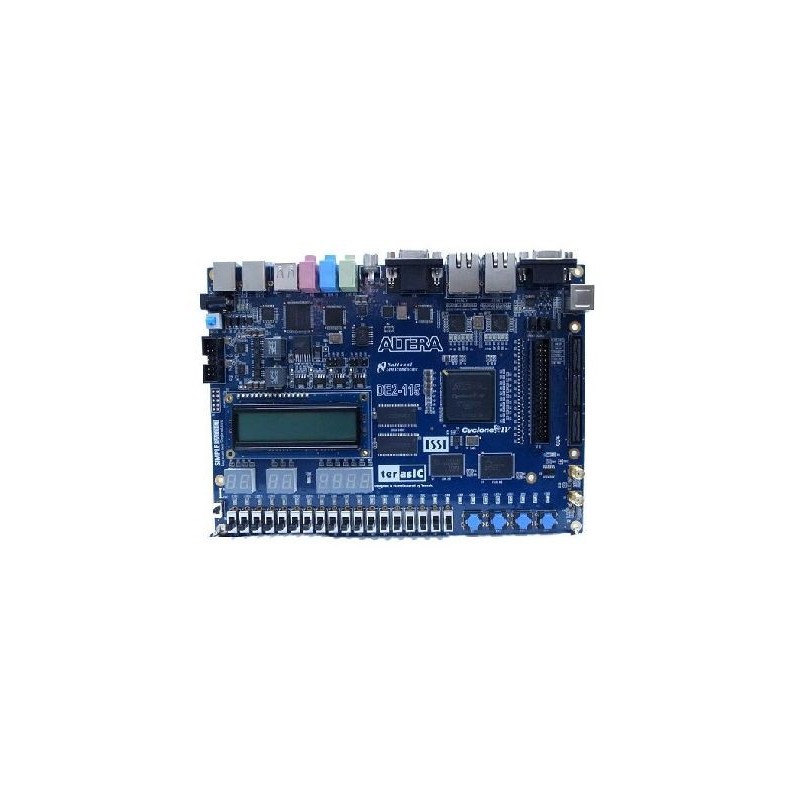

Overview

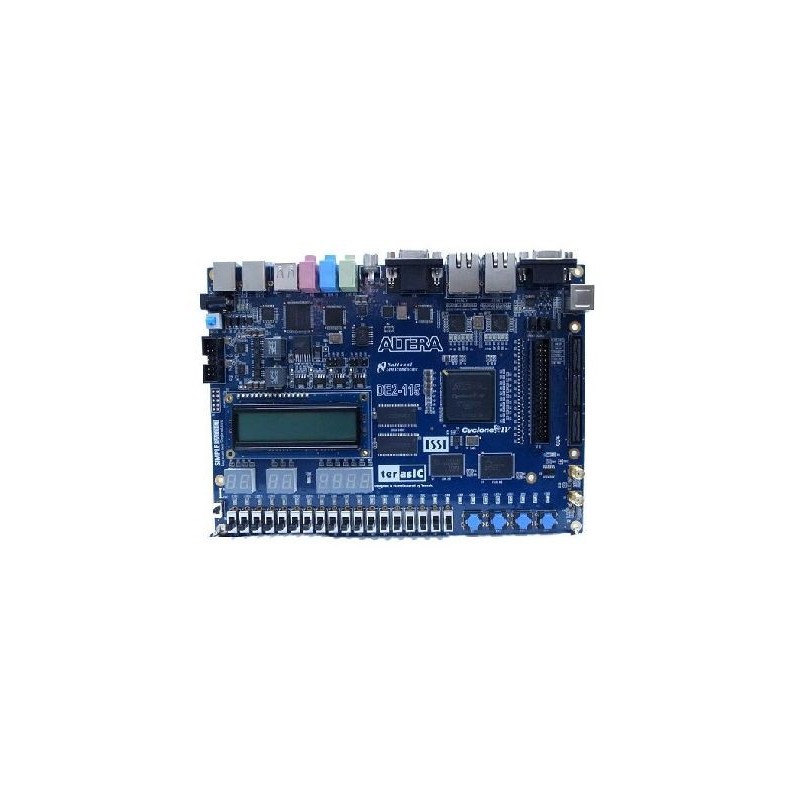

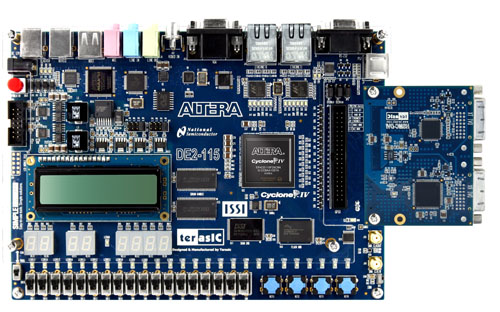

The DE2 series has consistently been at the forefront of educational development boards by distinguishing itself with an abundance of interfaces to accommodate various application needs. Extending its leadership and success, Terasic announces the latest DE2-115 that features the Cyclone IV E device. Responding to increased versatile low-cost spectrum needs driven by the demand for mobile video, voice, data access, and the hunger for high-quality images, the new DE2-115 offers an optimal balance of low cost, low power and a rich supply of logic, memory and DSP capabilities.

The Cyclone EP4CE115 device equipped on the DE2-115 features 114,480 logic elements (LEs), the largest offered in the Cyclone IV E series, up to 3.9-Mbits of RAM, and 266 multipliers. In addition, it delivers an unprecedented combination of low cost and functionality, and lower power compared to previous generation Cyclone devices.

The DE2-115 adopts similar features from the earlier DE2 series primarily the DE2-70, as well as additional interfaces to support mainstream protocols including Gigabit Ethernet (GbE). A High-Speed Mezzanine Card (HSMC) connector is provided to support additional functionality and connectivity via HSMC daughter cards and cables. For large-scale ASIC prototype development, a connection can be made with two or more FPGA-based boards by means of a HSMC cable through the HSMC connector.

Specification

Cyclone® IV EP4CE115

- 114,480 logic elements (LEs)

- 3,888 Embedded memory (Kbits)

- 266 Embedded 18 x 18 multipliers

- 4 General-purpose PLLs

- 528 User I/Os

Configuration Device and USB-Blaster Circuit

- EPCS64 serial configuration device

- On-board USB-Blaster circuitry

- JTAG and AS mode configuration supported

Memory Devices

- 128MB (32Mx32bit) SDRAM

- 2MB (1Mx16) SRAM

- 8MB (4Mx16) Flash with 8-bit mode

- 32Kbit EEPROM

Switches and Indicators

- 18 switches and 4 push-buttons

- 18 red and 9 green LEDs

- Eight 7-segment displays

Audio

- 24-bit encoder/decoder(CODEC)

- line-in, line-out, and microphone-in jacks

Display

- 16x2 LCD module

On-Board Clocking Circuitry

- Three 50MHz oscillator clock inputs

- SMA connectors (external clock input/output)

SD Card Socket

- Provides SPI and 4-bit SD mode for SD Card access

Two Gigabit Ethernet Ports

- Integrated 10/100/1000 Gigabit Ethernet

- Supports Industrial Ethernet IP cores

172-pin High Speed Mezzanine Card (HSMC)

- Configurable I/O standards (voltage levels: 3.3/2.5/1.8/1.5V)

USB Type A and B

- Provide host and device controller compliant with USB 2.0

- Support data transfer at full-speed and low-speed

- PC driver available

40-pin Expansion Port

- Configurable I/O standards (voltage levels: 3.3/2.5/1.8/1.5V)

VGA-out Connector

- VGA DAC (high speed triple DACs)

DB-9 Serial Connector

- RS232 port with flow control

PS/2 Connector

- PS/2 connector for connecting a PS2 mouse or keyboard to the DE2-115

Remote Control

- Infrared receiver module

TV-in Connector

- TV decoder (NTSC/PAL/SECAM)

Power

- Desktop DC input

- Switching and step-down regulators LM3150MH

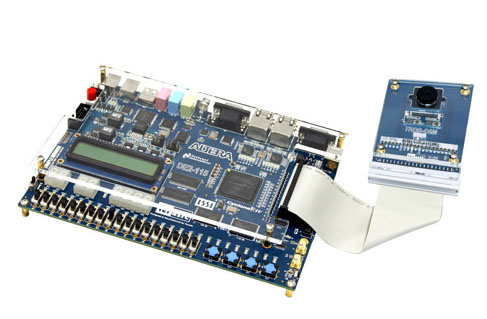

![]() Connect D5M

Connect D5M

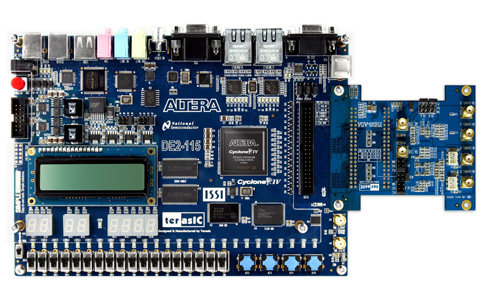

- Connect D5M with DE2-115

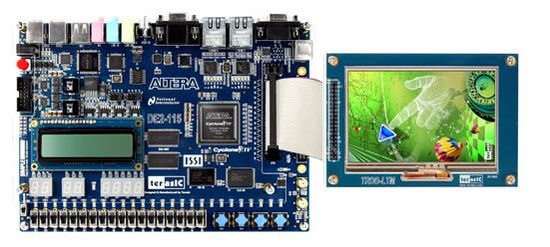

![]() Connect LTM

Connect LTM

- Connect LTM with DE2-115

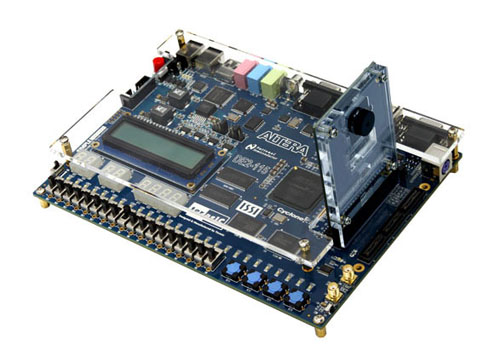

![]() Connect DVI-HSMC

Connect DVI-HSMC

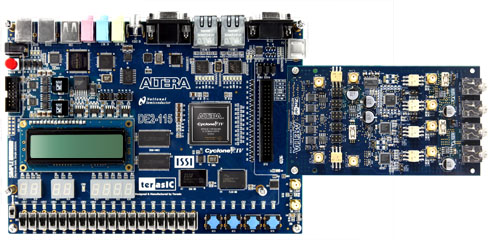

- Connect DVI-HSMC with DE2-115

![]() Connect ADA-HSMC

Connect ADA-HSMC

- Connect ADA-HSMC with DE2-115

![]() Connect DCC-HSMC

Connect DCC-HSMC

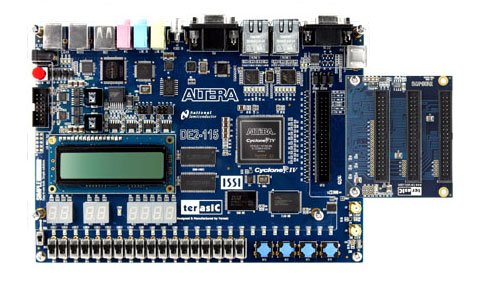

- Connect DCC-HSMC with DE2-115

![]() Connect HTG

Connect HTG

- Connect HTG with DE2-115

Layout

Resources

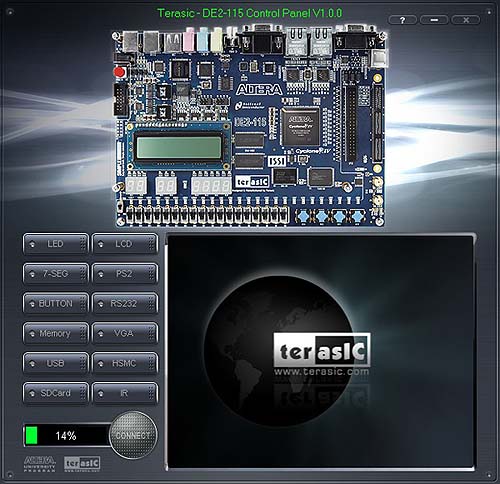

DE2-115 Control Panel – allows users to access various components on the DE2-115 platform from a host computer.

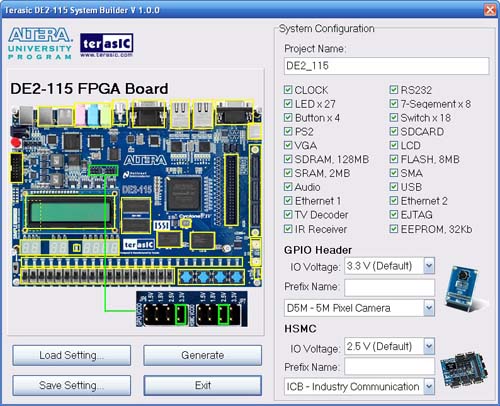

DE2-115 System Builder – a powerful tool that comes with the DE2-115 board. This tool will allow users to create a Quartus II project file on their custom design for the DE2-115 board. The top-level design file, pin assignments, and I/O standard settings for the DE2-115 board will be generated automatically from this tool. In addition, through the HSMC connectors ---> In addition, through the GPIO and HSMC connectors you can select various daughter cards in conjunction with the DE2-115 using the DE2-115 System Builder.

Kit Contents

Code: P0059

Producent BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Karta HTG-M przeznaczona jest dla zestawów ewaluacyjnych z układami FPGA, które zostały wyposażone w złącze HSMC (High-Speed Mezzanine connector) lub HSTC (High-Speed Terasic Connector). Karta HTG posiada trzy złącza męskie (40-pinowe). Pozwala na konwersje wejść/wyjść HSMC do dwóch 40-pinowych złącz prototypowych lub złącza HSTC do trzech 40-pinowych złącz prototypowych. TerasIC P0033

Wyświetlacz LCD alfanumeryczny 2x16 bez podświetlenia przeznaczony do zestawów firmy TerasIC (DE0, DE1, DE2 , DE2 -115). P0075

TerasIC LT24 to moduł z wyświetlaczem LCD 2,4-calowym o rozdzielczości 320 x 240 pikseli. Wyświetlacz wyposażony jest w panel dotykowy rezystancyjny. Wyświetlacz przeznaczony jest do użycia z zestawami uruchomieniowymi TerasIC ze złączem GPIO 2x20. P0185

Zestaw uruchomieniowy dla mikrokontrolerów PIC16F887

Brak towaru

Brak towaru

Brak towaru

Moduł kamery 2 MPx z sensorem OG02B10 współpracujący z wszystkimi wersjami Raspberry Pi. Wyposażony w migawkę, charakteryzuje się dobrą czułością. ArduCAM B0199

Brak towaru

Karta dźwiękowa w formie małego urządzenia z wtykiem USB. Wykorzystuje przetwornik DAC ES9018K2M, wzmacniacz słuchawkowy i ma wyjście audio Jack 3,5 mm

Brak towaru

Brak towaru

Brak towaru

Brak towaru

Moduł z z różnicowym transceiverem I2C pozwalającym na rozszerzenie zasięgu magistrali komunikacyjnej I2C do 30m. Sygnały różnicowe są przesyłane kablem Ethernet, który podłącza się do złącza RJ-45. SparkFun BOB-14589

Brak towaru

Brak towaru

Brak towaru

Brak towaru

Brak towaru

Brak towaru

Brak towaru

Brak towaru

Altera DE2-115 Development and Education Board