1 250,92 zł Netto

darmowa wysyłka na terenie Polski dla wszystkich zamówień powyżej 500 PLN

Jeśli Twoja wpłata zostanie zaksięgowana na naszym koncie do godz. 11:00

Każdy konsument może zwrócić zakupiony towar w ciągu 14 dni bez zbędnych pytań

Overview

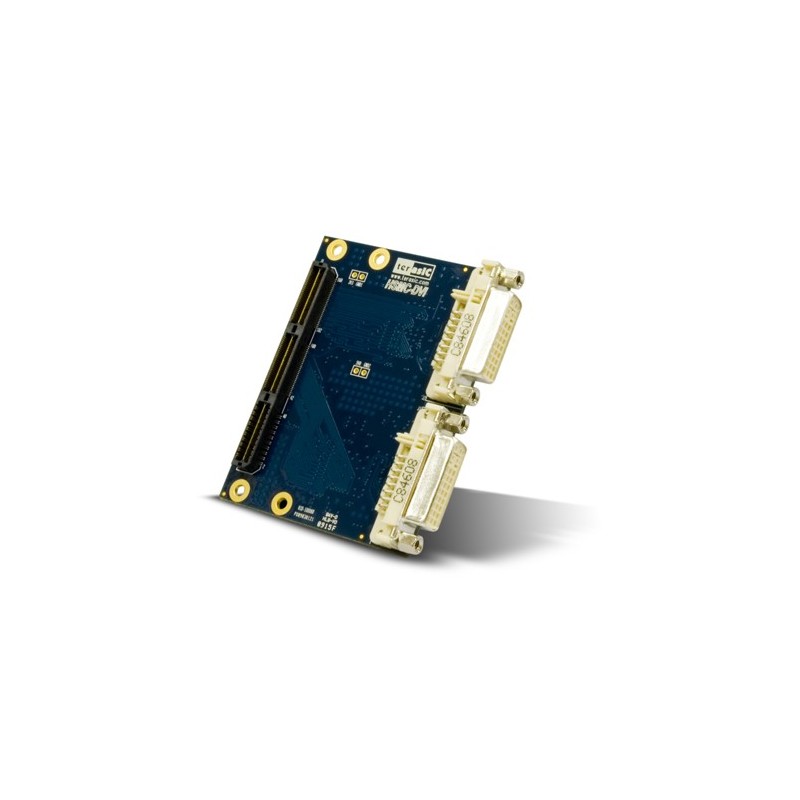

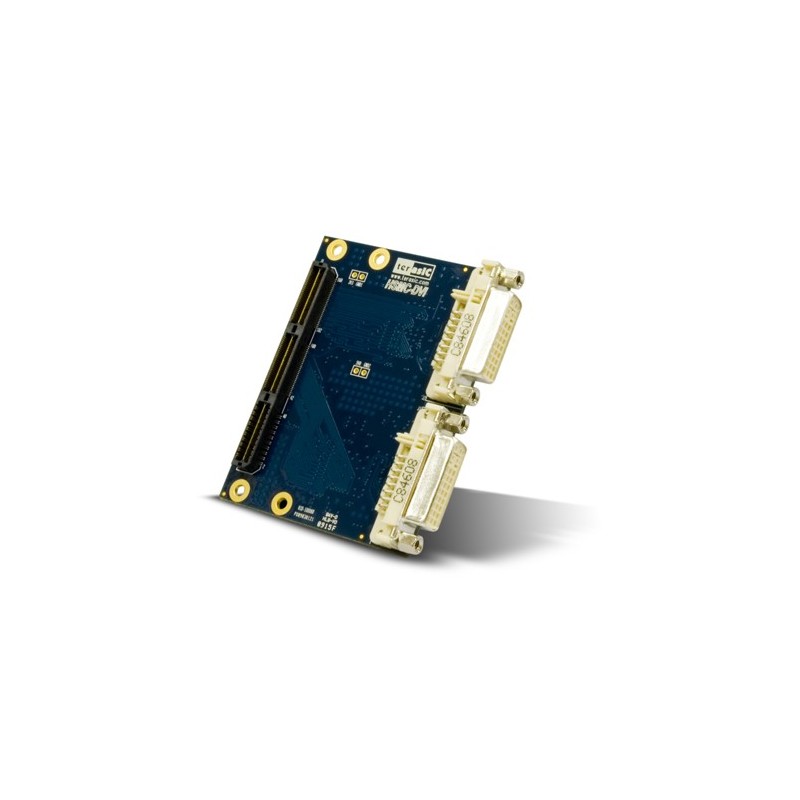

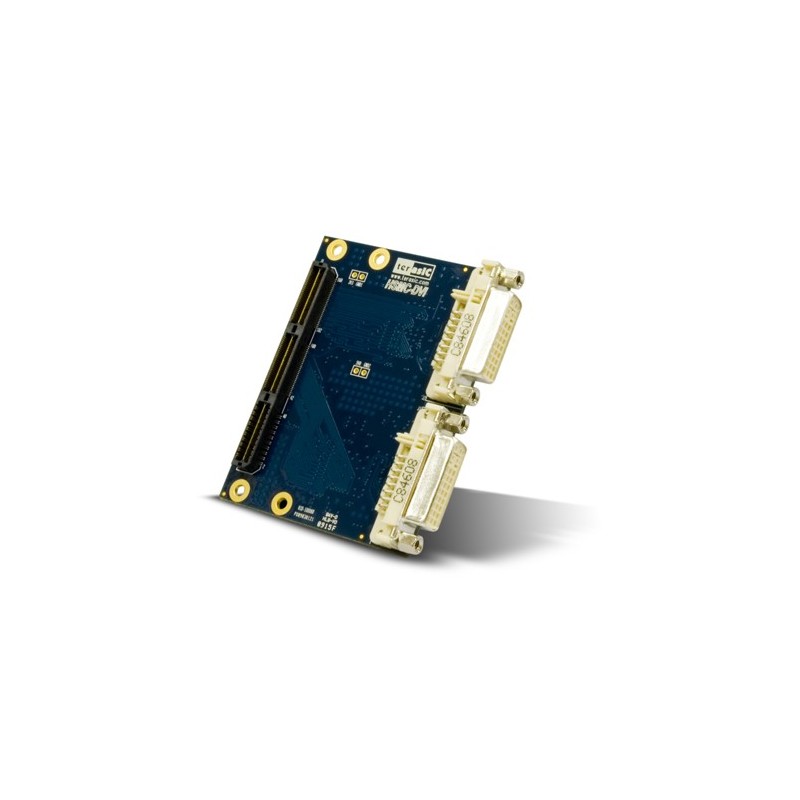

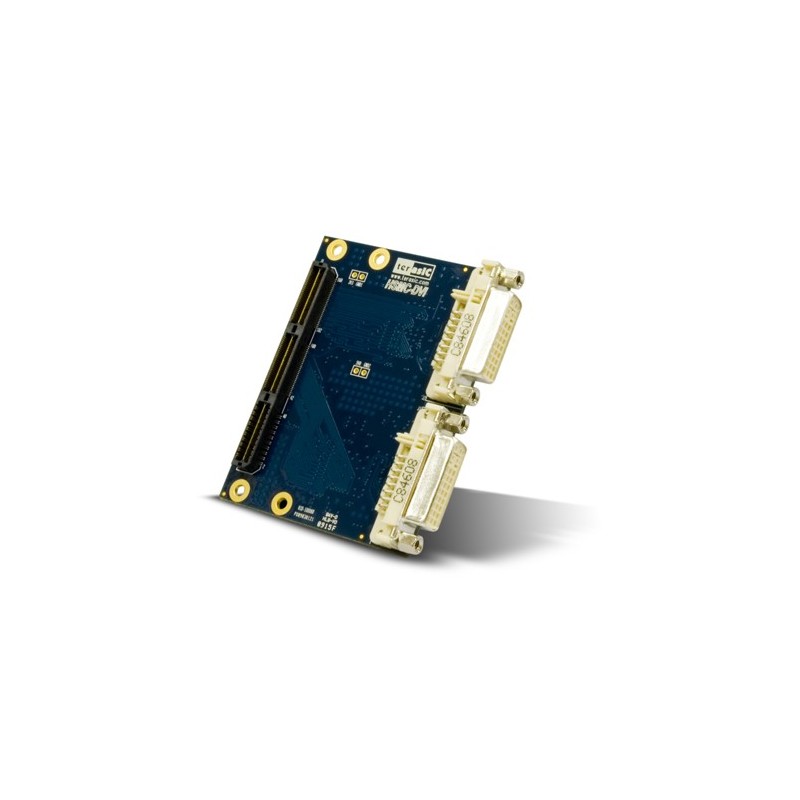

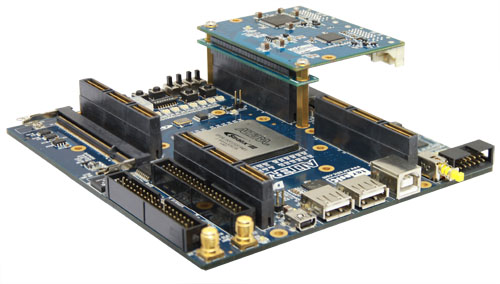

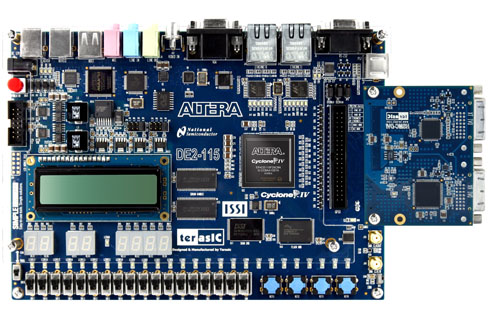

The Terasic DVI-HSMC is a DVI transmitter/receiver board with a High Speed Mezzanine Connector (HSMC) interface. It is designed to allow developers to access high quality and high resolution video signals that support UXGA Resolution (Pixel Rates up to 165 MHz). It gives the flexibility required in high resolution image processing systems by combining both the DVI transmitter and receiver onto the same card. Lastly, the DVI-HSMC daughter board can be connected to any HSMC/HSTC interface host boards.

Specification

![]() DVI-HSMC Card

DVI-HSMC Card

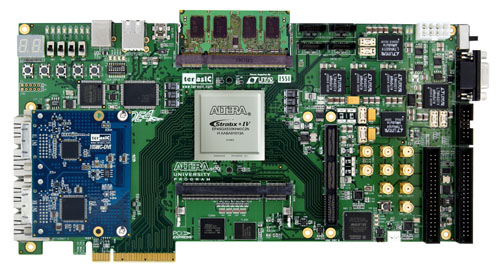

Connect ADA-HSMC with DE3

Note. An adapter (SFF or HFF) is required to connect ADA-HSMC with DE3. It is bundled in DE3 kit.

Resources

Reference Designs

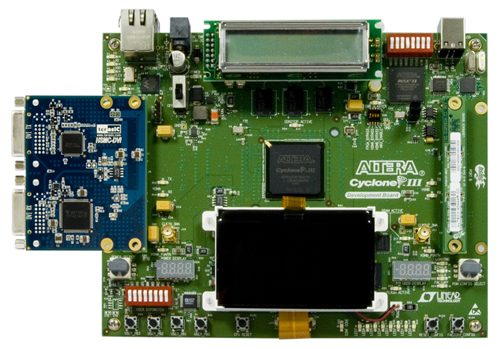

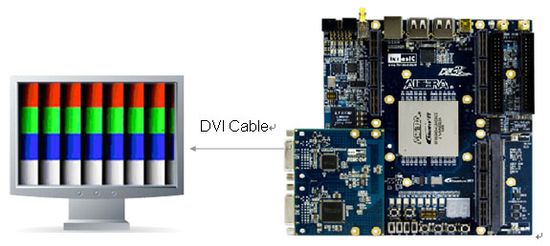

![]() Transmission-Only Demo

Transmission-Only Demo

(Full source code included)

The Transmission demonstration is able to generate various video format signals to the transmit port of the DVI Daughter Board from the associated host boards. (DE3, Cyclone III Starter Board, Cyclone III Development Board, and Stratix III Development Board). The various video signals will display test patterns on the LCD screen.

The supported video formats are listed below:

640x480@P60> 720x480@P60 1024x768@P60 1280x1024@P60 1920x1080@P60 1600x1200@P60Transmission Demo Hardware Setup

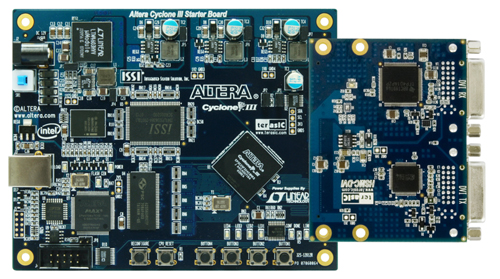

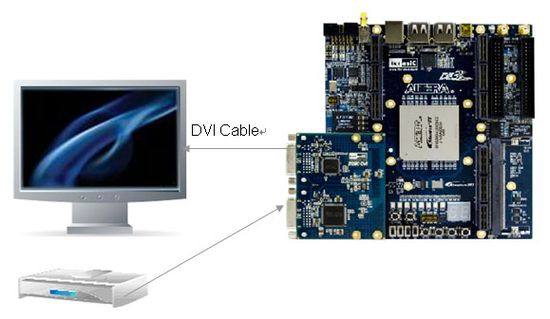

![]() Loopback Demo

Loopback Demo

(Full source code included)

The Loopback demonstration displays the groundwork of a connection established between the DVI source device to the transmitter output of the DVI daughter board. The loopback (Internal bypass) forms the DVI video signals within the FPGA board, as video output pins of the receiver are directly connected to the input video pins of the transmitter. The supported FPGA board for the Loopback demonstration includes (DE3, Cyclone III Starter Board, Cyclone III Development Board, Stratix III Development Board).

Loopback Demo Hardware Setup

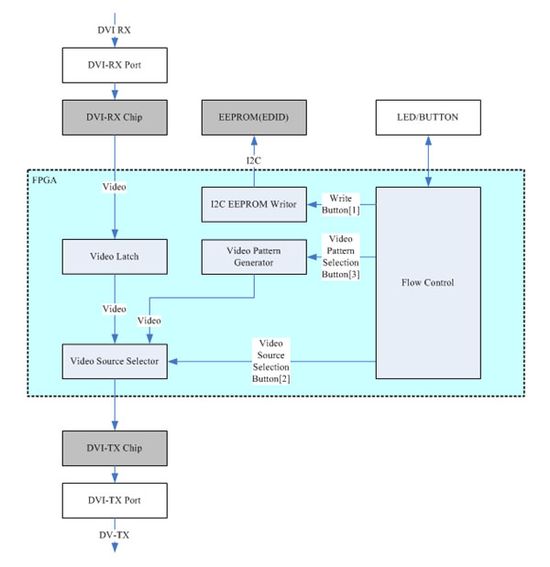

System Block diagram of the DVI demonstration

Kit Contents

The package of the DVI-HSMC board includes

The CD contains technical documents of the DVI-HSMC daughter board, and reference designs for the following main boards: the DE3, Cyclone III & Stratix III development board and the Cyclone III Starter board with full source code.

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Brak towaru

Brak towaru

VEEK-MT2S to płytka deweloperska oparta na układzie Cyclone V SX SoC Cyclone V SX SoC—5CSXFC6D6F31C6N. W zestawie, oprócz płytki z układem programowalnym FPGA, znajdują się również 7-calowy wyświetlacz TFT dotykowy o rozdzielczości 800 x 480 pikseli, kamera o rozdzielczości 8 Megapikseli (3264 x 2448 pikseli), czujnik światła czujnik IMU 9DOF (akcelerometr, żyroskop, magnetometr). Terasic K0161

Brak towaru

[CENA EDUKACYJNA] Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE oraz minikomputer z układem Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). Moduł FPGA posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0650

Brak towaru

Brak towaru

Płytka rozwojowa z układem FPGA Aria 10 GX to idealne rozwiązanie dla projektów wymagajacych dużej pojemności pamięci, szybkiej transmisji danych oraz efektywnego zarzadzania mocą. Terasic P0489

Brak towaru

Brak towaru

Moduł ewaluacyjny z procesorem Intel Stratix 10 SoC z elementami logicznymi 2800K. Moduł posiada pamięć DDR4 SDRAM (do 64 GB), wbudowany USB-Blaster II, Ethernet, microSD, miniUSB oraz złącza FMC/FMC+ do rozbudowy. TerasIC Apollo S10 SoM Board (P0630)

Brak towaru

Terasic DE10-Lite Board to niskobudżetowa płytka deweloperska z układem FPGA Altera MAX 10. Płyta zawiera szereg komponentów umożliwiających naukę oraz tworzenie prototypów projektów opartych o układy FPGA

Brak towaru

Zestaw elementów przeznaczony dla zestawów ewaluacyjnych z układami programowalnymi z rodziny Cyclone V SoC FPGA, w którego skład wchodzą; 7-calowy wyświetlacz TFT z obsługą dotyku (5-punktów), 8 megapikselowa kamera z autofocusem oraz czujniki (światła, akcelerometr, żyroskop, magnetometr). Terasic P0494

Brak towaru

Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE i obsługuje PCIe Gen 2x4. Płytka posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0559

Brak towaru

Terasic ADC-SoC to płyta rozwojowa z układem programowalnym FPGA oraz dwukanałowym szybkim przetwornikiem ADC. Płyta bazuje na module Terasic DE0-Nano-SoC. Wbudowany przetwornik ADC wykorzystuje SMA jako interfejs wejściowy, posiada dwa kanały, oferuje rozdzielczość 14-bitową, i szybkość próbkowania do 150 MSPS Megasamples per Second). Terasic (P0435)

Brak towaru

Zestaw startowy DE10-Nano Kit z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. Terasic P0496

Karta HTG-M przeznaczona jest dla zestawów ewaluacyjnych z układami FPGA, które zostały wyposażone w złącze HSMC (High-Speed Mezzanine connector) lub HSTC (High-Speed Terasic Connector). Karta HTG posiada trzy złącza męskie (40-pinowe). Pozwala na konwersje wejść/wyjść HSMC do dwóch 40-pinowych złącz prototypowych lub złącza HSTC do trzech 40-pinowych złącz prototypowych. TerasIC P0033

Brak towaru

Zestaw startowy VEEK-MT2-C5SoC z układem System-on-Chip z rodziny Cyclone V SX SoC. W zestawie 7-calowy wyświetlacz, 8 megapikselową kamerę z autofocusem, czujnik światła, żyroskop, magnetometr oraz 3 osiowy akcelerometr. Terasic K0160

Brak towaru