6 014,45 zł Netto

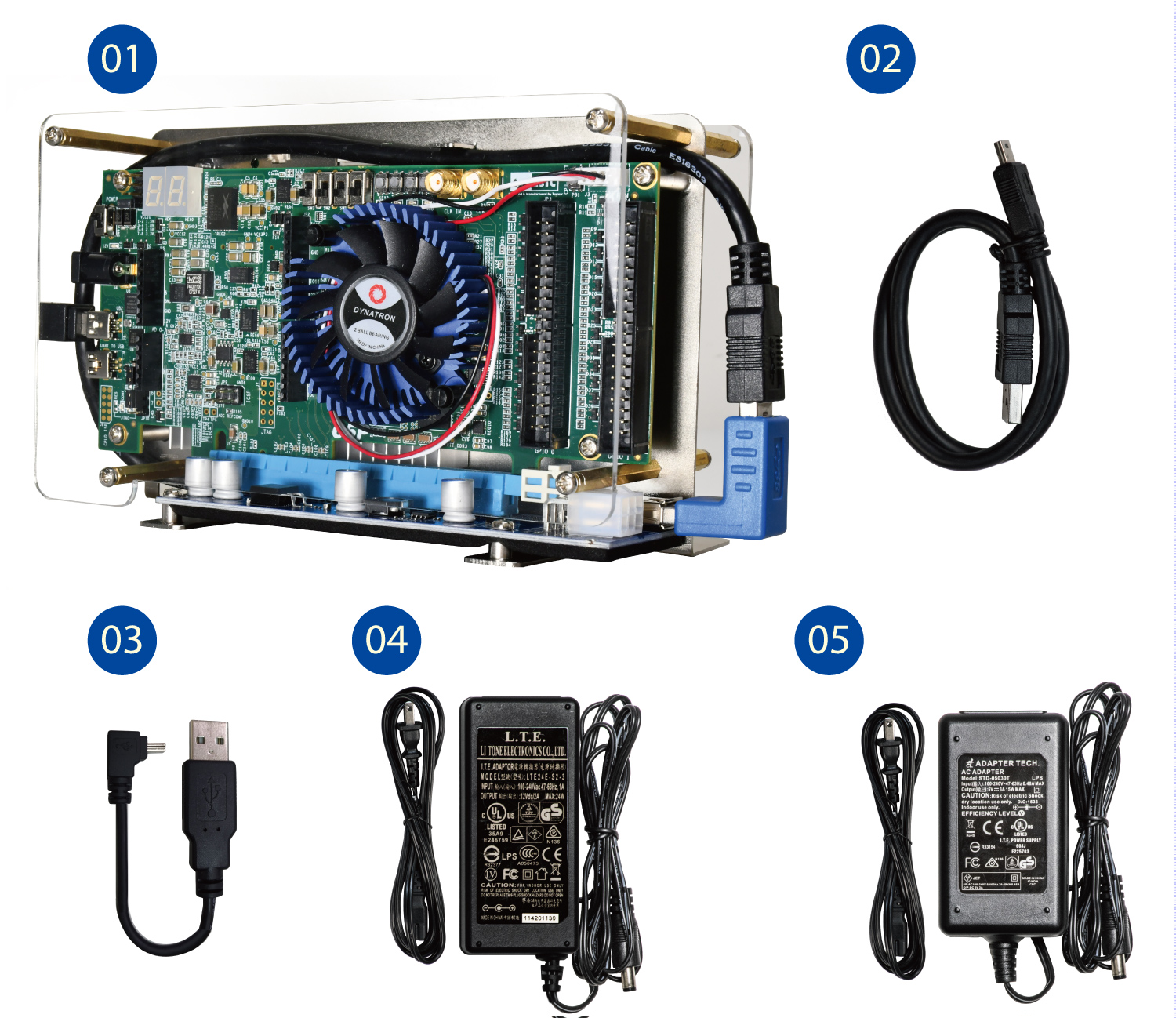

[CENA EDUKACYJNA] Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE oraz minikomputer z układem Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). Moduł FPGA posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0650

Oferta przeznaczona wyłącznie dla odbiorców akademickich (studentów i wykładowców wyższych uczelni)!

Składając zamówienie należy podać:

- imię i nazwisko użytkownika

- stanowisko

- adres e-mail użytkownika (adres e-mail musi być z domeny uczelni)

- pełną nazwę uczelni

- nazwę wydziału/instytutu/zakładu dydaktycznego

- adres uczelni

- stronę internetową uczelni

- telefon

- zastosowanie produktu

W uzasadnionych przypadkach zastrzegamy sobie prawo do odmowy zrealizowania zamówienia z oferty akademickiej.

Wszelkie zapytania można kierować na adres: sprzedaz@kamami.pl.

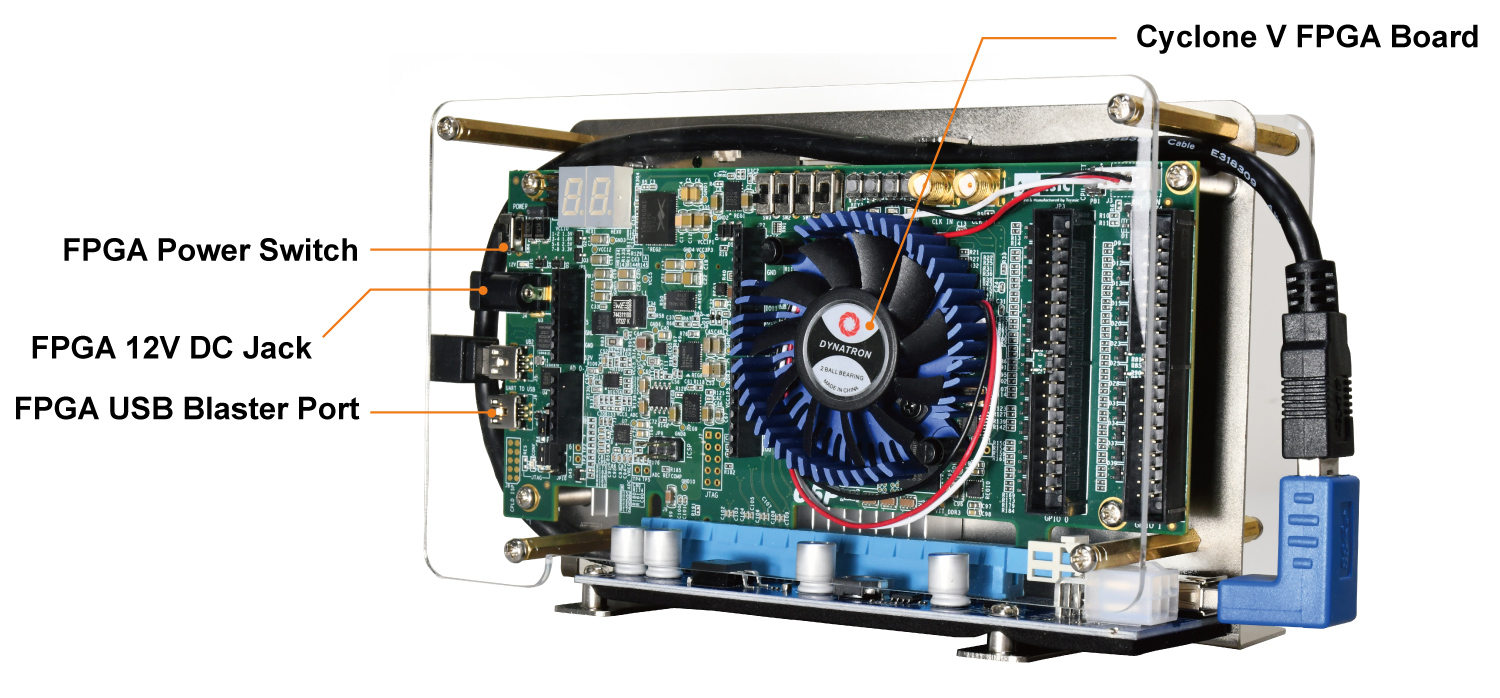

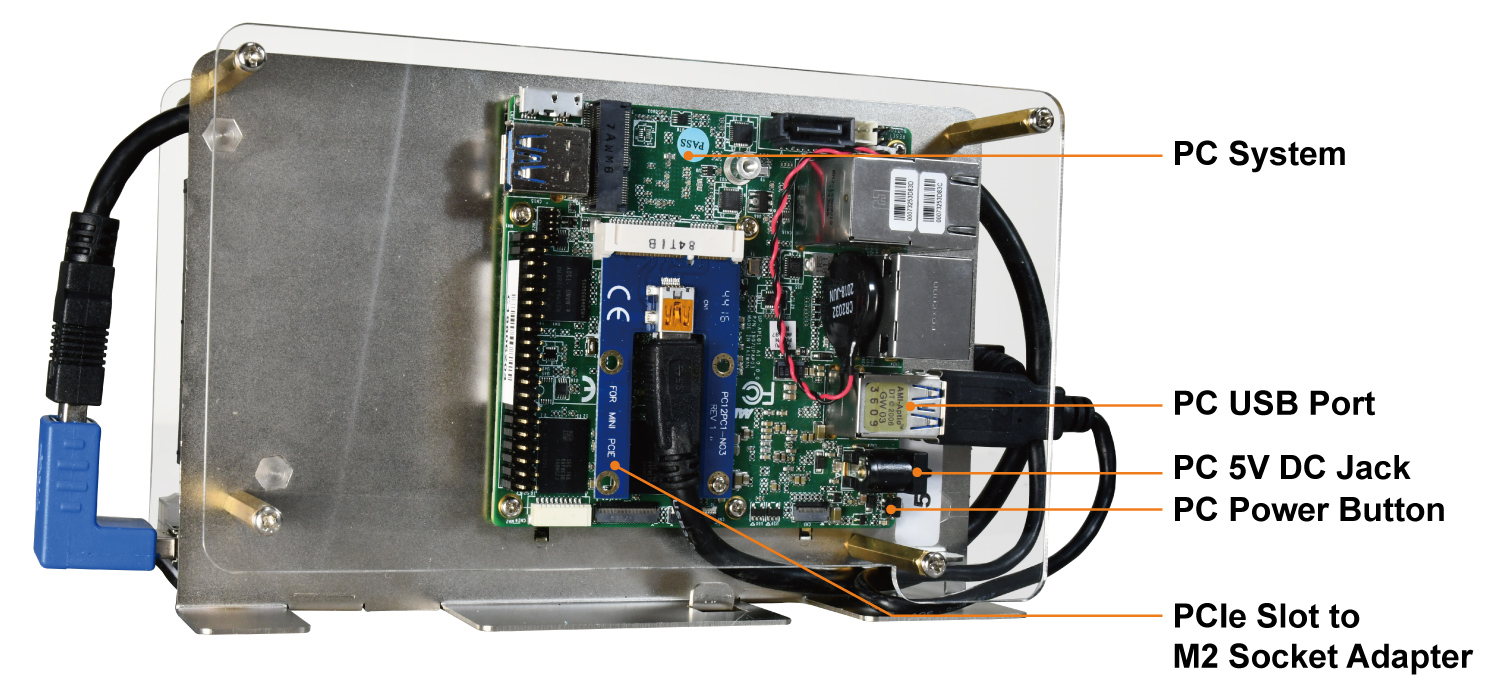

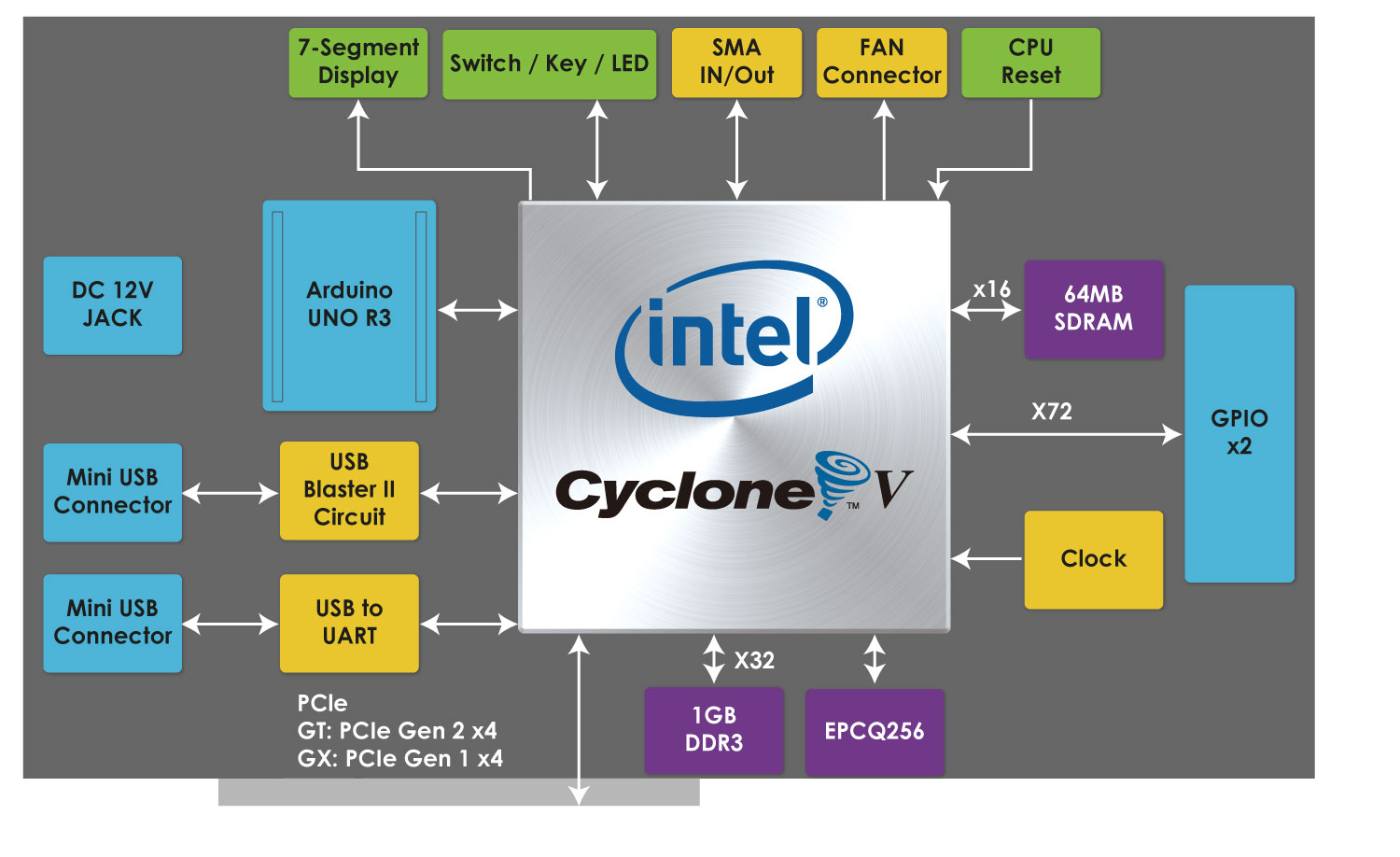

OpenVINO to zestaw startowy FPGA w postaci karty z złączem PCIe oraz zestawem PC z układem Intel Celeron Dual Core. Zestaw jest wyposażony w programowalny układ Cyclone V GT z 301K LE i obsługuje PCIe Gen 2x4. FPGA posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO czy pozwalające podłączyć rozszerzenia Arduino. Układ PC wyposażony jest w 64 GB pamięci eMMC oraz 4 GB pamięci RAM DDR4. To sprawia, że zestaw startowy OpenVINO to konfigurowalna platforma łącząca dużą wydajnością obliczeniową i niskie zużycie energii.

Pakiet OpenVINO zawiera projekty referencyjne dla wszystkich urządzeń peryferyjnych zestawu oraz szczegółową instrukcję dla programistów.

Zestaw CPU (PC)

Zestaw FPGA OpenVINO Starter Kit

Opis elementów składowych i rozmieszczenie złącz

Diagram blokowy

Producent BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

TerasIC DE0 to kompletny zestaw ewaluacyjny oparty na FPGA Cyclone III, zaprojektowany do nauki, testowania i wdrażania systemów cyfrowych. Oferuje szeroki zestaw interfejsów i peryferiów umożliwiających tworzenie złożonych projektów zarówno edukacyjnych, jak i przemysłowych.

Brak towaru

VEEK-MT2S to płytka deweloperska oparta na układzie Cyclone V SX SoC Cyclone V SX SoC—5CSXFC6D6F31C6N. W zestawie, oprócz płytki z układem programowalnym FPGA, znajdują się również 7-calowy wyświetlacz TFT dotykowy o rozdzielczości 800 x 480 pikseli, kamera o rozdzielczości 8 Megapikseli (3264 x 2448 pikseli), czujnik światła czujnik IMU 9DOF (akcelerometr, żyroskop, magnetometr). Terasic K0161

Brak towaru

Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE oraz minikomputer z układem Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). Moduł FPGA posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0650

Brak towaru

Wyświetlacz LCD alfanumeryczny 2x16 bez podświetlenia przeznaczony do zestawów firmy TerasIC (DE0, DE1, DE2 , DE2 -115). P0075

Stratix V GX FPGA Video Development System

Brak towaru

Cyclone V E FPGA Video Development System

Brak towaru

Płytka TerasIC C5G (P0150) umożliwia rozwój zaawansowanych aplikacji FPGA wymagających wysokiej przepustowości i elastycznej komunikacji. Płytka sprawdza się w projektach badawczo-rozwojowych, telekomunikacyjnych i przemysłowych, gdzie istotne pozostają wydajność, dostęp do szybkich interfejsów oraz kompatybilność z narzędziami projektowymi Cyclone V.

Brak towaru

Wszechstronna i niezwykle popularna platforma do nauki oraz rozwoju projektów opartych o architekturę ARM + FPGA. Dzięki bogatemu wyposażeniu, dużej ilości pamięci, licznym interfejsom oraz wsparciu narzędzi firmy Intel/Altera, płytka doskonale sprawdzi się w edukacji akademickiej, badaniach naukowych oraz prototypowaniu zaawansowanych systemów wbudowanych i multimedialnych. To idealny wybór dla studentów, inżynierów i hobbystów chcących poznać pełne możliwości systemów SoC.DE1-SoC Development Kit

TerasIC LT24 to moduł z wyświetlaczem LCD 2,4-calowym o rozdzielczości 320 x 240 pikseli. Wyświetlacz wyposażony jest w panel dotykowy rezystancyjny. Wyświetlacz przeznaczony jest do użycia z zestawami uruchomieniowymi TerasIC ze złączem GPIO 2x20. P0185

Brak towaru

Terasic DE1-SoC-MTL2 to rozbudowana i sprawdzona platforma dla inżynierów, studentów i zespołów R&D, którzy potrzebują wydajnego SoC FPGA z dotykowym interfejsem graficznym. Idealna do projektów, w których liczy się połączenie elastyczności FPGA z wygodą systemu Linux i nowoczesnym HMI.

Płyta bazowa FPGA z układem FPGA z rodziny MAX10 z 7", 5-punktowym wyświetlaczem multidotykowym. Oparty na układzie 10M50DAF484C6G. 512 Mb pamięci Flash, gniazdo miroSD, wejście Audio, Video, zasilanie 5 V/3 A.

Brak towaru

Terasic Spider to sześcionożny robot kroczący z 18 serwomechanizmami sterowanymi przez płytkę Altera DE0-Nano-SoC łączącą układ FPGA oraz procesor ARM Cortex-A9. Zestaw zawiera złożonego robota oraz liczne akcesoria. P0425

A-Cute Car Robotic Kit to kompletne 3-kołowe podwozie robota mobilnego wraz ze sterownikiem opartym o układ FPGA do samodzielnego programowania. P0467

Brak towaru

Terasic DE10-Lite Board to niskobudżetowa płytka deweloperska z układem FPGA Altera MAX 10. Płyta zawiera szereg komponentów umożliwiających naukę oraz tworzenie prototypów projektów opartych o układy FPGA. Terasic P0466

Terasic DE10-Lite Board to niskobudżetowa płytka deweloperska z układem FPGA Altera MAX 10. Płyta zawiera szereg komponentów umożliwiających naukę oraz tworzenie prototypów projektów opartych o układy FPGA

Sterownik serwomechanizmów do zestawów FPGA TerasIC serii DE umożliwia sterowanie maksymalnie 24 serwomechanizmami. Dostarcza napięcie 6 V do zasilania serwomechanizmów. W zestawie serwomechanizm MG966R i taśma do połączenia z zestawem FPGA. P0288

Moduł z kamerą przeznaczony do użycia z zestawami Terasic. Kamera posiada przetwornik o rozdzielczości 8 Megapikseli (3264 x 2448), do komunikacji wykorzystuje interfejs MIPI. Na module znalazł się również dekoder MIPI oraz układ HDMI-TX. Terasic P0449

Brak towaru

[CENA EDUKACYJNA] Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE oraz minikomputer z układem Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). Moduł FPGA posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0650