462,60 zł Netto

Zestaw startowy/ewaluacyjny Terasic DE0-Nano Board dla układów FPGA Cyclone IV firmy Altera. Jest to jeden z najmniejszych i najprostszych i jednocześnie dobrze wyposażonych zestawów startowych dla układów FPGA, jego standardowym wyposażeniem jest programator-konfigurator JTAG.

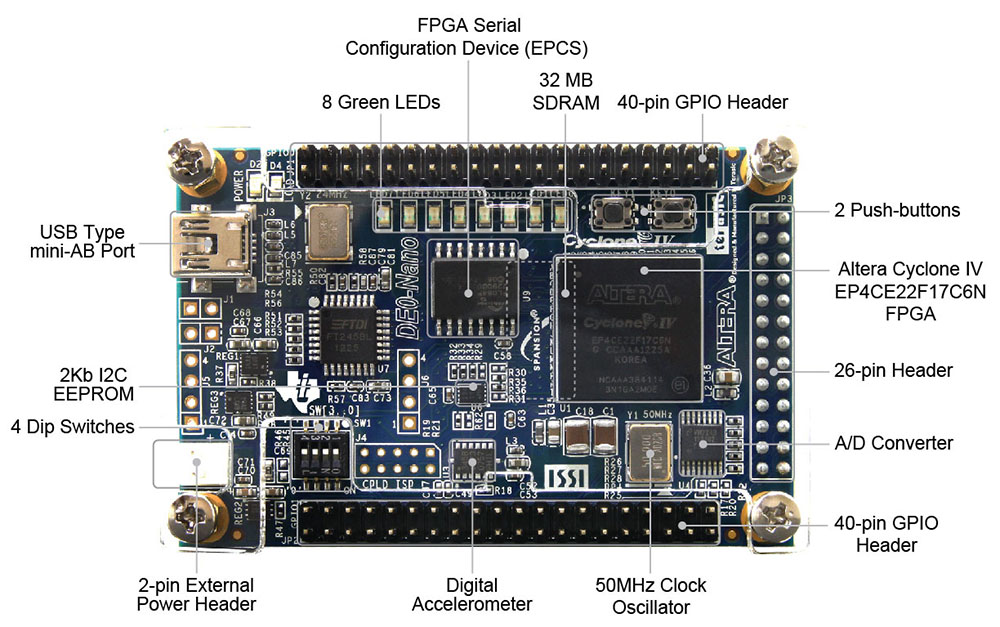

Terasic DE-Nano to kompaktowa płytka deweloperska oparta na układzie Altera Cyclone® EP4CE22F17C6N. Ten układ programowalny FPGA, posiada 22,320 elementów logicznych. Płytka dzięki wielu komponentom, jakimi są liczne diody LED, przyciski monostabilne, przełączniki suwakowe, akcelerometr, złącze z wejściami oraz wyjściami cyfrowymi, to idealne narzędzie do nauki programowania układów FPGA. Płytkę można także zastosować do prototypowania projektów związanych z tą tematyką.

Zaletą DE0-Nano są niewielkie wymiary i niska waga, tym co odróżnia ją od innych płytek tego typu to wiele możliwości zasilania, możliwe jest zasilanie za pomocą gniazda miniUSB, 2-pinowe złącze zasilające (3,6...5,7 V), lub dwa złącza DC 5 V.

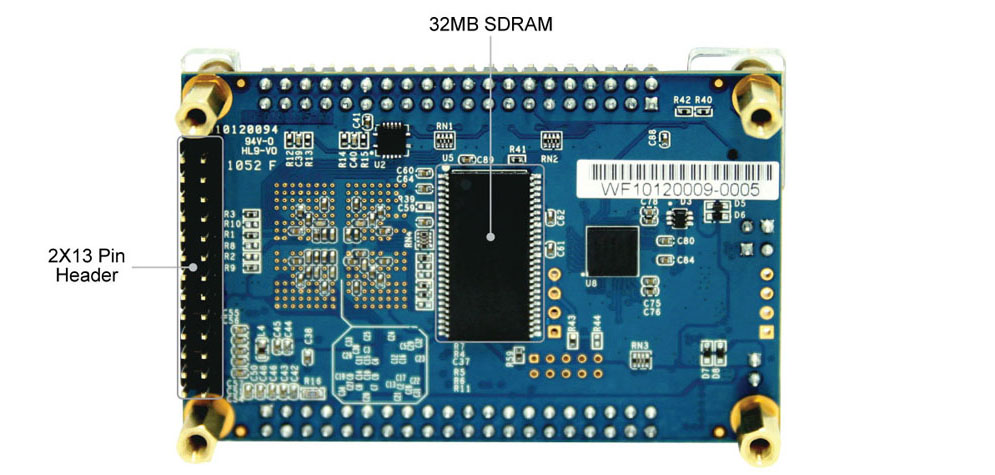

Rozmieszczenie elementów

Producent BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

TerasIC DE0 to kompletny zestaw ewaluacyjny oparty na FPGA Cyclone III, zaprojektowany do nauki, testowania i wdrażania systemów cyfrowych. Oferuje szeroki zestaw interfejsów i peryferiów umożliwiających tworzenie złożonych projektów zarówno edukacyjnych, jak i przemysłowych.

Brak towaru

[CENA EDUKACYJNA] Zestaw ewaluacyjny Terasic DE0 Board dla układów FPGA Cyclone III firmy Altera. Wyposażono go we wszystkie podstawowe peryferia umożliwiające prowadzenie prac badawczych i ewaluacyjnych z układami FPGA, w tym programator-konfigurator JTAG. Obniżona cena (w stosunku do klasycznej wersji Terasic DE0) dotyczy wyłącznie szkół, uczelni, wykładowców, uczniów i studentów.

Zestaw startowy/ewaluacyjny Terasic DE0-Nano Board dla układów FPGA Cyclone IV firmy Altera. Jest to jeden z najmniejszych i najprostszych i jednocześnie dobrze wyposażonych zestawów startowych dla układów FPGA, jego standardowym wyposażeniem jest programator-konfigurator JTAG.

Brak towaru

[CENA EDUKACYJNA] Zestaw startowy/ewaluacyjny Terasic DE0-Nano Board dla układów FPGA Cyclone IV firmy Altera. Jeden z najmniejszych i najprostszych zestawów startowych dla układów FPGA, wyposażony w podstawowe peryferia, w tym programator-konfigurator JTAG.Obniżona cena (w stosunku do klasycznej wersji Terasic DE0-Nano) dotyczy wyłącznie szkół, uczelni, wykładowców, uczniów i studentów. P0082

TerasIC LT24 to moduł z wyświetlaczem LCD 2,4-calowym o rozdzielczości 320 x 240 pikseli. Wyświetlacz wyposażony jest w panel dotykowy rezystancyjny. Wyświetlacz przeznaczony jest do użycia z zestawami uruchomieniowymi TerasIC ze złączem GPIO 2x20. P0185

Terasic HDMI-FMC to karta rozszerzająca układy ewaluacyjny o możliwość wyświetlania oraz odbierania obrazu wideo przy pomocy złącz HDMI. Pozwalają wyświetlać obraz w rozdzielczości 4K@30FPS. Wspiera HDMI 1.4a. Terasic P0431

Terasic NET-FMC to karta rozszerzająca z Gigabajtowym Ethernetem oraz interfejsem FMC. Dzięki temu interfejsowi może być używana z zestawami firmy Terasic. Terasic P0481

Brak towaru

Zestaw startowy DE10-Standard z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. P0493

Zestaw startowy DE10-Standard z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. P0493

Brak towaru

Zestaw startowy DE10-Nano Kit z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. Terasic P0496

Brak towaru

Zestaw startowy DE10-Nano Kit z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. Terasic P0496

VEEK-MT2S to płytka deweloperska oparta na układzie Cyclone V SX SoC Cyclone V SX SoC—5CSXFC6D6F31C6N. W zestawie, oprócz płytki z układem programowalnym FPGA, znajdują się również 7-calowy wyświetlacz TFT dotykowy o rozdzielczości 800 x 480 pikseli, kamera o rozdzielczości 8 Megapikseli (3264 x 2448 pikseli), czujnik światła czujnik IMU 9DOF (akcelerometr, żyroskop, magnetometr). Terasic K0161

Brak towaru

VEEK-MT2S to płytka deweloperska oparta na układzie Cyclone V SX SoC Cyclone V SX SoC—5CSXFC6D6F31C6N. W zestawie, oprócz płytki z układem programowalnym FPGA, znajdują się również 7-calowy wyświetlacz TFT dotykowy o rozdzielczości 800 x 480 pikseli, kamera o rozdzielczości 8 Megapikseli (3264 x 2448 pikseli), czujnik światła czujnik IMU 9DOF (akcelerometr, żyroskop, magnetometr). Terasic K0161

Brak towaru

Adapter przeznaczony do łączenia płytek ze złączem PCIe z komputerem. Może obsługiwać interfejs PCIe Gen3 x4. Terasic P0492

Płytka rozwojowa z układem FPGA Aria 10 GX to idealne rozwiązanie dla projektów wymagajacych dużej pojemności pamięci, szybkiej transmisji danych oraz efektywnego zarzadzania mocą. Terasic P0489

Brak towaru

Zestaw Terasic VEEK-MT2 zapewnia kompletną platformę sprzętowo-programową do projektowania systemów wbudowanych i multimedialnych z wykorzystaniem układów FPGA. Umożliwia tworzenie i testowanie aplikacji interaktywnych, sterujących oraz pomiarowych dzięki rozbudowanej bazie interfejsów, pamięci i czujników.

Brak towaru

Robot może rozpoznawać postawę w czasie rzeczywistym za pomocą czujnika przyspieszenia i żyroskopu, a także osiągnąć równowagę poprzez sterowanie silnikami w celu regulacji pozycji. Terasic P0582

Brak towaru

Zintegrowany komputer jednopłytkowy z rdzeniem Cyclone V SoC. SoC SoM zawiera pamięć DDR3, pamięć Flash, system zarządzania energią, wspólne kontrolery interfejsów i oprogramowanie do obsługi płyt (BSP). Terasic P0581

Brak towaru

Zestaw rozwojowy z układem SoC FPGA Intel Arria 10. Dedykowany do przemysłowych aplikacji wbudowanych o wysokich wymaganiach wydajności. Terasic P0506

Brak towaru

Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE i obsługuje PCIe Gen 2x4. Płytka posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0559

Brak towaru

[CENA EDUKACYJNA] Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE i obsługuje PCIe Gen 2x4. Płytka posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0559

Brak towaru

Zestaw startowy/ewaluacyjny Terasic DE0-Nano Board dla układów FPGA Cyclone IV firmy Altera. Jest to jeden z najmniejszych i najprostszych i jednocześnie dobrze wyposażonych zestawów startowych dla układów FPGA, jego standardowym wyposażeniem jest programator-konfigurator JTAG.