37 395,09 zł Netto

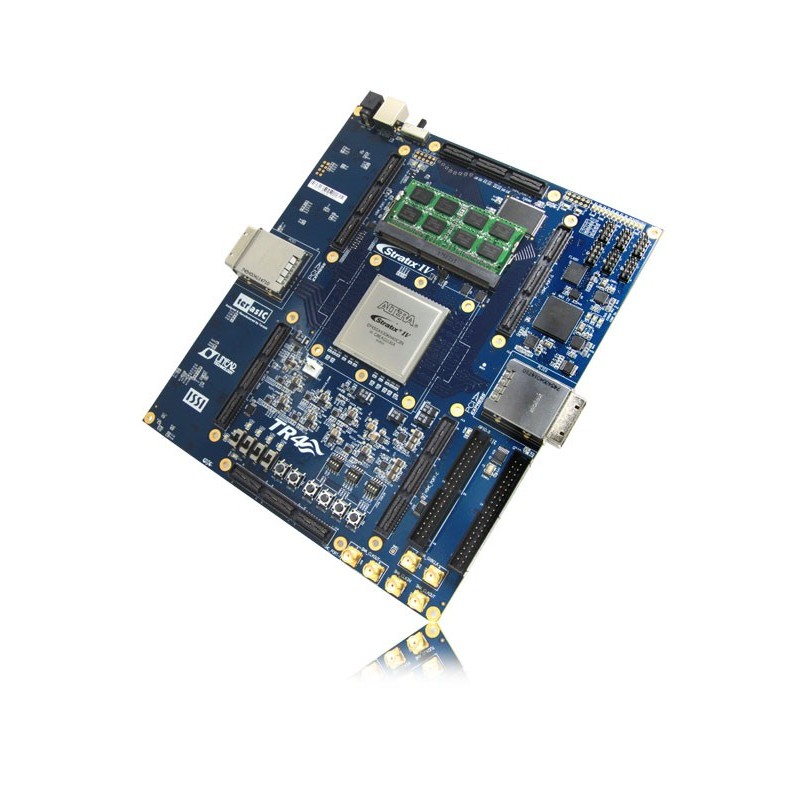

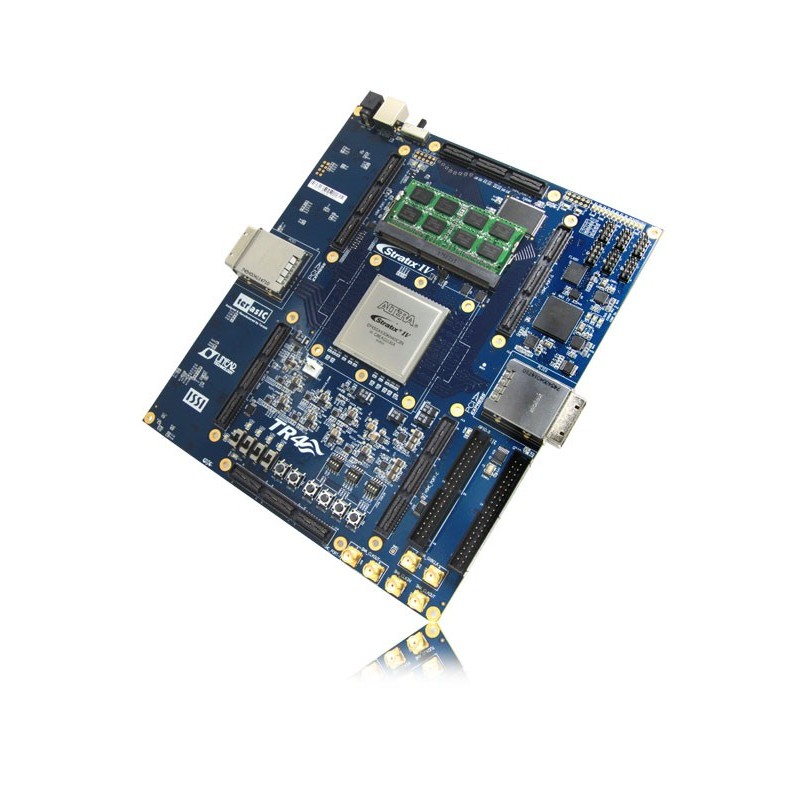

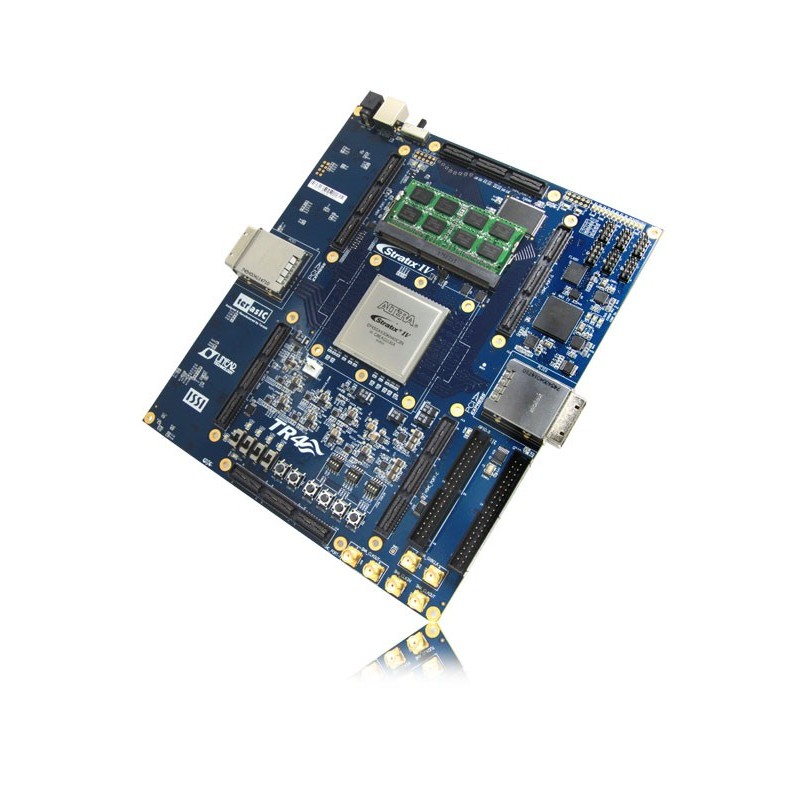

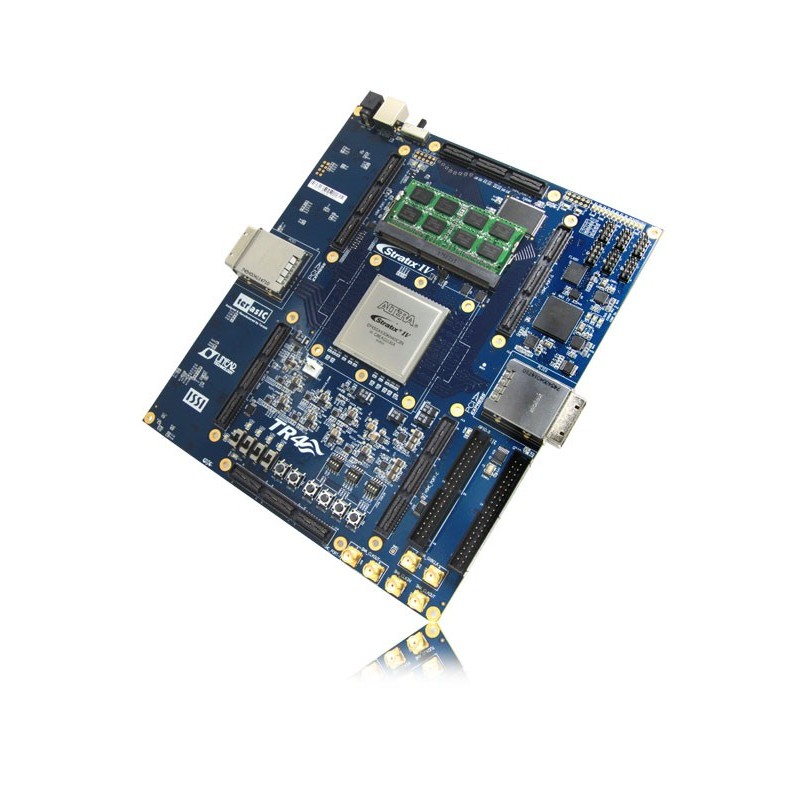

TerasIC TR4-530 (P0109) to zestaw rozwojowy FPGA z układem Stratix IV GX, oferujący wysoką wydajność logiczną, obsługę szybkiej pamięci DDR3 oraz szerokie możliwości rozbudowy przez złącza HSMC i PCIe. Platforma przeznaczona do prototypowania systemów cyfrowych, aplikacji PCI Express i przetwarzania danych w czasie rzeczywistym.

Zestaw rozwojowy TR4-530 oferuje zaawansowaną platformę sprzętową do projektowania systemów wymagających dużej wydajności obliczeniowej, rozbudowanej komunikacji szeregowej oraz zaawansowanego dostępu do pamięci. Płytka oparta na układzie FPGA Intel Stratix IV GX EP4SGX530 wyposażona została w 531 200 elementów logicznych, 1 024 bloków mnożników 18x18 oraz 27 376 Kbit pamięci wewnętrznej. Obsługuje także cztery twarde rdzenie PCIe oraz osiem pętli PLL.

Urządzenie oferuje gniazdo SO-DIMM DDR3 o pojemności do 4 GB z przepustowością teoretyczną do 68 Gb/s. W zestawie dostępna pamięć Flash 64 MB i 2 MB pamięci SSRAM. Płytka posiada sześć złączy HSMC (High Speed Mezzanine Card), które umożliwiają łatwe rozszerzanie funkcjonalności poprzez moduły córki. Złącza te zapewniają łącznie 16 szybkich transceiverów do 6,5 Gb/s oraz 68 kanałów LVDS.

Do komunikacji z komputerem służy wbudowany programator USB Blaster, a konfiguracja FPGA możliwa jest również przez JTAG. Układ zarządzający MAX II CPLD odpowiada za konfigurację oraz kontrolę nad programowalnym generatorem PLL. Zestaw obsługuje zasilanie z zewnętrznego źródła 19 V DC i umożliwia integrację wielu płytek TR4 w systemy wieloukładowe do prototypowania układów ASIC.

Producent BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Zestaw Terasic VEEK-MT2 zapewnia kompletną platformę sprzętowo-programową do projektowania systemów wbudowanych i multimedialnych z wykorzystaniem układów FPGA. Umożliwia tworzenie i testowanie aplikacji interaktywnych, sterujących oraz pomiarowych dzięki rozbudowanej bazie interfejsów, pamięci i czujników.

Brak towaru

Robot może rozpoznawać postawę w czasie rzeczywistym za pomocą czujnika przyspieszenia i żyroskopu, a także osiągnąć równowagę poprzez sterowanie silnikami w celu regulacji pozycji. Terasic P0582

Brak towaru

Zintegrowany komputer jednopłytkowy z rdzeniem Cyclone V SoC. SoC SoM zawiera pamięć DDR3, pamięć Flash, system zarządzania energią, wspólne kontrolery interfejsów i oprogramowanie do obsługi płyt (BSP). Terasic P0581

Brak towaru

Zestaw rozwojowy z układem SoC FPGA Intel Arria 10. Dedykowany do przemysłowych aplikacji wbudowanych o wysokich wymaganiach wydajności. Terasic P0506

Brak towaru

Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE i obsługuje PCIe Gen 2x4. Płytka posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0559

Brak towaru

[CENA EDUKACYJNA] Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE i obsługuje PCIe Gen 2x4. Płytka posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0559

Brak towaru

Moduł pamięci SODIMM firmy TerasIC o pojemności 18MB i częstotliwości pracy 550MHz. Moduł przeznaczony jest do pracy z układami FPGA Intel Stratix 10 w zestawach ewaluacyjnych takich jak TerasIC DE10-Pro-GX-280-4G oraz TerasIC DE10-Pro-GX-280-8G. TerasIC S0534

Brak towaru

Moduł SoM z układem SoC łączącym FPGA z rdzeniem ARM Cortex-A9. Płytka wyposażona jest w złacze DDR4 Eadge (z zasialniem 3,3 V). Terasic P0553

Brak towaru

MAX 10 Plus jest zestawem deweloperskim opartym o układ FPGA od Intela, wyposażony w 50 000 programowalnych elementów logicznych. Digilent P0638

Brak towaru

Moduł XTS-FMC jest rozszerzeniem dla układów FPGA pozwalającym na dostęp do kanałów/interfejsów komunikacyjnych poprzez złącze SMA. TerasIC P0401

Brak towaru

[CENA EDUKACYJNA] Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE oraz minikomputer z układem Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). Moduł FPGA posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0650

Brak towaru

Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE oraz minikomputer z układem Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). Moduł FPGA posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0650

Brak towaru

Platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. TerasIC T-Core P0633

Brak towaru

Platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. Wersja edukacyjna. TerasIC T-Core P0633

Brak towaru

Kompaktowy zestaw FPGA z układem Intel Arria 10 GX wyposażony w 8 GB pamięci DDR4-2133 oraz złącze komunikacyjne Thunderbolt 3. Może być zastosowany bezpośrednio na laptopach lub innych urządzeniach przenośnych. Terasic FLIK P0642

Brak towaru

Kompaktowy zestaw FPGA z układem Intel Arria 10 GX wyposażony w 8 GB pamięci DDR4-2133 oraz złącze komunikacyjne Thunderbolt 3. Może być zastosowany bezpośrednio na laptopach lub innych urządzeniach przenośnych. Wersja edukacyjna. Terasic FLIK P0642

Brak towaru

TerasIC TR4-530 (P0109) to zestaw rozwojowy FPGA z układem Stratix IV GX, oferujący wysoką wydajność logiczną, obsługę szybkiej pamięci DDR3 oraz szerokie możliwości rozbudowy przez złącza HSMC i PCIe. Platforma przeznaczona do prototypowania systemów cyfrowych, aplikacji PCI Express i przetwarzania danych w czasie rzeczywistym.