Terasic DE0-Nano

Altera DE0 NANO Development and Education Board

Overview

The DE0-Nano board introduces a compact-sized FPGA development platform suited for prototyping circuit designs such as robots and "portable" projects. The board is designed to be used in the simplest possible implementation targeting the Cyclone IV device up to 22,320 LEs.

The DE0-Nano has a collection of interfaces including two external GPIO headers to extend designs beyond the DE0-Nano board, on-board memory devices including SDRAM and EEPROM for larger data storage and frame buffering, as well as general user peripheral with LEDs and push-buttons.

The advantages of the DE0-Nano board include its size and weight, as well as its ability to be reconfigured without carrying superfluous hardware, setting itself apart from other general purpose development boards. In addition, for mobile designs where portable power is crucial, the DE0-Nano provides designers with three power scheme options including a USB mini-AB port, 2-pin external power header and two DC 5V pins.

Specification

Cyclone® IV EP4CE22F17C6N FPGA

- 22,320 Logic elements (LEs)

- 594 Embedded memory (Kbits)

- 66 Embedded 18 x 18 multipliers

- 4 General-purpose PLLs

- 153 Maximum FPGA I/O pins

Configuration Status and Set-Up Elements

- On-board USB-Blaster circuit for programming

- Altera serial configuration device – EPCS16

Expansion Header

- Two 40-pin Headers (GPIOs) provides 72 I/O pins

- Two 5V power pins, two 3.3V power pins and four ground pins

- One 26-pin header provides 16 digital I/O pins and 8 analog input pins to connect to analog sensors, etc

Memory Devices

- 32MB SDRAM

- 2Kb I2C EEPROM

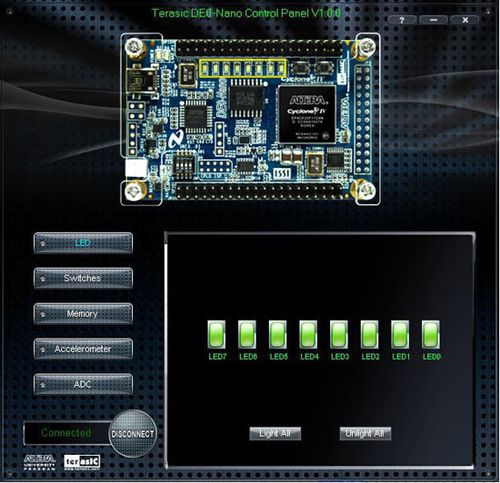

General User Input/Output

- 8 green LEDs

- 2 debounced push-buttons

- 4 dip switches

G-Sensor

- ADI ADXL345, 3-axis accelerometer with high resolution (13-bit)

A/D Converter

- NS ADC128S022, 8-Channel, 12-bit A/D Converter

- 50 ksps to 200 ksps

Clock System

- On-board 50MHz clock oscillator

Power Supply

- USB Type mini-AB port (5V)

- Two DC 5V pins of the GPIO headers (5V)

- 2-pin external power header (3.6-5.7V)

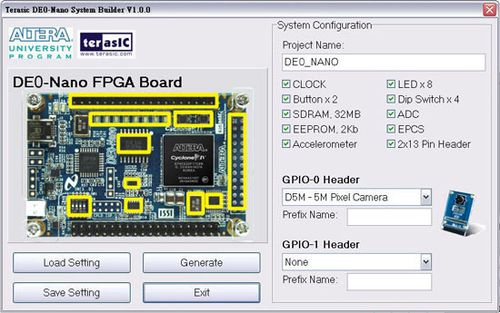

![]() Connect D5M

Connect D5M

- Connect with 5-megapixel CMOS Sensor (D5M)

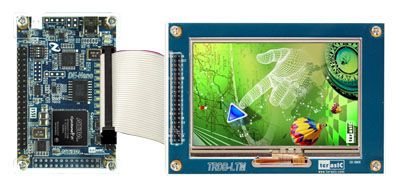

![]() Connect LTM

Connect LTM

- Connect with LCD Touch Screen Module (LTM)

![]() Connect THDB-ADA

Connect THDB-ADA

- Connect with Analog to Digital/Digital to Analog Conversion Daughter Card (THDB-ADA)

Layout

Resources

| Title | Version | Size(KB) | Date Added | Download |

|---|---|---|---|---|

| DE0_Nano_User_manual | - | 9200 | 2011-01-25 |  |

Kit Contents

Code: P0082

Manufacturer BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Poland sprzedaz@kamami.pl 22 767 36 20

Responsible person BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Poland sprzedaz@kamami.pl 22 767 36 20

TerasIC DE0 is a complete evaluation kit based on the Cyclone III FPGA, designed for learning, testing, and implementing digital systems. It offers a wide range of interfaces and peripherals enabling the creation of complex projects for both educational and industrial purposes.

No product available!

[EDUCATIONAL PRICE] Terasic DE0 Board evaluation kit for Altera Cyclone III FPGA devices. It is equipped with all basic peripherals enabling research and evaluation work with FPGAs, including a JTAG programmer-configurator. The reduced price (compared to the standard Terasic DE0 version) applies exclusively to schools, universities, lecturers, pupils, and students.

No product available!

Altera DE0 NANO Development and Education Board introduces a compact-sized FPGA development platform suited for prototyping circuit designs such as robots and "portable" projects. The board is designed to be used in the simplest possible implementation targeting the Cyclone IV device up to 22,320 LEs.

The Terasic LT24 is a 2.4” LCD touch module with 240(H) x 320(V) display resolution. It can be bundled with various Terasic FPGA development boards through the 2x20 GPIO interface. P0185

FPGA starter kit equipped with Cyclone V GT with 301K LE and supports PCIe Gen 2x4. The board has 1 GB DDR3 memory, 64 MB SDRAM memory, UART-USB interface and extensions such as GPIO and Arduino. Terasic P0559

No product available!

[EDUCATIONAL PRICE] FPGA starter kit equipped with Cyclone V GT with 301K LE and supports PCIe Gen 2x4. The board has 1 GB DDR3 memory, 64 MB SDRAM memory, UART-USB interface and extensions such as GPIO and Arduino. Terasic P0559

No product available!

TerasIC SODIMM memory module with 18MB capacity and 550MHz operating frequency. The module is designed to work with Intel Stratix 10 FPGAs in evaluation kits such as TerasIC DE10-Pro-GX-280-4G and TerasIC DE10-Pro-GX-280-8G. TerasIC S0534

No product available!

SoM module with SoC connecting the FPGA with the ARM Cortex-A9 core. The board is equipped with DDR4 Eadge connector (with 3.3 V power supply). P0553

No product available!

MAX 10 Plus is a development kit based on the FPGA chip from Intel, equipped with 50,000 programmable logic elements. p0638

No product available!

The XTS-FMC module is an extension for FPGA devices that allows access to communication channels via the SMA connector. P0401

No product available!

[EDUCATIONAL PRICE] FPGA starter kit equipped with Cyclone V GT with 301K LE and minicomputer with Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). The FPGA module has 1 GB DDR3 memory, 64 MB SDRAM memory, UART-USB interface and extensions such as GPIO and Arduino. Terasic P0650

No product available!

FPGA starter kit equipped with Cyclone V GT with 301K LE and minicomputer with Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). The FPGA module has 1 GB DDR3 memory, 64 MB SDRAM memory, UART-USB interface and extensions such as GPIO and Arduino. Terasic P0650

No product available!

Development platform based on Intel MAX 10 FPGA. The system provides the user with 50,000 logical elements and 1638 kbits M9K and 5888 kbits Flash. The board contains components such as embedded USB-Blaster II, QSPI Flash, ADC connector, WS2812B RGB LED and 2x6 TMD connector. TerasiC T-Core P0633

No product available!

Development platform based on Intel MAX 10 FPGA. The system provides the user with 50,000 logical elements and 1638 kbits M9K and 5888 kbits Flash. The board contains components such as built-in USB-Blaster II, QSPI Flash, ADC connector, WS2812B RGB LED and 2x6 TMD connector. Academic version. TerasiC T-Core P0633

No product available!

Compact FPGA kit with Intel Arria 10 GX chip equipped with 8 GB DDR4-2133 memory and Thunderbolt 3 communication connector. Can be used directly on laptops or other portable devices. Terasic FLIK P0642

No product available!

Compact FPGA kit with Intel Arria 10 GX chip equipped with 8 GB DDR4-2133 memory and Thunderbolt 3 communication connector. Can be used directly on laptops or other portable devices. Academic version. Terasic FLIK P0642

No product available!

Evaluation module with Intel Stratix 10 SoC processor with 2800K logic elements. The module has DDR4 SDRAM memory (up to 64 GB), built-in USB-Blaster II, Ethernet, microSD, miniUSB and expandable FMC/FMC+ connectors. TerasIC Apollo S10 SoM Board (P0630)

No product available!

Development kit with Apollo S10 module and base board. Equipped with an Intel Stratix 10 SoC processor with 2800K logic elements, has a DDR4 SDRAM memory (up to 64 GB), built-in USB-Blaster II, Ethernet, microSD, miniUSB and QSFP connectors and USB type C. TerasIC Apollo Developer Kit (P0671)

No product available!

FPGA starter kit with Intel Stratix 10 SX chip. The module has integrated transceivers that transmit data at speeds up to 28.3 Gb/s, making DE10-Pro fully compatible with version 3.0 of the PCI Express standard. The DE10-Pro offers fast parallel Flash memory and four SO-DIMMs that have 4 GB DDR4 SDRAM. Terasic P0627

No product available!

FPGA starter kit with Intel Stratix 10 SX chip. The module has integrated transceivers that transmit data at speeds up to 28.3 Gb/s, making DE10-Pro fully compatible with version 3.0 of the PCI Express standard. The DE10-Pro offers fast parallel Flash memory and four SO-DIMMs that have 8GB DDR4 SDRAM. Terasic P0629

No product available!

Altera DE0 NANO Development and Education Board