![Terasic DE0-Nano [EDU] - zestaw startowy z układem FPGA z rodziny Cyclone IV firmy Altera Terasic DE0-Nano [EDU] - zestaw startowy z układem FPGA z rodziny Cyclone IV firmy Altera](https://kamami.pl/4338-large_default/terasic-de0-nano-p0082-edu.jpg)

![Terasic DE0-Nano [EDU] - zestaw startowy z układem FPGA z rodziny Cyclone IV firmy Altera Terasic DE0-Nano [EDU] - zestaw startowy z układem FPGA z rodziny Cyclone IV firmy Altera](https://kamami.pl/4338-large_default/terasic-de0-nano-p0082-edu.jpg)

![Terasic DE0-Nano [EDU] - zestaw startowy z układem FPGA z rodziny Cyclone IV firmy Altera Terasic DE0-Nano [EDU] - zestaw startowy z układem FPGA z rodziny Cyclone IV firmy Altera](https://kamami.pl/4338-large_default/terasic-de0-nano-p0082-edu.jpg)

![Terasic DE0-Nano [EDU] - zestaw startowy z układem FPGA z rodziny Cyclone IV firmy Altera Terasic DE0-Nano [EDU] - zestaw startowy z układem FPGA z rodziny Cyclone IV firmy Altera](https://kamami.pl/4338-small_default/terasic-de0-nano-p0082-edu.jpg)

zł422.32 tax excl.

Altera DE0 NANO Development and Education Board introduces a compact-sized FPGA development platform suited for prototyping circuit designs such as robots and "portable" projects. The board is designed to be used in the simplest possible implementation targeting the Cyclone IV device up to 22,320 LEs.

ATTENTION! This product is for academic recipients (students and academic teachers) only!

After the ordering, please send us by e-mail the data listed below:

- the name and last name

- position (student, teacher)

- e-mail (with the University domain)

- University name

- Facultie / Section

- University address

- University phone no.

- End user application

The DE0-Nano board introduces a compact-sized FPGA development platform suited for prototyping circuit designs such as robots and "portable" projects. The board is designed to be used in the simplest possible implementation targeting the Cyclone IV device up to 22,320 LEs.

The DE0-Nano has a collection of interfaces including two external GPIO headers to extend designs beyond the DE0-Nano board, on-board memory devices including SDRAM and EEPROM for larger data storage and frame buffering, as well as general user peripheral with LEDs and push-buttons.

The advantages of the DE0-Nano board include its size and weight, as well as its ability to be reconfigured without carrying superfluous hardware, setting itself apart from other general purpose development boards. In addition, for mobile designs where portable power is crucial, the DE0-Nano provides designers with three power scheme options including a USB mini-AB port, 2-pin external power header and two DC 5V pins.

Cyclone® IV EP4CE22F17C6N FPGA

- 22,320 Logic elements (LEs)

- 594 Embedded memory (Kbits)

- 66 Embedded 18 x 18 multipliers

- 4 General-purpose PLLs

- 153 Maximum FPGA I/O pins

Configuration Status and Set-Up Elements

- On-board USB-Blaster circuit for programming

- Altera serial configuration device – EPCS16

Expansion Header

- Two 40-pin Headers (GPIOs) provides 72 I/O pins

- Two 5V power pins, two 3.3V power pins and four ground pins

- One 26-pin header provides 16 digital I/O pins and 8 analog input pins to connect to analog sensors, etc

Memory Devices

- 32MB SDRAM

- 2Kb I2C EEPROM

General User Input/Output

- 8 green LEDs

- 2 debounced push-buttons

- 4 dip switches

G-Sensor

- ADI ADXL345, 3-axis accelerometer with high resolution (13-bit)

A/D Converter

NS ADC128S022, 8-Channel, 12-bit A/D Converter

50 ksps to 200 ksps

Clock System

On-board 50MHz clock oscillator

Power Supply

Connectivity:

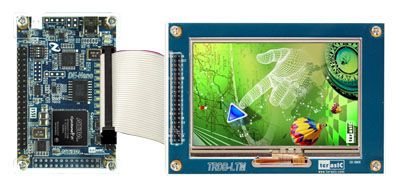

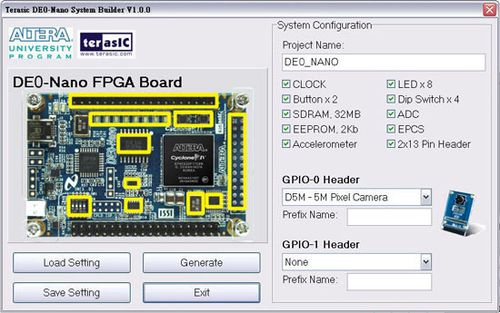

Connect D5M

- Connect with 5-megapixel CMOS Sensor (D5M)

Connect LTM

- Connect with LCD Touch Screen Module (LTM)

Connect THDB-ADA

- Connect with Analog to Digital/Digital to Analog Conversion Daughter Card (THDB-ADA)

Layout

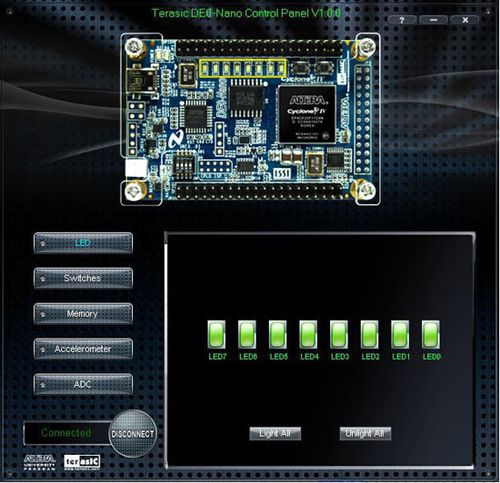

DE0-Nano Control Panel

DE0-Nano System Builder

Kit Contents

The DE0-Nano package includes:

Manufacturer BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Poland sprzedaz@kamami.pl 22 767 36 20

Responsible person BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Poland sprzedaz@kamami.pl 22 767 36 20

TerasIC DE0 is a complete evaluation kit based on the Cyclone III FPGA, designed for learning, testing, and implementing digital systems. It offers a wide range of interfaces and peripherals enabling the creation of complex projects for both educational and industrial purposes.

No product available!

[EDUCATIONAL PRICE] Terasic DE0 Board evaluation kit for Altera Cyclone III FPGA devices. It is equipped with all basic peripherals enabling research and evaluation work with FPGAs, including a JTAG programmer-configurator. The reduced price (compared to the standard Terasic DE0 version) applies exclusively to schools, universities, lecturers, pupils, and students.

No product available!

Altera DE0 NANO Development and Education Board introduces a compact-sized FPGA development platform suited for prototyping circuit designs such as robots and "portable" projects. The board is designed to be used in the simplest possible implementation targeting the Cyclone IV device up to 22,320 LEs.

The Terasic LT24 is a 2.4” LCD touch module with 240(H) x 320(V) display resolution. It can be bundled with various Terasic FPGA development boards through the 2x20 GPIO interface. P0185

The TerasIC AHA-HSMC card enables the integration of Aptina image sensors with TerasIC FPGA kits equipped with an HSMC interface. It provides full support for communication, data transmission, and shutter control, making it a key component in vision systems and real-time image processing projects.

No product available!

The TerasIC HDMI v1.4 (P0087) module enables the implementation of a complete HDMI transmit–receive chain in FPGA systems. With support for Full HD resolution, compliance with HDMI 1.4a, and included reference designs, it serves as a versatile solution for testing, learning, and deploying video transmission in embedded and multimedia applications.

No product available!

TerasIC TR4-530 (P0109) is an FPGA development kit featuring the Stratix IV GX device, offering high logic performance, high-speed DDR3 memory support, and extensive expandability through HSMC and PCIe connectors. The platform is designed for prototyping digital systems, PCI Express applications, and real-time data processing.

No product available!

TerasIC TR4-230 (P0107) provides a development platform based on the Stratix IV GX FPGA, featuring a wide range of interfaces and support for PCI Express projects and high-speed DDR3 memory. The solution is designed for communication systems, ASIC prototyping, and applications requiring high logic resource capacity.

No product available!

TerasIC CLR-HSMC (P0079) enables the integration of industrial cameras with a Camera Link interface into FPGA boards via the HSMC connector, supporting image transmission in base, medium, and dual base modes. The module is used in vision systems, production lines, and projects involving real-time image processing.

No product available!

TerasIC XSFP/SFP+HSMC (P0092) enables the development of 10G Ethernet systems based on the XAUI interface, featuring two SFP+ channels and a 156.25 MHz reference clock. Designed for integration with FPGA boards equipped with an HSMC connector — including Stratix IV GX and DE4 — the module is used in networking projects, data transmission applications, and high-throughput interface testing.

No product available!

2x16 LCD Module (No Backlight)

Stratix V GX FPGA Video Development System

No product available!

Cyclone V E FPGA Video Development System

No product available!

No product available!

The robust hardware design platform built around the Altera System-on-Chip (SoC) FPGA, which combines the latest dual-core Cortex-A9 embedded cores with industry-leading programmable logic for ultimate design flexibility. Users can now leverage the power of tremendous re-configurability paired with a high-performance, low-power processor system.

The Terasic LT24 is a 2.4” LCD touch module with 240(H) x 320(V) display resolution. It can be bundled with various Terasic FPGA development boards through the 2x20 GPIO interface. P0185

No product available!

DE1-SoC + 5 points multitouch display MTL2

MAX 10 10M50DAF484C6G with 50K LEs, DDR3 with ECC, QSPI Flash, MicroSD Card, Ethernet, Audio codec, HDMI RX, Acceleromter, ADC, DAC, 8-Mega pixel color camera and 7" 5-point touch screen. P0800

No product available!

![Terasic DE0-Nano [EDU] - zestaw startowy z układem FPGA z rodziny Cyclone IV firmy Altera Terasic DE0-Nano [EDU] - zestaw startowy z układem FPGA z rodziny Cyclone IV firmy Altera](https://kamami.pl/4338-large_default/terasic-de0-nano-p0082-edu.jpg)

Altera DE0 NANO Development and Education Board introduces a compact-sized FPGA development platform suited for prototyping circuit designs such as robots and "portable" projects. The board is designed to be used in the simplest possible implementation targeting the Cyclone IV device up to 22,320 LEs.