1 415,83 zł Netto

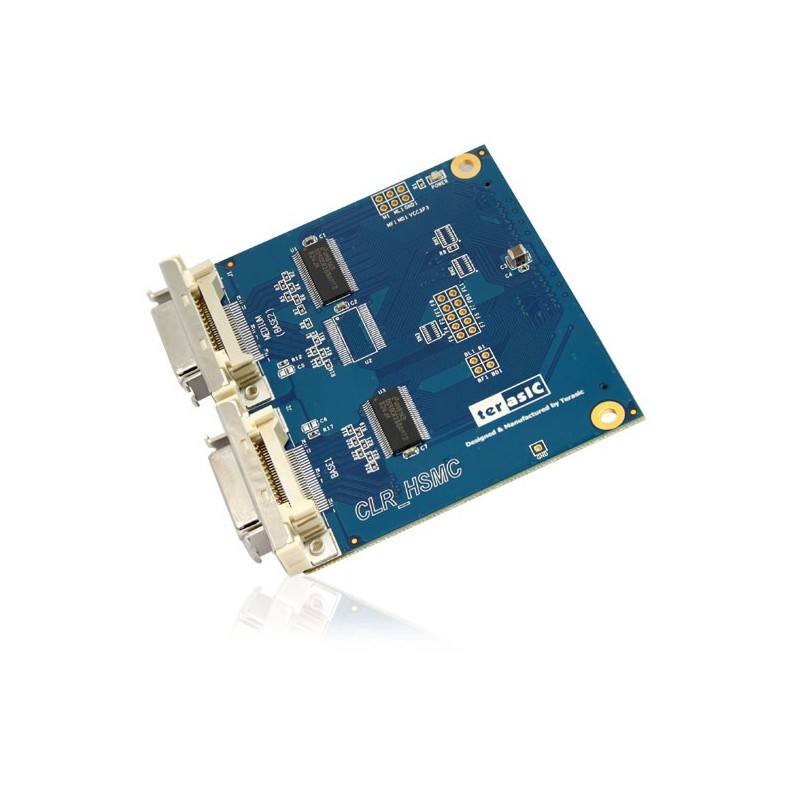

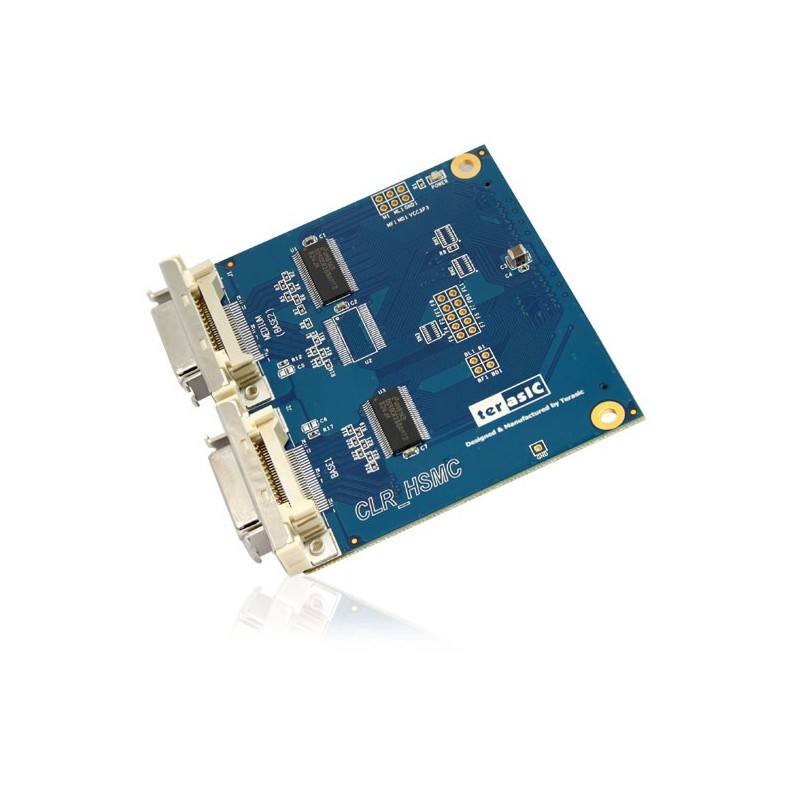

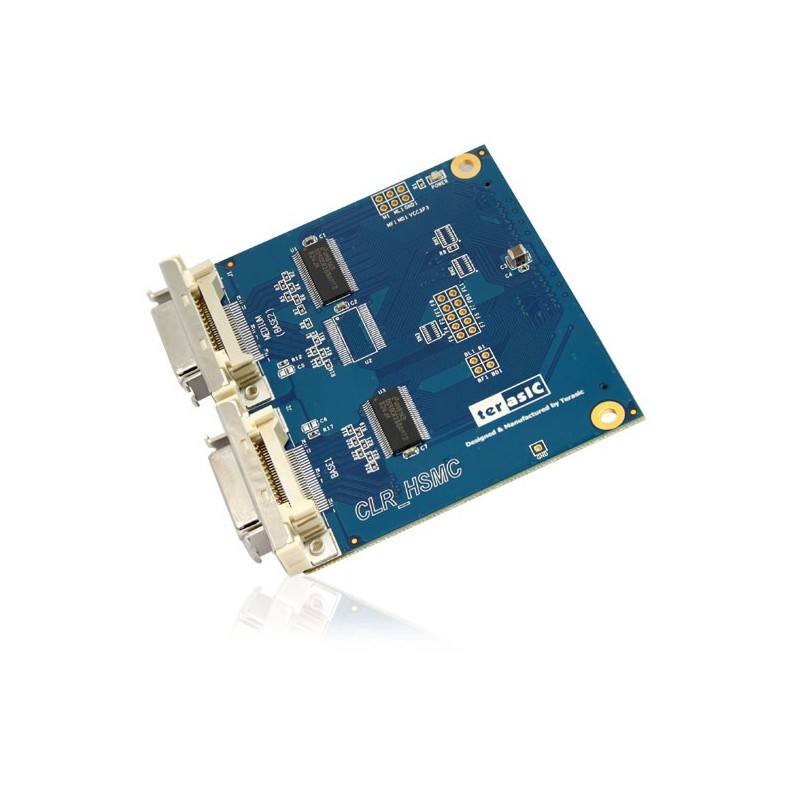

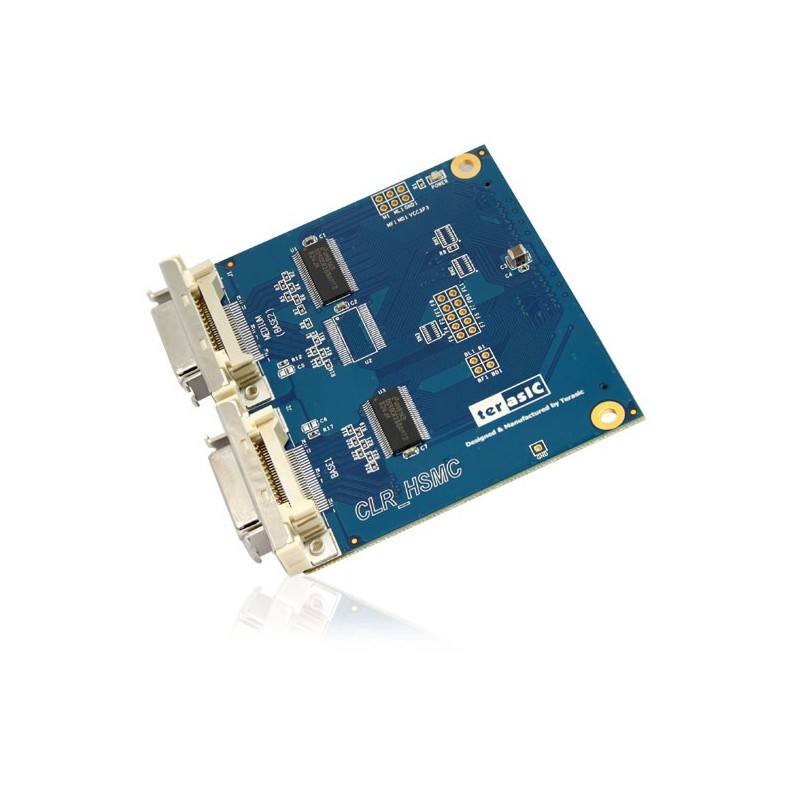

TerasIC CLR-HSMC (P0079) umożliwia integrację kamer przemysłowych z interfejsem Camera Link z płytami FPGA przez złącze HSMC, wspierając przesył obrazu w trybach base, medium i dual base. Moduł znajduje zastosowanie w systemach wizyjnych, liniach produkcyjnych oraz projektach z przetwarzaniem obrazu w czasie rzeczywistym.

Moduł rozszerzeń CLR-HSMC umożliwia bezpośrednie podłączenie kamer przemysłowych z interfejsem Camera Link do płyt rozwojowych wyposażonych w złącze HSMC, takich jak DE4, DE3 czy DE2-115. Obsługuje standardowe tryby Camera Link: base, medium oraz dual base assembly, zapewniając komunikację szeregową i automatyczne wykrywanie urządzenia przez sprzęt i oprogramowanie.

Moduł oparty został na dwóch układach DS90CR288A, wspierających transmisję LVDS w standardzie 28-bitowym z zegarem przesuwającym w zakresie od 20 do 85 MHz. Maksymalna przepustowość transmisji wynosi 2,38 Gb/s, co odpowiada 297,5 MB/s. Obsługiwane poziomy napięć interfejsów to 2,5 V i 3,3 V, co pozwala na integrację z szeroką gamą systemów.

CLR-HSMC współpracuje z płytami DE4 i DE3 poprzez adaptery HMF2 i HFF (dołączane odpowiednio do zestawów DE4 i DE3). Dzięki prostemu interfejsowi oraz gotowym projektom referencyjnym dla platform TerasIC, moduł znajduje zastosowanie w systemach wizyjnych i aplikacjach przemysłowych wymagających wysokiej jakości transmisji obrazu.

Producent BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Terasic DE1-SoC-MTL2 to rozbudowana i sprawdzona platforma dla inżynierów, studentów i zespołów R&D, którzy potrzebują wydajnego SoC FPGA z dotykowym interfejsem graficznym. Idealna do projektów, w których liczy się połączenie elastyczności FPGA z wygodą systemu Linux i nowoczesnym HMI.

Płyta bazowa FPGA z układem FPGA z rodziny MAX10 z 7", 5-punktowym wyświetlaczem multidotykowym. Oparty na układzie 10M50DAF484C6G. 512 Mb pamięci Flash, gniazdo miroSD, wejście Audio, Video, zasilanie 5 V/3 A.

Brak towaru

Terasic Spider to sześcionożny robot kroczący z 18 serwomechanizmami sterowanymi przez płytkę Altera DE0-Nano-SoC łączącą układ FPGA oraz procesor ARM Cortex-A9. Zestaw zawiera złożonego robota oraz liczne akcesoria. P0425

A-Cute Car Robotic Kit to kompletne 3-kołowe podwozie robota mobilnego wraz ze sterownikiem opartym o układ FPGA do samodzielnego programowania. P0467

Brak towaru

Terasic DE10-Lite Board to niskobudżetowa płytka deweloperska z układem FPGA Altera MAX 10. Płyta zawiera szereg komponentów umożliwiających naukę oraz tworzenie prototypów projektów opartych o układy FPGA. Terasic P0466

Terasic DE10-Lite Board to niskobudżetowa płytka deweloperska z układem FPGA Altera MAX 10. Płyta zawiera szereg komponentów umożliwiających naukę oraz tworzenie prototypów projektów opartych o układy FPGA

Sterownik serwomechanizmów do zestawów FPGA TerasIC serii DE umożliwia sterowanie maksymalnie 24 serwomechanizmami. Dostarcza napięcie 6 V do zasilania serwomechanizmów. W zestawie serwomechanizm MG966R i taśma do połączenia z zestawem FPGA. P0288

Moduł z kamerą przeznaczony do użycia z zestawami Terasic. Kamera posiada przetwornik o rozdzielczości 8 Megapikseli (3264 x 2448), do komunikacji wykorzystuje interfejs MIPI. Na module znalazł się również dekoder MIPI oraz układ HDMI-TX. Terasic P0449

Brak towaru

Zestaw startowy VEEK-MT2-C5SoC z układem System-on-Chip z rodziny Cyclone V SX SoC. W zestawie 7-calowy wyświetlacz, 8 megapikselową kamerę z autofocusem, czujnik światła, żyroskop, magnetometr oraz 3 osiowy akcelerometr. Terasic K0160

Brak towaru

Terasic ADC-SoC to płyta rozwojowa z układem programowalnym FPGA oraz dwukanałowym szybkim przetwornikiem ADC. Płyta bazuje na module Terasic DE0-Nano-SoC. Wbudowany przetwornik ADC wykorzystuje SMA jako interfejs wejściowy, posiada dwa kanały, oferuje rozdzielczość 14-bitową, i szybkość próbkowania do 150 MSPS Megasamples per Second). Terasic (P0435)

Brak towaru

Zestaw elementów przeznaczony dla zestawów ewaluacyjnych z układami programowalnymi z rodziny Cyclone V SoC FPGA, w którego skład wchodzą; 7-calowy wyświetlacz TFT z obsługą dotyku (5-punktów), 8 megapikselowa kamera z autofocusem oraz czujniki (światła, akcelerometr, żyroskop, magnetometr). Terasic P0494

Brak towaru

Terasic HDMI-FMC to karta rozszerzająca układy ewaluacyjny o możliwość wyświetlania oraz odbierania obrazu wideo przy pomocy złącz HDMI. Pozwalają wyświetlać obraz w rozdzielczości 4K@30FPS. Wspiera HDMI 1.4a. Terasic P0431

Terasic NET-FMC to karta rozszerzająca z Gigabajtowym Ethernetem oraz interfejsem FMC. Dzięki temu interfejsowi może być używana z zestawami firmy Terasic. Terasic P0481

Brak towaru

Zestaw startowy DE10-Standard z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. P0493

Zestaw startowy DE10-Standard z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. P0493

Brak towaru

Zestaw startowy DE10-Nano Kit z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. Terasic P0496

Brak towaru

TerasIC CLR-HSMC (P0079) umożliwia integrację kamer przemysłowych z interfejsem Camera Link z płytami FPGA przez złącze HSMC, wspierając przesył obrazu w trybach base, medium i dual base. Moduł znajduje zastosowanie w systemach wizyjnych, liniach produkcyjnych oraz projektach z przetwarzaniem obrazu w czasie rzeczywistym.