324,59 zł Netto

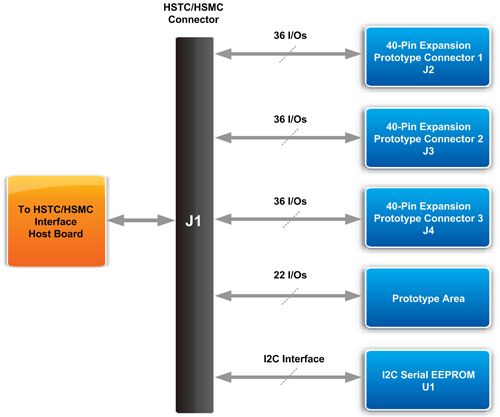

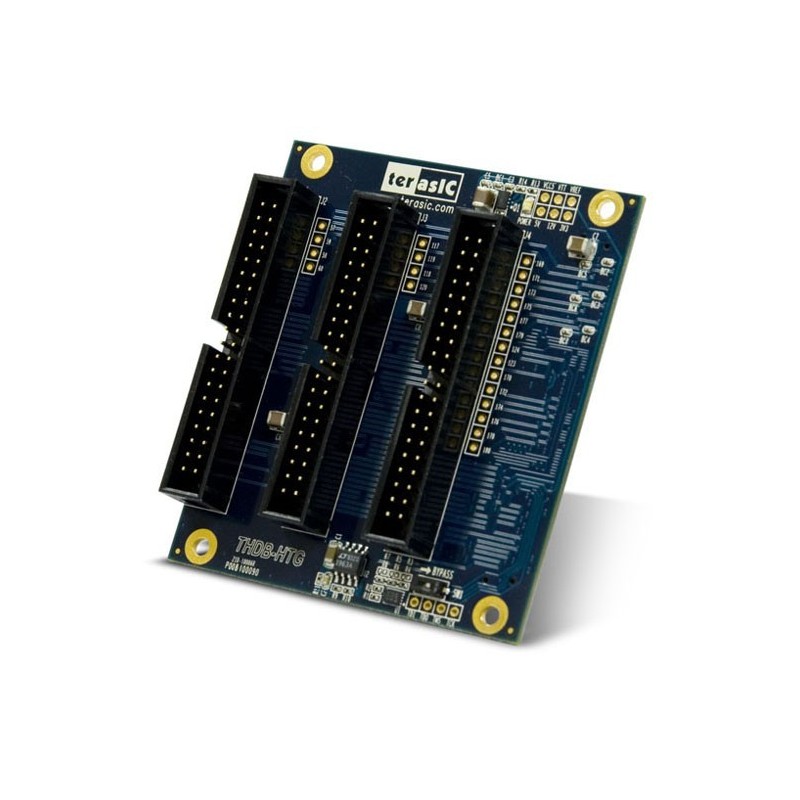

Karta HTG-M przeznaczona jest dla zestawów ewaluacyjnych z układami FPGA, które zostały wyposażone w złącze HSMC (High-Speed Mezzanine connector) lub HSTC (High-Speed Terasic Connector). Karta HTG posiada trzy złącza męskie (40-pinowe). Pozwala na konwersje wejść/wyjść HSMC do dwóch 40-pinowych złącz prototypowych lub złącza HSTC do trzech 40-pinowych złącz prototypowych. TerasIC P0033

Karta HTG-M przeznaczona jest dla zestawów ewaluacyjnych z układami FPGA, które zostały wyposażone w złącze HSMC (High-Speed Mezzanine connector) lub HSTC (High-Speed Terasic Connector). Karta HTG posiada trzy złącza męskie (40-pinowe). Pozwala na konwersje wejść/wyjść HSMC do dwóch 40-pinowych złącz prototypowych lub złącza HSTC do trzech 40-pinowych złącz prototypowych.

Producent BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Karta HTG-M przeznaczona jest dla zestawów ewaluacyjnych z układami FPGA, które zostały wyposażone w złącze HSMC (High-Speed Mezzanine connector) lub HSTC (High-Speed Terasic Connector). Karta HTG posiada trzy złącza żeńskie (40-pinowe). Pozwala na konwersje wejść/wyjść HSMC do dwóch 40-pinowych złącz prototypowych lub złącza HSTC do trzech 40-pinowych złącz prototypowych. TerasIC P0024

TerasIC XSFP/SFP+HSMC (P0092) umożliwia budowę systemów Ethernet 10G opartych na interfejsie XAUI z dwoma kanałami SFP+ i zegarem referencyjnym 156,25 MHz. Moduł przeznaczony do integracji z płytami FPGA posiadającymi złącze HSMC, m.in. Stratix IV GX i DE4, znajduje zastosowanie w projektach sieciowych, transmisji danych oraz testach interfejsów wysokiej przepustowości.

Brak towaru

Zestaw rozwojowy z układem SoC FPGA Intel Arria 10. Dedykowany do przemysłowych aplikacji wbudowanych o wysokich wymaganiach wydajności. Terasic P0506

Brak towaru

Zestaw startowy DE10-Nano Kit z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. Terasic P0496

TerasIC DVI-HSMC to karta rozszerzeń FPGA z nadajnikiem i odbiornikiem DVI, umożliwiająca obsługę wysokorozdzielczych sygnałów wideo w projektach multimedialnych i systemach przetwarzania obrazu. Dzięki zgodności z platformami Terasic i Altera oferuje szybkie wdrożenie i testowanie aplikacji wizualnych w oparciu o układy FPGA.

MAX 10 Plus jest zestawem deweloperskim opartym o układ FPGA od Intela, wyposażony w 50 000 programowalnych elementów logicznych. Digilent P0638

Brak towaru

Zestaw deweloperski z modułem Apollo S10 oraz płytą bazową. Wyposażony w procesor Intel Stratix 10 SoC z elementami logicznymi 2800K, posiada pamięć DDR4 SDRAM (do 64 GB), wbudowany USB-Blaster II, Ethernet, microSD, miniUSB oraz złącza QSFP i USB typ C. TerasIC Apollo Developer Kit (P0671)

Brak towaru

Terasic DE10-Lite Board to niskobudżetowa płytka deweloperska z układem FPGA Altera MAX 10. Płyta zawiera szereg komponentów umożliwiających naukę oraz tworzenie prototypów projektów opartych o układy FPGA

Kompaktowy zestaw FPGA z układem Intel Arria 10 GX wyposażony w 8 GB pamięci DDR4-2133 oraz złącze komunikacyjne Thunderbolt 3. Może być zastosowany bezpośrednio na laptopach lub innych urządzeniach przenośnych. Wersja edukacyjna. Terasic FLIK P0642

Brak towaru

TerasIC INK to kompleksowa platforma sprzętowa do tworzenia i testowania aplikacji przemysłowych opartych na FPGA, oferująca pełną obsługę komunikacji szeregowej i Ethernetu przemysłowego. Zestaw pozwala na szybki rozwój rozwiązań automatyki i transmisji danych w środowiskach wymagających wysokiej niezawodności.

Brak towaru

Cyclone V E FPGA Video Development System

Brak towaru

Moduł TerasIC HDMI v1.4 (P0087) umożliwia implementację pełnego toru nadawczo-odbiorczego HDMI w systemach FPGA. Dzięki obsłudze rozdzielczości Full HD, zgodności z HDMI 1.4a oraz dołączonym projektom referencyjnym, stanowi uniwersalne rozwiązanie do testowania, nauki i wdrażania transmisji wideo w aplikacjach embedded i multimedialnych.

Brak towaru

Moduł TerasIC HDMI_RX P0083 umożliwia odbiór sygnałów HDMI przez interfejs HSMC w systemach FPGA. Dzięki zgodności ze standardami HDMI i HDCP oraz dostępnemu projektowi referencyjnemu, stanowi kompletne rozwiązanie do implementacji, testowania i analizy transmisji wideo w aplikacjach wbudowanych i systemach przetwarzania obrazu.

Brak towaru

TerasIC XTS-HSMC to karta rozszerzeń dla platform FPGA z transceiverami, umożliwiająca konwersję sygnałów na złącza SMA i szybkie prototypowanie interfejsów wysokiej przepustowości. Sprawdza się w testach zgodności, ocenie jakości transmisji oraz projektach wymagających niezawodnego przesyłu danych z prędkościami gigabitowymi.

Brak towaru

TerasIC DE0 to kompletny zestaw ewaluacyjny oparty na FPGA Cyclone III, zaprojektowany do nauki, testowania i wdrażania systemów cyfrowych. Oferuje szeroki zestaw interfejsów i peryferiów umożliwiających tworzenie złożonych projektów zarówno edukacyjnych, jak i przemysłowych.

Brak towaru

Adapter przeznaczony do łączenia płytek ze złączem PCIe z komputerem. Może obsługiwać interfejs PCIe Gen3 x4. Terasic P0492

Robot może rozpoznawać postawę w czasie rzeczywistym za pomocą czujnika przyspieszenia i żyroskopu, a także osiągnąć równowagę poprzez sterowanie silnikami w celu regulacji pozycji. Terasic P0582

Brak towaru

Karta HTG-M przeznaczona jest dla zestawów ewaluacyjnych z układami FPGA, które zostały wyposażone w złącze HSMC (High-Speed Mezzanine connector) lub HSTC (High-Speed Terasic Connector). Karta HTG posiada trzy złącza męskie (40-pinowe). Pozwala na konwersje wejść/wyjść HSMC do dwóch 40-pinowych złącz prototypowych lub złącza HSTC do trzech 40-pinowych złącz prototypowych. TerasIC P0033