15 259,65 zł Netto

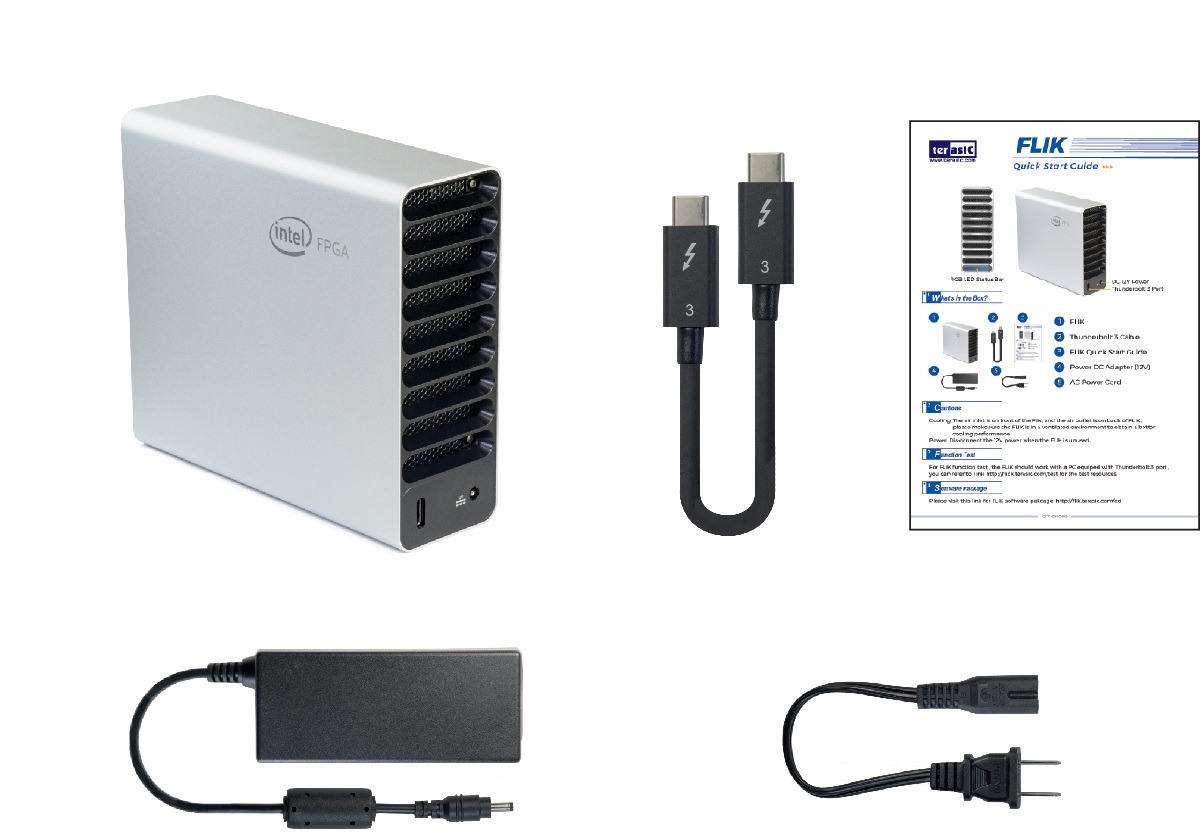

Kompaktowy zestaw FPGA z układem Intel Arria 10 GX wyposażony w 8 GB pamięci DDR4-2133 oraz złącze komunikacyjne Thunderbolt 3. Może być zastosowany bezpośrednio na laptopach lub innych urządzeniach przenośnych. Wersja edukacyjna. Terasic FLIK P0642

Oferta przeznaczona wyłącznie dla odbiorców akademickich (studentów i wykładowców wyższych uczelni)!

Składając zamówienie należy podać:

- imię i nazwisko użytkownika

- stanowisko

- adres e-mail użytkownika (adres e-mail musi być z domeny uczelni)

- pełną nazwę uczelni

- nazwę wydziału/instytutu/zakładu dydaktycznego

- adres uczelni

- stronę internetową uczelni

- telefon

- zastosowanie produktu

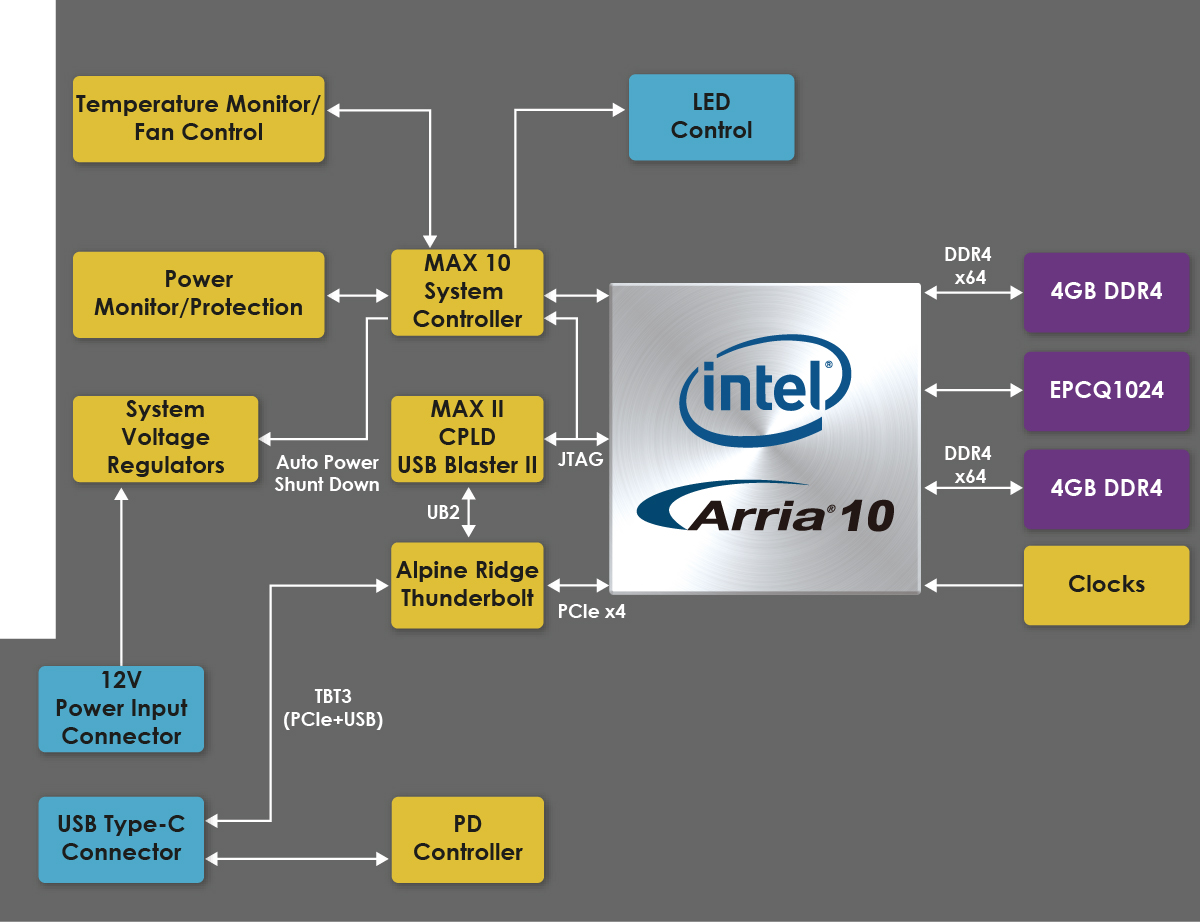

FLIK to kompaktowy zestaw FPGA firmy TerasIC z układem Intel Arria 10 GX. Jest to uniwersalny projekt akceleratora do przyspieszania krytycznych obliczeń, takich jak analiza danych, głębokie uczenie się i algorytmy uczenia maszynowego. Może być zastosowany bezpośrednio na laptopach lub innych urządzeniach przenośnych.

FLIK wykorzystuje potężny procesor Intel Arria 10 FPGA, co umożliwia szybsze przetwarzanie danych. Zestaw jest wyposażony w 8 GB pamięci DDR4-2133 oraz złącze komunikacyjne Thunderbolt 3.

Zestaw posiada szerokie wsparcie w postaci narzędzi takich jak Intel Open VINO Toolkit, Intel Acceleration Stack i OpenCL zarówno w wersji Linux, jak i Windows.

Producent BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

TerasIC DE0 to kompletny zestaw ewaluacyjny oparty na FPGA Cyclone III, zaprojektowany do nauki, testowania i wdrażania systemów cyfrowych. Oferuje szeroki zestaw interfejsów i peryferiów umożliwiających tworzenie złożonych projektów zarówno edukacyjnych, jak i przemysłowych.

Brak towaru

[CENA EDUKACYJNA] Zestaw ewaluacyjny Terasic DE0 Board dla układów FPGA Cyclone III firmy Altera. Wyposażono go we wszystkie podstawowe peryferia umożliwiające prowadzenie prac badawczych i ewaluacyjnych z układami FPGA, w tym programator-konfigurator JTAG. Obniżona cena (w stosunku do klasycznej wersji Terasic DE0) dotyczy wyłącznie szkół, uczelni, wykładowców, uczniów i studentów.

Zestaw startowy DE10-Nano Kit z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. Terasic P0496

Brak towaru

Zestaw startowy DE10-Nano Kit z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. Terasic P0496

Kompaktowy zestaw FPGA z układem Intel Arria 10 GX wyposażony w 8 GB pamięci DDR4-2133 oraz złącze komunikacyjne Thunderbolt 3. Może być zastosowany bezpośrednio na laptopach lub innych urządzeniach przenośnych. Terasic FLIK P0642

Brak towaru

TerasIC SDI HSMC to specjalistyczny moduł dla projektów FPGA w obszarze transmisji wideo, oferujący wsparcie dla standardów SDI i AES oraz pełną kompatybilność z platformami HSMC. Idealny do rozwoju rozwiązań nadawczych, analizatorów sygnału i profesjonalnych aplikacji wideo.

TerasIC INK to kompleksowa platforma sprzętowa do tworzenia i testowania aplikacji przemysłowych opartych na FPGA, oferująca pełną obsługę komunikacji szeregowej i Ethernetu przemysłowego. Zestaw pozwala na szybki rozwój rozwiązań automatyki i transmisji danych w środowiskach wymagających wysokiej niezawodności.

Brak towaru

TerasIC DE0 to kompletny zestaw ewaluacyjny oparty na FPGA Cyclone III, zaprojektowany do nauki, testowania i wdrażania systemów cyfrowych. Oferuje szeroki zestaw interfejsów i peryferiów umożliwiających tworzenie złożonych projektów zarówno edukacyjnych, jak i przemysłowych.

Brak towaru

[CENA EDUKACYJNA] Zestaw ewaluacyjny Terasic DE0 Board dla układów FPGA Cyclone III firmy Altera. Wyposażono go we wszystkie podstawowe peryferia umożliwiające prowadzenie prac badawczych i ewaluacyjnych z układami FPGA, w tym programator-konfigurator JTAG. Obniżona cena (w stosunku do klasycznej wersji Terasic DE0) dotyczy wyłącznie szkół, uczelni, wykładowców, uczniów i studentów.

TerasIC SATA/SAS HSMC to specjalistyczna karta rozszerzeń umożliwiająca implementację i testowanie interfejsów pamięci masowych w systemach FPGA. Dzięki obsłudze protokołów SATA i SAS oraz kompatybilności z zaawansowanymi układami FPGA, stanowi narzędzie do tworzenia aplikacji przechowywania danych, testowania zgodności i rozwoju systemów typu SoC.

Brak towaru

TerasIC XTS-HSMC to karta rozszerzeń dla platform FPGA z transceiverami, umożliwiająca konwersję sygnałów na złącza SMA i szybkie prototypowanie interfejsów wysokiej przepustowości. Sprawdza się w testach zgodności, ocenie jakości transmisji oraz projektach wymagających niezawodnego przesyłu danych z prędkościami gigabitowymi.

Brak towaru

TerasIC AD/DA Data Conversion Card to uniwersalna karta konwersji danych analogowo-cyfrowych i cyfrowo-analogowych przeznaczona do systemów FPGA. Dzięki wysokiej szybkości próbkowania i wbudowanemu kodekowi audio doskonale sprawdza się w aplikacjach DSP, telekomunikacyjnych i edukacyjnych.

Brak towaru

TerasIC ADA-HSMC to wydajna karta konwersji AD/DA dla systemów FPGA, oferująca wysoką precyzję i elastyczność w aplikacjach DSP oraz komunikacyjnych. Dzięki wsparciu interfejsów HSMC i GPIO zapewnia szeroką kompatybilność z płytami rozwojowymi Terasic i Altera, umożliwiając szybki rozwój systemów przetwarzania sygnałów.

Brak towaru

Karta HTG-M przeznaczona jest dla zestawów ewaluacyjnych z układami FPGA, które zostały wyposażone w złącze HSMC (High-Speed Mezzanine connector) lub HSTC (High-Speed Terasic Connector). Karta HTG posiada trzy złącza żeńskie (40-pinowe). Pozwala na konwersje wejść/wyjść HSMC do dwóch 40-pinowych złącz prototypowych lub złącza HSTC do trzech 40-pinowych złącz prototypowych. TerasIC P0024

TerasIC DVI-HSMC to karta rozszerzeń FPGA z nadajnikiem i odbiornikiem DVI, umożliwiająca obsługę wysokorozdzielczych sygnałów wideo w projektach multimedialnych i systemach przetwarzania obrazu. Dzięki zgodności z platformami Terasic i Altera oferuje szybkie wdrożenie i testowanie aplikacji wizualnych w oparciu o układy FPGA.

TerasIC ICB-HSMC to karta komunikacyjna dla systemów FPGA, wyposażona w interfejsy RS-232, RS-485 i CAN, a także porty GPIO i PIO do rozbudowy. Umożliwia szybkie wdrażanie i testowanie systemów komunikacji przemysłowej oraz implementację magistral polowych w aplikacjach automatyki i sterowania.

Brak towaru

TerasIC NET to moduł Ethernet w standardzie HSMC, umożliwiający szybkie wdrożenie komunikacji sieciowej w systemach FPGA. Dzięki obsłudze prędkości od 10 Mb/s do 1 Gb/s oraz pełnej integracji z układami FPGA stanowi wygodne narzędzie do projektowania aplikacji wymagających niezawodnej komunikacji sieciowej.

Brak towaru

TerasIC USB Blaster Download Cable (UBT) to w pełni zgodny z Altera USB Blaster programator JTAG/ISP dla układów CPLD i FPGA. Dzięki niezawodnej konstrukcji oraz odporności na zakłócenia stanowi uniwersalne narzędzie dla projektantów pracujących z układami programowalnymi Altera. TerasIC P0302

TerasIC ADA-GPIO to karta konwersji AD/DA umożliwiająca współpracę z wieloma płytami FPGA przez interfejsy GPIO i HSMC. Dzięki wysokiej szybkości próbkowania oraz szerokiej kompatybilności doskonale nadaje się do zastosowań DSP, edukacyjnych i komunikacyjnych.

Brak towaru

Karta HTG-M przeznaczona jest dla zestawów ewaluacyjnych z układami FPGA, które zostały wyposażone w złącze HSMC (High-Speed Mezzanine connector) lub HSTC (High-Speed Terasic Connector). Karta HTG posiada trzy złącza męskie (40-pinowe). Pozwala na konwersje wejść/wyjść HSMC do dwóch 40-pinowych złącz prototypowych lub złącza HSTC do trzech 40-pinowych złącz prototypowych. TerasIC P0033

Zestaw TerasIC P0057 umożliwia testowanie, debugowanie i symulację sygnałów w systemach wykorzystujących interfejs HSMC. Przeznaczony do prac projektowych i diagnostycznych z płytami głównymi FPGA i innymi układami wyposażonymi w złącze HSMC.

Brak towaru

Kompaktowy zestaw FPGA z układem Intel Arria 10 GX wyposażony w 8 GB pamięci DDR4-2133 oraz złącze komunikacyjne Thunderbolt 3. Może być zastosowany bezpośrednio na laptopach lub innych urządzeniach przenośnych. Wersja edukacyjna. Terasic FLIK P0642