313,00 zł Netto

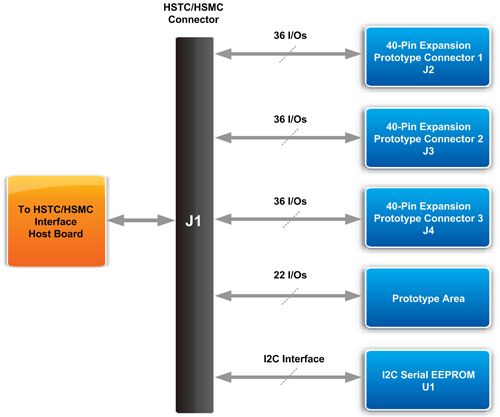

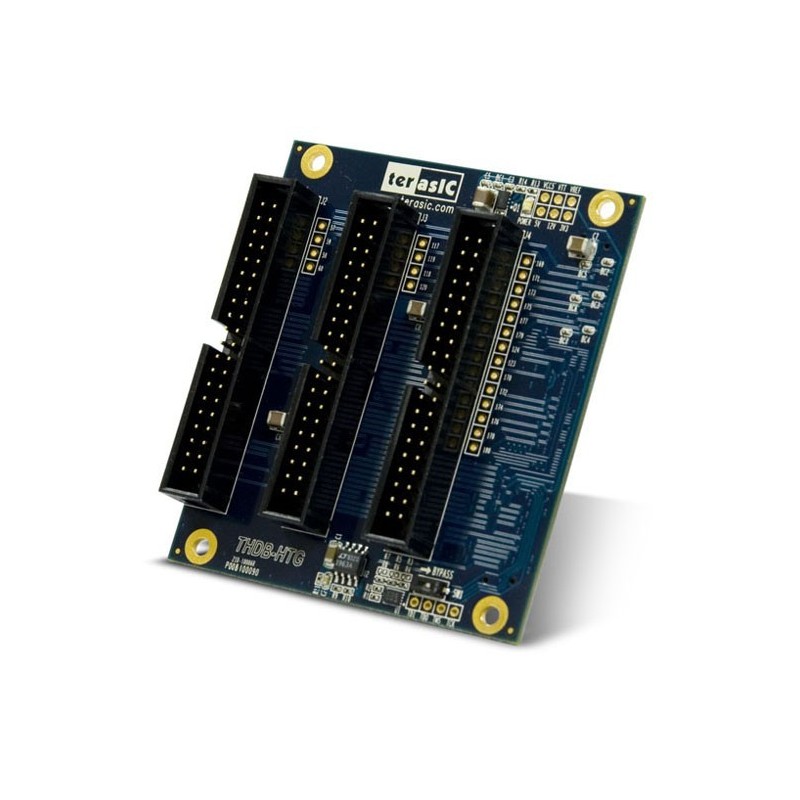

Karta HTG-M przeznaczona jest dla zestawów ewaluacyjnych z układami FPGA, które zostały wyposażone w złącze HSMC (High-Speed Mezzanine connector) lub HSTC (High-Speed Terasic Connector). Karta HTG posiada trzy złącza żeńskie (40-pinowe). Pozwala na konwersje wejść/wyjść HSMC do dwóch 40-pinowych złącz prototypowych lub złącza HSTC do trzech 40-pinowych złącz prototypowych. TerasIC P0024

Karta HTG-M przeznaczona jest dla zestawów ewaluacyjnych z układami FPGA, które zostały wyposażone w złącze HSMC (High-Speed Mezzanine connector) lub HSTC (High-Speed Terasic Connector). Karta HTG posiada trzy złącza żeńskie (40-pinowe). Pozwala na konwersje wejść/wyjść HSMC do dwóch 40-pinowych złącz prototypowych lub złącza HSTC do trzech 40-pinowych złącz prototypowych.

Uwaga!

Moduł posiada trzy złącza żeńskie pomimo że zdjęciu znajdują się złącza męskie. W sprzedaży znajduje się moduł z złączami męskimi: TerasIC HTG_M (P0033)

Producent BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Karta HTG-M przeznaczona jest dla zestawów ewaluacyjnych z układami FPGA, które zostały wyposażone w złącze HSMC (High-Speed Mezzanine connector) lub HSTC (High-Speed Terasic Connector). Karta HTG posiada trzy złącza męskie (40-pinowe). Pozwala na konwersje wejść/wyjść HSMC do dwóch 40-pinowych złącz prototypowych lub złącza HSTC do trzech 40-pinowych złącz prototypowych. TerasIC P0033

Zestaw z płytką FPGA Terasic DE10-Nano oraz modułem WiFi. Przeznaczony do projektów wykorzystujących FPGA do pracy w chmurze. TerasIC P0700

Brak towaru

Moduł akceleratora obliczeń oparty na układzie FPGA Intel® Agilex™. Ma gniazdo PCI Express Gen 4.0 x16, dwa złącza 200G QSFP-DD i oferuje 32 GB DDR4. Terasic DE10-Agilex (P0701)

Brak towaru

Moduł ewaluacyjny z procesorem Intel Stratix 10 SoC z elementami logicznymi 2800K. Moduł posiada pamięć DDR4 SDRAM (do 64 GB), wbudowany USB-Blaster II, Ethernet, microSD, miniUSB oraz złącza FMC/FMC+ do rozbudowy. TerasIC Apollo S10 SoM Board (P0630)

Brak towaru

[CENA EDUKACYJNA] Zestaw startowy/ewaluacyjny Terasic DE0-Nano Board dla układów FPGA Cyclone IV firmy Altera. Jeden z najmniejszych i najprostszych zestawów startowych dla układów FPGA, wyposażony w podstawowe peryferia, w tym programator-konfigurator JTAG.Obniżona cena (w stosunku do klasycznej wersji Terasic DE0-Nano) dotyczy wyłącznie szkół, uczelni, wykładowców, uczniów i studentów. P0082

Zestaw startowy/ewaluacyjny Terasic DE0-Nano Board dla układów FPGA Cyclone IV firmy Altera. Jest to jeden z najmniejszych i najprostszych i jednocześnie dobrze wyposażonych zestawów startowych dla układów FPGA, jego standardowym wyposażeniem jest programator-konfigurator JTAG.

Brak towaru

TerasIC TR4-230 (P0107) oferuje platformę rozwojową opartą na FPGA Stratix IV GX z szerokim zakresem interfejsów oraz wsparciem dla projektów PCI Express i szybkiej pamięci DDR3. Rozwiązanie przeznaczone do budowy systemów komunikacyjnych, prototypowania ASIC oraz aplikacji o wysokim zapotrzebowaniu na zasoby logiczne.

Brak towaru

Płytka ewaluacyjna z układem Intel Agilex SoC z 1400 tys. elementów logicznych. Moduł ma gniazda z wbudowaną pamięcią DDR4 SO-DIMM o pojemności 32 GB, złącze QSFP28, PCIe Gen 4x16, wbudowany USB-Blaster II oraz złącza FMC/FMC+ do rozbudowy. TerasIC Apollo Agilex SOM (P0795)

Brak towaru

Moduł XTS-FMC jest rozszerzeniem dla układów FPGA pozwalającym na dostęp do kanałów/interfejsów komunikacyjnych poprzez złącze SMA. TerasIC P0401

Brak towaru

Robot może rozpoznawać postawę w czasie rzeczywistym za pomocą czujnika przyspieszenia i żyroskopu, a także osiągnąć równowagę poprzez sterowanie silnikami w celu regulacji pozycji. Terasic P0582

Brak towaru

TerasIC AD/DA Data Conversion Card to uniwersalna karta konwersji danych analogowo-cyfrowych i cyfrowo-analogowych przeznaczona do systemów FPGA. Dzięki wysokiej szybkości próbkowania i wbudowanemu kodekowi audio doskonale sprawdza się w aplikacjach DSP, telekomunikacyjnych i edukacyjnych.

Brak towaru

A-Cute Car Robotic Kit to kompletne 3-kołowe podwozie robota mobilnego wraz ze sterownikiem opartym o układ FPGA do samodzielnego programowania. P0467

Brak towaru

Zestaw startowy FPGA z układem Intel Stratix 10 SX. Moduł posiada zintegrowane urządzenia nadawczo-odbiorcze, które przesyłają dane z prędkością do 28,3 Gb/s, dzięki czemu DE10-Pro jest w pełni zgodny z wersją 3.0 standardu PCI Express. DE10-Pro oferuje szybką pamięć równoległą Flash i cztery pamięci SO-DIMM, które mają 8 GB DDR4 SDRAM. Terasic P0629

Brak towaru

Stratix V GX FPGA Video Development System

Brak towaru

TerasIC USB Blaster Download Cable (UBT) to w pełni zgodny z Altera USB Blaster programator JTAG/ISP dla układów CPLD i FPGA. Dzięki niezawodnej konstrukcji oraz odporności na zakłócenia stanowi uniwersalne narzędzie dla projektantów pracujących z układami programowalnymi Altera. TerasIC P0302

Cyclone V E FPGA Video Development System

Brak towaru

Karta HTG-M przeznaczona jest dla zestawów ewaluacyjnych z układami FPGA, które zostały wyposażone w złącze HSMC (High-Speed Mezzanine connector) lub HSTC (High-Speed Terasic Connector). Karta HTG posiada trzy złącza żeńskie (40-pinowe). Pozwala na konwersje wejść/wyjść HSMC do dwóch 40-pinowych złącz prototypowych lub złącza HSTC do trzech 40-pinowych złącz prototypowych. TerasIC P0024