- Obecnie brak na stanie

Overview

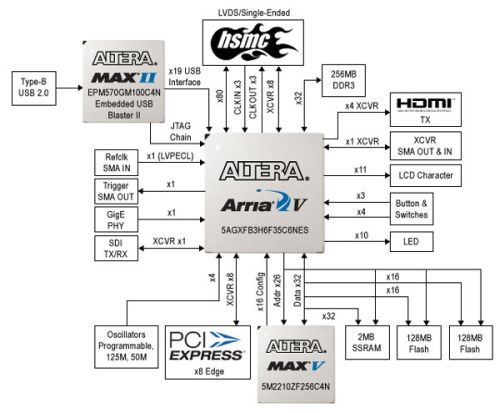

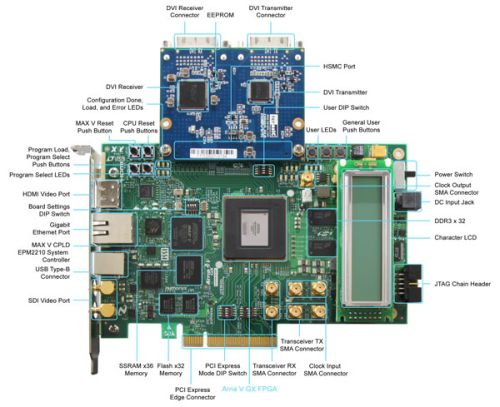

The Arria V GX FPGA Video Development System is an ideal video processing platform for high-performance, cost-effective video applications. The Arria II development kit features 256MB of SDRAM memory, HDMI, and SDI connections to form a perfect solution for imaging applications.

The DVI-HSMC daughter card part of the bundled package will allow developers to access high quality and high resolution video signals that can support resolution up to 1600x1200. A complete DVI video controller design with source code is provided.

Terasic recognized for its strong design expertise in high-end video, imaging and multimedia products have made available a video development package that targets video processing development. The platform can also allow users to experience advanced image processing designs incorporating VIP (Altera’s Video and Image Processing Suite MegaCore Functions).

Specification

Altera Arria V GX Video Development System

Terasic DVI-HSMC Card

Layout

Resources

Demo

DVI Video Development System Bundle

The Terasic DVI Development System bundles together the DVI daughter card and Altera development kit for cost-effective video development. All source code shown is included.

Code: K0111

Producent BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Kabel z wtykami USB typ A oraz micro-USB typ B, kabel o długości 1m. Kabel ma pomarańczowy nylonowy oplot

Brak towaru

Kabel z wtykami USB typ A oraz micro-USB typ B, kabel o długości 1m. Kabel ma zielony nylonowy oplot

Brak towaru

Kabel z wtykami USB typ A oraz micro-USB typ B, kabel o długości 1m. Kabel ma ciemno-różowy nylonowy oplot

Brak towaru

Brak towaru

Płytka z otworami prototypowymi przeznaczona do minikomputerów BeagleBone Black. SparkFun DEV-12774

Brak towaru

Brak towaru

Brak towaru

Moduł DIP z mikrokontrolerem ATmega128A, kwarc 16 MHz. Idealnie pasuje do zestawu ZL8AVR

Brak towaru

Brak towaru

Stacja lutownicza hotair 100-480 °C, lutownica grotowa 75W 200-480 °C. Ustawienia wyświetlane są na wyświetlaczach LED

Brak towaru

Stacja lutownicza 5w1: hotair 100..480 st. C, lutownica grotowa 75W, zasilacz serwisowy 0..15V/1A, tester sygnału RF, miernik napięcia. W zestawie m.in. komplet dysz oraz przewody do zasilacza

Brak towaru

Brak towaru

Brak towaru

Zasilacz laboratoryjny KA3005P z programowalną pamięcią, regulacją napięcia 0–30 V i prądu 0–5 A, oferuje pracę w trybach C.V. i C.C. oraz zabezpieczenia OVP i OCP. Umożliwia zapis 5 ustawień parametrów oraz ich zdalną obsługę przez USB i RS-232. Charakteryzuje się wysoką precyzją ustawień (1 mA / 10 mV), rozbudowanym sterowaniem oraz funkcją blokady przycisków. Przeznaczony do zastosowań wymagających dokładnego sterowania zasilaniem, m.in. w laboratoriach, instytutach badawczych, przemyśle elektronicznym, edukacji i warsztatach serwisowych. Korad KA3005P

Brak towaru

Niewielki silnik Pololu z plastikową przekładnią 120:1, napięciem pracy 4,5 V, prędkością 120 rpm i momentem obrotowym 1,4 kg*cm (20 oz-in), D-kształtnym wałem pod kątem 90° względem obustronnych osi silnika. Pololu 1519

Brak towaru

Zintegrowany optyczny sensor odległości, koloru RGB, natężenia światła, detektor gestów 3D z wbudowanym oświetlaczem IrED.

Brak towaru

Arria V GX FPGA Video Development System