- Out-of-Stock

Overview

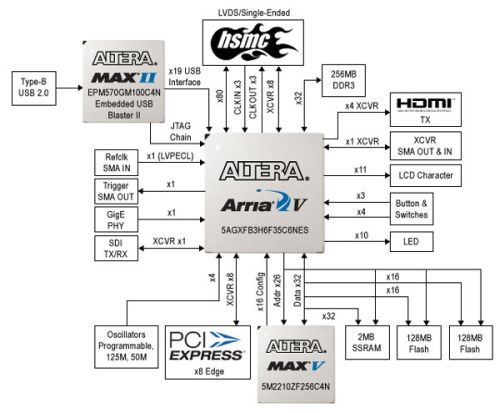

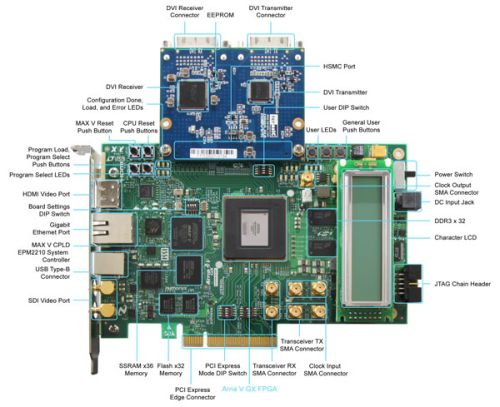

The Arria V GX FPGA Video Development System is an ideal video processing platform for high-performance, cost-effective video applications. The Arria II development kit features 256MB of SDRAM memory, HDMI, and SDI connections to form a perfect solution for imaging applications.

The DVI-HSMC daughter card part of the bundled package will allow developers to access high quality and high resolution video signals that can support resolution up to 1600x1200. A complete DVI video controller design with source code is provided.

Terasic recognized for its strong design expertise in high-end video, imaging and multimedia products have made available a video development package that targets video processing development. The platform can also allow users to experience advanced image processing designs incorporating VIP (Altera’s Video and Image Processing Suite MegaCore Functions).

Specification

Altera Arria V GX Video Development System

Terasic DVI-HSMC Card

Layout

Resources

Demo

DVI Video Development System Bundle

The Terasic DVI Development System bundles together the DVI daughter card and Altera development kit for cost-effective video development. All source code shown is included.

Code: K0111

Manufacturer BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Poland sprzedaz@kamami.pl 22 767 36 20

Responsible person BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Poland sprzedaz@kamami.pl 22 767 36 20

No product available!

No product available!

No product available!

No product available!

No product available!

No product available!

No product available!

ICP programmer for ST7F Flash microcontrollers

No product available!

No product available!

ZL17ARM_A - ARMputer with NPCP LPC2103 microcontroller

No product available!

10/100 Ethernet transceiver with Media Independent Interface, 3.3V, TQFP64, RoHS

No product available!

No product available!

No product available!

No product available!

No product available!

No product available!

Arria V GX FPGA Video Development System