Overview

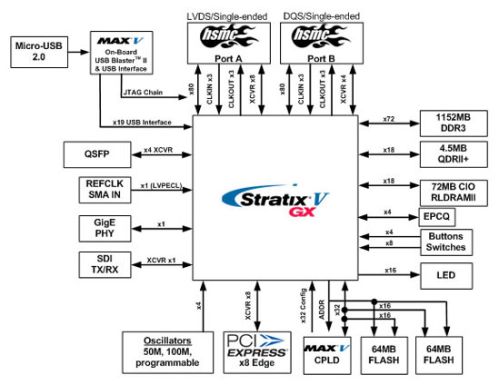

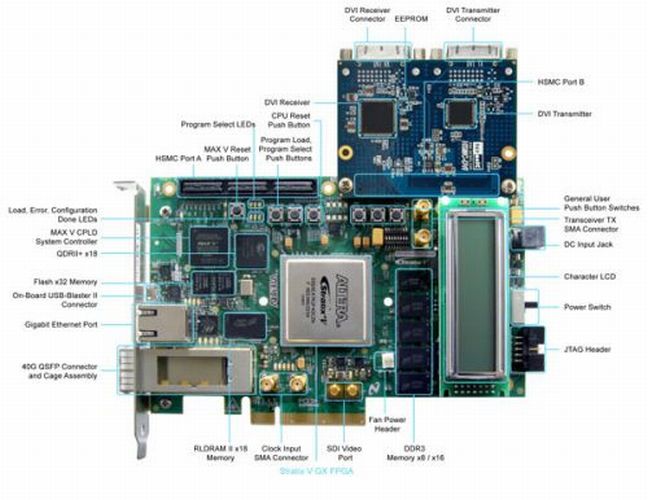

The Stratix V GX FPGA Video Development System fills the need for the highest bandwidth, best performance video applications. The kit features an extensive feature-set of memories, including DDR3, QDRII+, and RLDRAM II. The QSFP optical cage, PCIe x8 edge connectors, SDI, and gigabit Ethernet options allow for blazingly fast interfacing with peripherals.

The DVI-HSMC daughter card part of the bundled package will allow developers to access high quality and high resolution video signals that can support resolution up to 1600x1200. A complete DVI video controller design with source code is provided.

Terasic recognized for its strong design expertise in high-end video, imaging and multimedia products have made available a video development package that targets video processing development. The platform can also allow users to experience advanced image processing designs incorporating VIP (Altera’s Video and Image Processing Suite MegaCore Functions).

Specification

Stratix V GX Video Development System

Terasic DVI-HSMC Card

Layout

Resources

Kit Contents

Demo

DVI Video Development System Bundle

The Terasic DVI Development System bundles together the DVI daughter card and Altera development kit for cost-effective video development. All source code shown is included.

Code: K0117

Producent BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Moduł akceleratora obliczeń oparty na układzie FPGA Intel® Agilex™. Ma gniazdo PCI Express Gen 4.0 x16, dwa złącza 200G QSFP-DD i oferuje 32 GB DDR4. Terasic DE10-Agilex (P0701)

Brak towaru

Zestaw startowy DE10-Standard z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. P0493

Terasic NET-FMC to karta rozszerzająca z Gigabajtowym Ethernetem oraz interfejsem FMC. Dzięki temu interfejsowi może być używana z zestawami firmy Terasic. Terasic P0481

Brak towaru

TerasIC ADA-HSMC to wydajna karta konwersji AD/DA dla systemów FPGA, oferująca wysoką precyzję i elastyczność w aplikacjach DSP oraz komunikacyjnych. Dzięki wsparciu interfejsów HSMC i GPIO zapewnia szeroką kompatybilność z płytami rozwojowymi Terasic i Altera, umożliwiając szybki rozwój systemów przetwarzania sygnałów.

Brak towaru

Brak towaru

Adapter przeznaczony do łączenia płytek ze złączem PCIe z komputerem. Może obsługiwać interfejs PCIe Gen3 x4. Terasic P0492

TerasIC DVI-HSMC to karta rozszerzeń FPGA z nadajnikiem i odbiornikiem DVI, umożliwiająca obsługę wysokorozdzielczych sygnałów wideo w projektach multimedialnych i systemach przetwarzania obrazu. Dzięki zgodności z platformami Terasic i Altera oferuje szybkie wdrożenie i testowanie aplikacji wizualnych w oparciu o układy FPGA.

[CENA EDUKACYJNA] Zestaw startowy/ewaluacyjny Terasic DE0-Nano Board dla układów FPGA Cyclone IV firmy Altera. Jeden z najmniejszych i najprostszych zestawów startowych dla układów FPGA, wyposażony w podstawowe peryferia, w tym programator-konfigurator JTAG.Obniżona cena (w stosunku do klasycznej wersji Terasic DE0-Nano) dotyczy wyłącznie szkół, uczelni, wykładowców, uczniów i studentów. P0082

Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE i obsługuje PCIe Gen 2x4. Płytka posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0559

Brak towaru

Moduł TerasIC HDMI_TX P0084 umożliwia realizację transmisji HDMI z wykorzystaniem interfejsu HSMC w projektach FPGA. Zgodność z najnowszymi standardami HDMI i dostarczony kod źródłowy przyspieszają rozwój oraz testowanie aplikacji wizyjnych i multimedialnych w systemach opartych na układach FPGA.

Brak towaru

TerasIC NET to moduł Ethernet w standardzie HSMC, umożliwiający szybkie wdrożenie komunikacji sieciowej w systemach FPGA. Dzięki obsłudze prędkości od 10 Mb/s do 1 Gb/s oraz pełnej integracji z układami FPGA stanowi wygodne narzędzie do projektowania aplikacji wymagających niezawodnej komunikacji sieciowej.

Brak towaru

Płytka rozwojowa Terasic DE25-Nano z układem FPGA Agilex™ 5 i systemem HPS ARM Cortex-A76/A55 stanowi nowoczesną platformę dla aplikacji AI, przetwarzania wizyjnego i systemów wbudowanych. Bogaty zestaw interfejsów oraz pamięci, aktywne chłodzenie i kompaktowe wymiary pozwalają na wykorzystanie zarówno w prototypowaniu, jak i docelowych rozwiązaniach przemysłowych.

Brak towaru

TerasIC TR4-230 (P0107) oferuje platformę rozwojową opartą na FPGA Stratix IV GX z szerokim zakresem interfejsów oraz wsparciem dla projektów PCI Express i szybkiej pamięci DDR3. Rozwiązanie przeznaczone do budowy systemów komunikacyjnych, prototypowania ASIC oraz aplikacji o wysokim zapotrzebowaniu na zasoby logiczne.

Brak towaru

TerasIC USB Blaster Download Cable (UBT) to w pełni zgodny z Altera USB Blaster programator JTAG/ISP dla układów CPLD i FPGA. Dzięki niezawodnej konstrukcji oraz odporności na zakłócenia stanowi uniwersalne narzędzie dla projektantów pracujących z układami programowalnymi Altera. TerasIC P0302

Karta HTG-M przeznaczona jest dla zestawów ewaluacyjnych z układami FPGA, które zostały wyposażone w złącze HSMC (High-Speed Mezzanine connector) lub HSTC (High-Speed Terasic Connector). Karta HTG posiada trzy złącza męskie (40-pinowe). Pozwala na konwersje wejść/wyjść HSMC do dwóch 40-pinowych złącz prototypowych lub złącza HSTC do trzech 40-pinowych złącz prototypowych. TerasIC P0033

Stratix V GX FPGA Video Development System