37 395,09 zł Netto

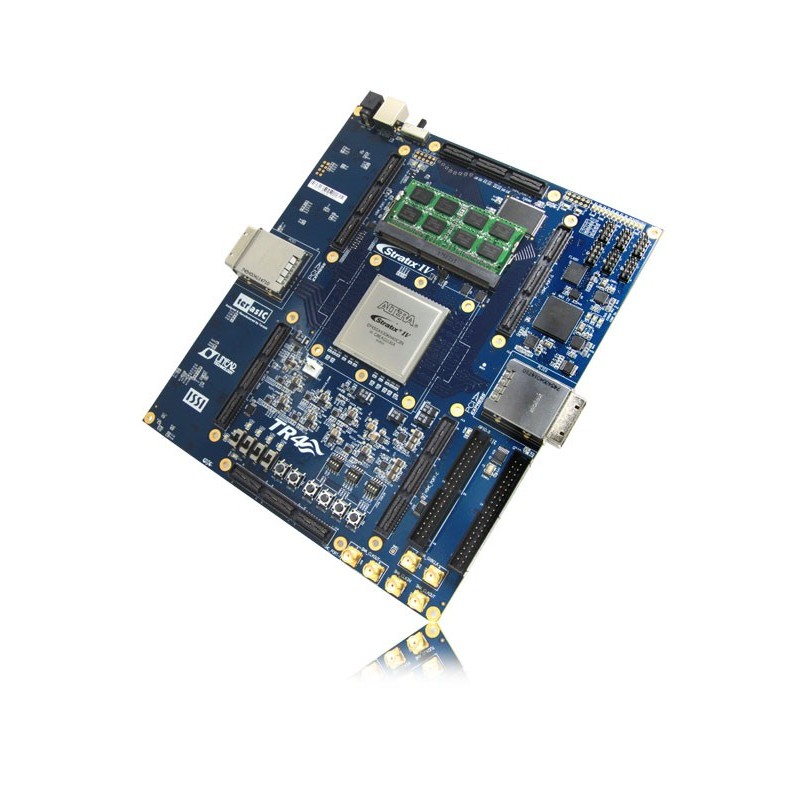

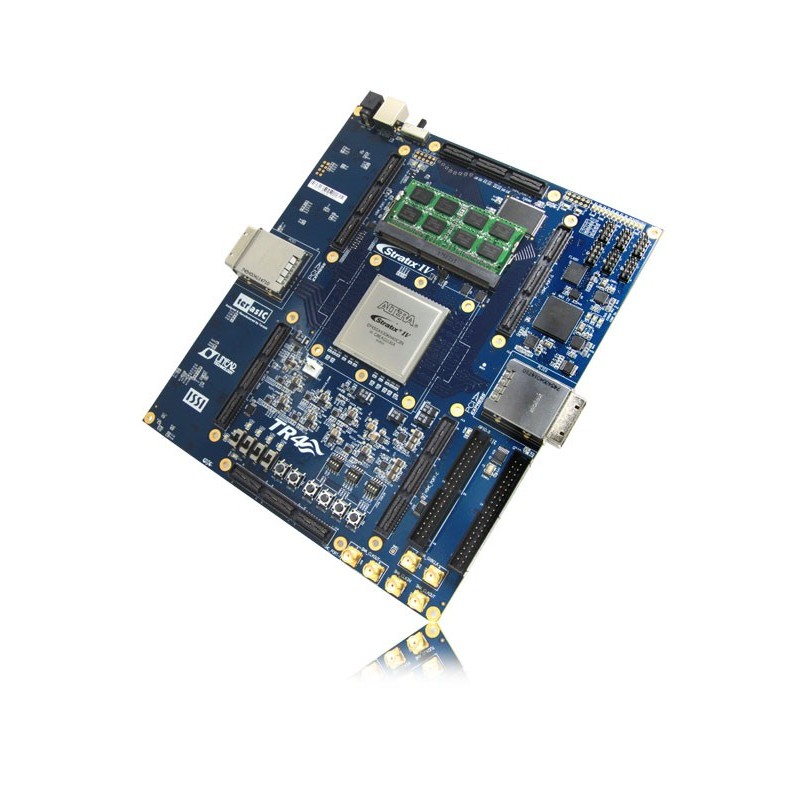

TR4 FPGA Development Kit

darmowa wysyłka na terenie Polski dla wszystkich zamówień powyżej 500 PLN

Jeśli Twoja wpłata zostanie zaksięgowana na naszym koncie do godz. 11:00

Każdy konsument może zwrócić zakupiony towar w ciągu 14 dni bez zbędnych pytań

Overview

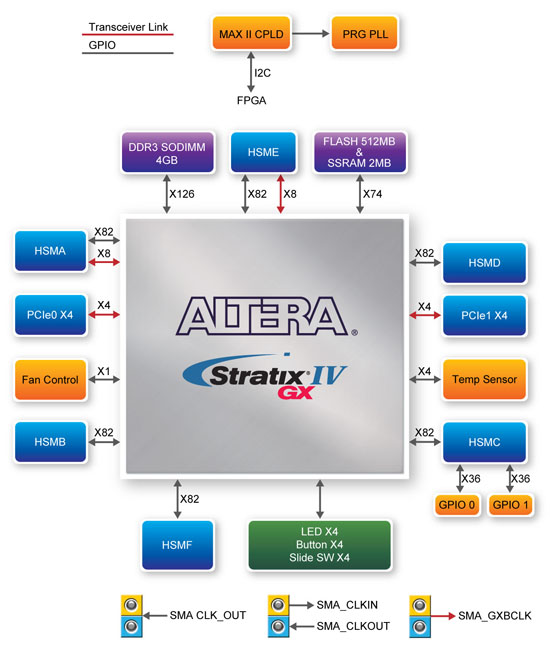

The TR4 Development Board provides the ideal hardware platform for system designs that demand high-performance, serial connectivity, and advanced memory interfacing. Developed specifically to address the rapidly evolving requirements in many end markets for greater bandwidth, improved jitter performance, and lower power consumption, the TR4 is powered by the Stratix® IV GX device and supported by industry-standard peripherals, connectors and interfaces that offer a rich set of features that is suitable for a wide range of compute-intensive applications.

The TR4 is supported by multiple reference designs and six High-Speed Mezzanine Card (HSMC) connectors that allow scaling and customization with mezzanine daughter cards. For large-scale ASIC prototype development, multiple TR4s can be stacked together to create an easily-customizable multi-FPGA system.

Specification

Layout

Resources

TR4 Control Panel – allows users to access various components on the TR4 board from a host computer.

TR4 Control Panel

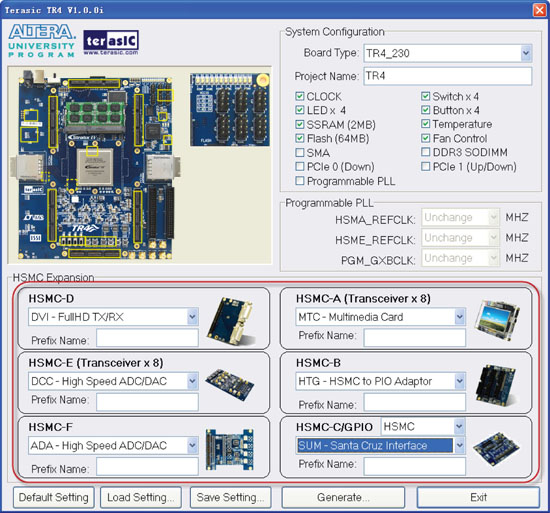

TR4 System Builder – a powerful tool comes with the TR4 board. This tool will allow users to create a Quartus II project file on their custom design for the TR4 board. The top-level design file, pin assignments, and I/O standard settings for the TR4 board will be generated automatically by the TR4 System Builder. In addition, through the HSMC connectors you can select various daughter cards in conjunction with the TR4 using the TR4 System Builder.

TR4 System Builder

The generated Quartus II project files include the following:

Kit Contents

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Karta HTG-M przeznaczona jest dla zestawów ewaluacyjnych z układami FPGA, które zostały wyposażone w złącze HSMC (High-Speed Mezzanine connector) lub HSTC (High-Speed Terasic Connector). Karta HTG posiada trzy złącza męskie (40-pinowe). Pozwala na konwersje wejść/wyjść HSMC do dwóch 40-pinowych złącz prototypowych lub złącza HSTC do trzech 40-pinowych złącz prototypowych. TerasIC P0033

Brak towaru

Terasic Spider to sześcionożny robot kroczący z 18 serwomechanizmami sterowanymi przez płytkę Altera DE0-Nano-SoC łączącą układ FPGA oraz procesor ARM Cortex-A9. Zestaw zawiera złożonego robota oraz liczne akcesoria. P0425

Altera DE2-115 Development and Education Board Academic

Brak towaru

Brak towaru

Stratix V GX FPGA Video Development System

Brak towaru

Terasic DE10-Lite Board to niskobudżetowa płytka deweloperska z układem FPGA Altera MAX 10. Płyta zawiera szereg komponentów umożliwiających naukę oraz tworzenie prototypów projektów opartych o układy FPGA. Terasic P0466

Brak towaru

Moduł pamięci SODIMM firmy TerasIC o pojemności 18MB i częstotliwości pracy 550MHz. Moduł przeznaczony jest do pracy z układami FPGA Intel Stratix 10 w zestawach ewaluacyjnych takich jak TerasIC DE10-Pro-GX-280-4G oraz TerasIC DE10-Pro-GX-280-8G. TerasIC S0534

Brak towaru

Płytka ewaluacyjna z układem Intel Agilex SoC z 1400 tys. elementów logicznych. Moduł ma gniazda z wbudowaną pamięcią DDR4 SO-DIMM o pojemności 32 GB, złącze QSFP28, PCIe Gen 4x16, wbudowany USB-Blaster II oraz złącza FMC/FMC+ do rozbudowy. TerasIC Apollo Agilex SOM (P0795)

Brak towaru

Terasic DE10-Lite Board to niskobudżetowa płytka deweloperska z układem FPGA Altera MAX 10. Płyta zawiera szereg komponentów umożliwiających naukę oraz tworzenie prototypów projektów opartych o układy FPGA

Brak towaru

Brak towaru

[CENA EDUKACYJNA] Zestaw startowy/ewaluacyjny Terasic DE0-Nano Board dla układów FPGA Cyclone IV firmy Altera. Jeden z najmniejszych i najprostszych zestawów startowych dla układów FPGA, wyposażony w podstawowe peryferia, w tym programator-konfigurator JTAG.Obniżona cena (w stosunku do klasycznej wersji Terasic DE0-Nano) dotyczy wyłącznie szkół, uczelni, wykładowców, uczniów i studentów. P0082

Brak towaru

Zestaw ewaluacyjny Terasic DE0 Board dla układów FPGA Cyclone III firmy Altera. Wyposażono go we wszystkie podstawowe peryferia umożliwiające prowadzenie prac badawczych i ewaluacyjnych z układami FPGA, w tym programator-konfigurator JTAG.

Brak towaru

Sterownik serwomechanizmów do zestawów FPGA TerasIC serii DE umożliwia sterowanie maksymalnie 24 serwomechanizmami. Dostarcza napięcie 6 V do zasilania serwomechanizmów. W zestawie serwomechanizm MG966R i taśma do połączenia z zestawem FPGA. P0288

TR4 FPGA Development Kit