6 014,45 zł Netto

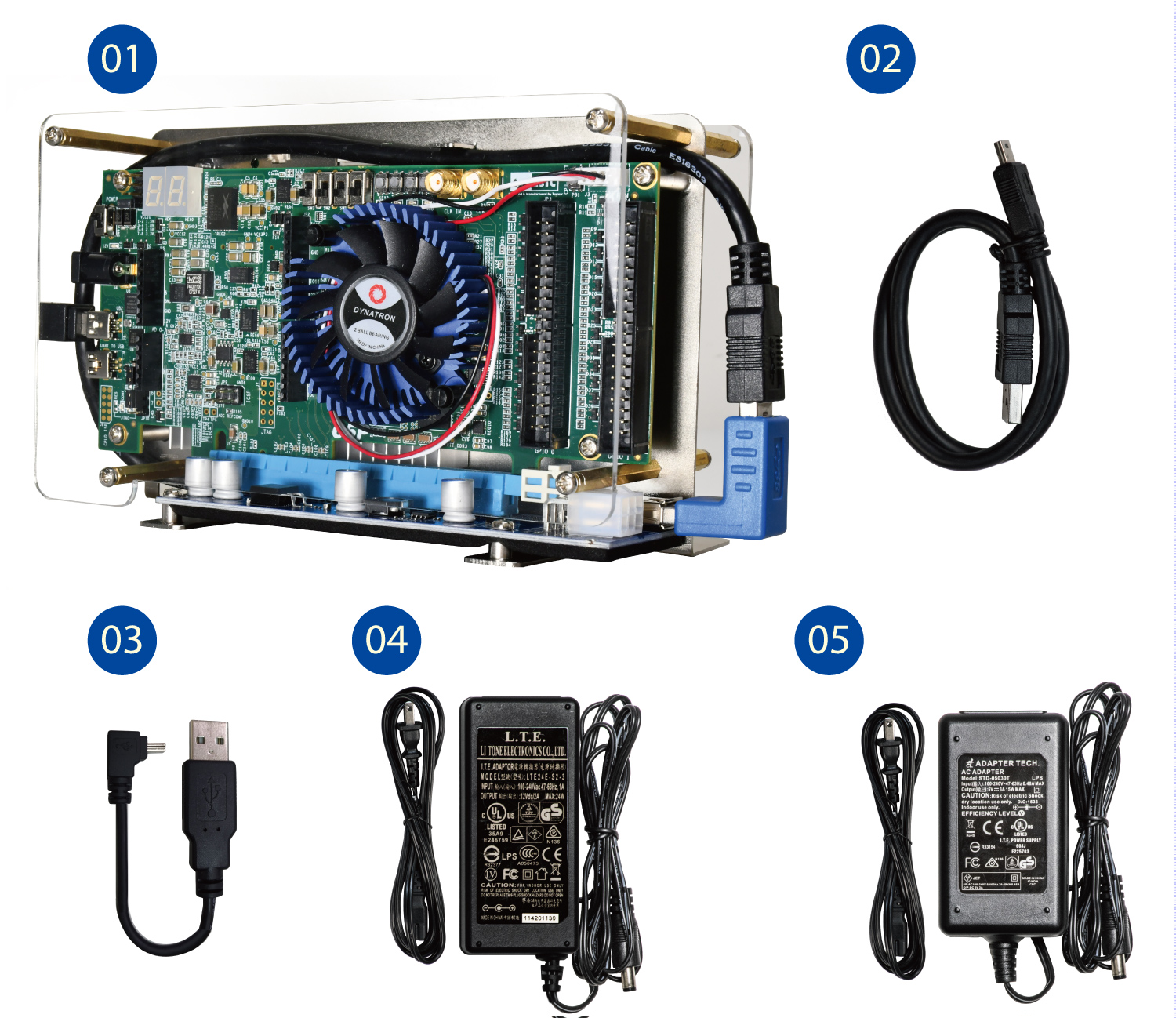

[CENA EDUKACYJNA] Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE oraz minikomputer z układem Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). Moduł FPGA posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0650

darmowa wysyłka na terenie Polski dla wszystkich zamówień powyżej 500 PLN

Jeśli Twoja wpłata zostanie zaksięgowana na naszym koncie do godz. 11:00

Każdy konsument może zwrócić zakupiony towar w ciągu 14 dni bez zbędnych pytań

Oferta przeznaczona wyłącznie dla odbiorców akademickich (studentów i wykładowców wyższych uczelni)!

Składając zamówienie należy podać:

- imię i nazwisko użytkownika

- stanowisko

- adres e-mail użytkownika (adres e-mail musi być z domeny uczelni)

- pełną nazwę uczelni

- nazwę wydziału/instytutu/zakładu dydaktycznego

- adres uczelni

- stronę internetową uczelni

- telefon

- zastosowanie produktu

W uzasadnionych przypadkach zastrzegamy sobie prawo do odmowy zrealizowania zamówienia z oferty akademickiej.

Wszelkie zapytania można kierować na adres: sprzedaz@kamami.pl.

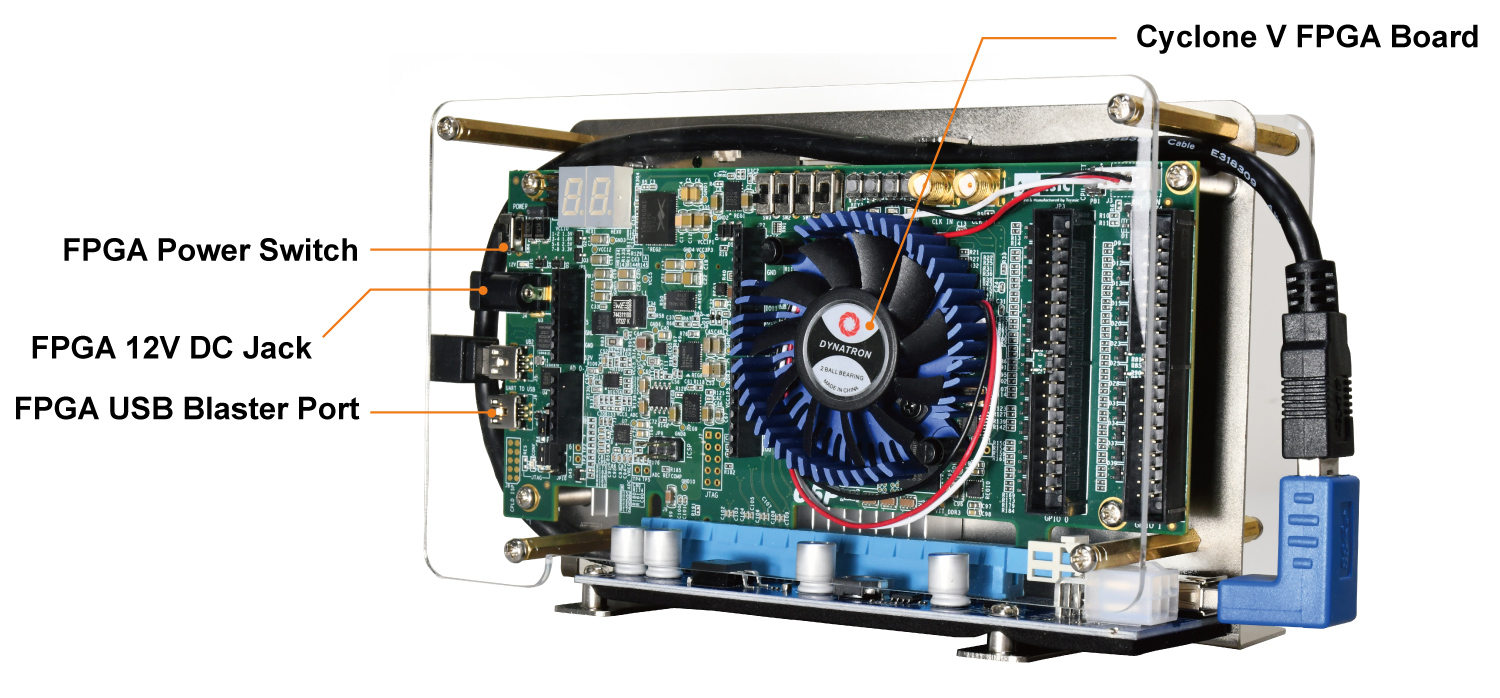

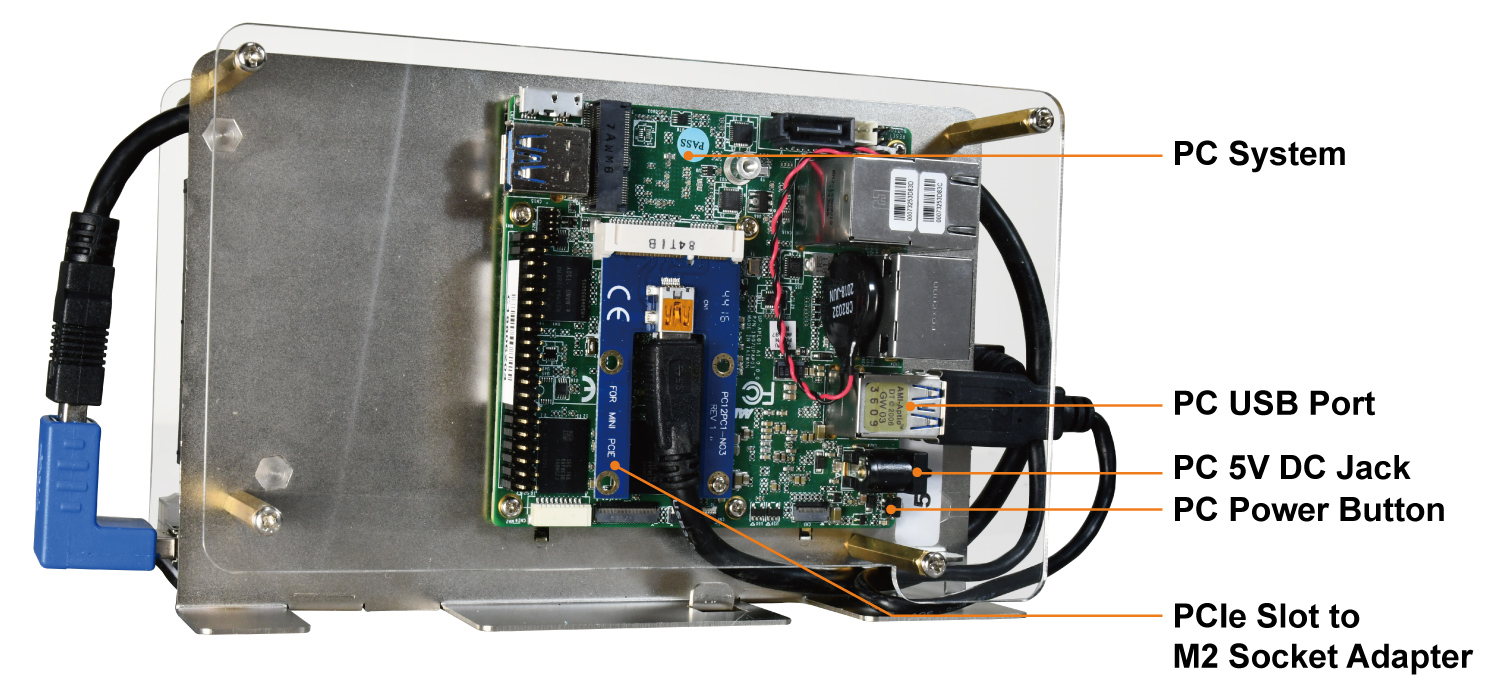

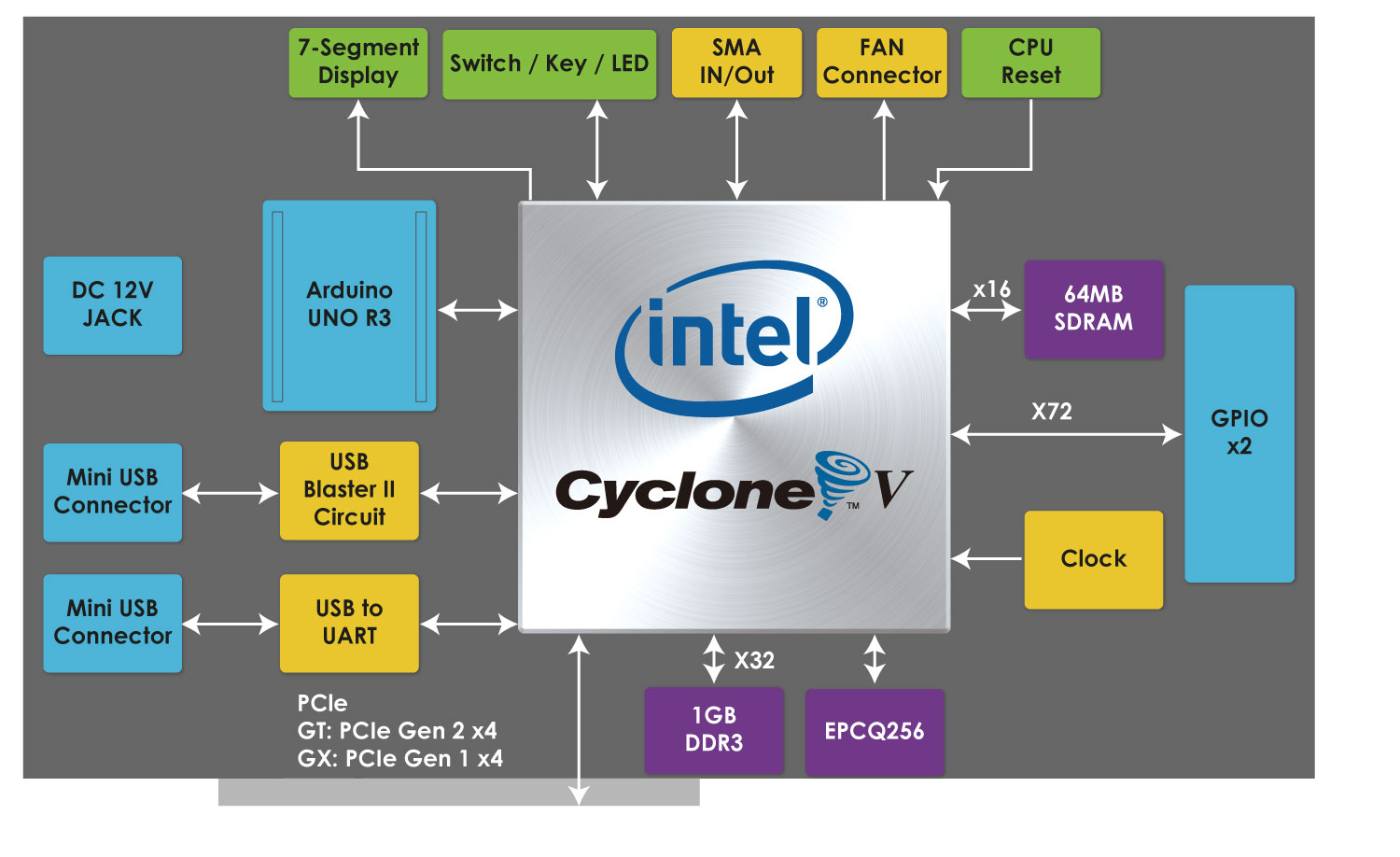

OpenVINO to zestaw startowy FPGA w postaci karty z złączem PCIe oraz zestawem PC z układem Intel Celeron Dual Core. Zestaw jest wyposażony w programowalny układ Cyclone V GT z 301K LE i obsługuje PCIe Gen 2x4. FPGA posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO czy pozwalające podłączyć rozszerzenia Arduino. Układ PC wyposażony jest w 64 GB pamięci eMMC oraz 4 GB pamięci RAM DDR4. To sprawia, że zestaw startowy OpenVINO to konfigurowalna platforma łącząca dużą wydajnością obliczeniową i niskie zużycie energii.

Pakiet OpenVINO zawiera projekty referencyjne dla wszystkich urządzeń peryferyjnych zestawu oraz szczegółową instrukcję dla programistów.

Zestaw CPU (PC)

Zestaw FPGA OpenVINO Starter Kit

Opis elementów składowych i rozmieszczenie złącz

Diagram blokowy

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Zestaw ewaluacyjny Terasic DE0 Board dla układów FPGA Cyclone III firmy Altera. Wyposażono go we wszystkie podstawowe peryferia umożliwiające prowadzenie prac badawczych i ewaluacyjnych z układami FPGA, w tym programator-konfigurator JTAG.

Brak towaru

VEEK-MT2S to płytka deweloperska oparta na układzie Cyclone V SX SoC Cyclone V SX SoC—5CSXFC6D6F31C6N. W zestawie, oprócz płytki z układem programowalnym FPGA, znajdują się również 7-calowy wyświetlacz TFT dotykowy o rozdzielczości 800 x 480 pikseli, kamera o rozdzielczości 8 Megapikseli (3264 x 2448 pikseli), czujnik światła czujnik IMU 9DOF (akcelerometr, żyroskop, magnetometr). Terasic K0161

Brak towaru

Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE oraz minikomputer z układem Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). Moduł FPGA posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0650

Brak towaru

MAX 10 Plus jest zestawem deweloperskim opartym o układ FPGA od Intela, wyposażony w 50 000 programowalnych elementów logicznych. Digilent P0638

Brak towaru

Terasic Spider to sześcionożny robot kroczący z 18 serwomechanizmami sterowanymi przez płytkę Altera DE0-Nano-SoC łączącą układ FPGA oraz procesor ARM Cortex-A9. Zestaw zawiera złożonego robota oraz liczne akcesoria. P0425

Brak towaru

A-Cute Car Robotic Kit to kompletne 3-kołowe podwozie robota mobilnego wraz ze sterownikiem opartym o układ FPGA do samodzielnego programowania. P0467

Brak towaru

Brak towaru

Terasic HDMI-FMC to karta rozszerzająca układy ewaluacyjny o możliwość wyświetlania oraz odbierania obrazu wideo przy pomocy złącz HDMI. Pozwalają wyświetlać obraz w rozdzielczości 4K@30FPS. Wspiera HDMI 1.4a. Terasic P0431

Zintegrowany komputer jednopłytkowy z rdzeniem Cyclone V SoC. SoC SoM zawiera pamięć DDR3, pamięć Flash, system zarządzania energią, wspólne kontrolery interfejsów i oprogramowanie do obsługi płyt (BSP). Terasic P0581

Brak towaru

Zestaw ewaluacyjny Terasic DE0 Board dla układów FPGA Cyclone III firmy Altera. Wyposażono go we wszystkie podstawowe peryferia umożliwiające prowadzenie prac badawczych i ewaluacyjnych z układami FPGA, w tym programator-konfigurator JTAG.

Brak towaru

Moduł SoM z układem SoC łączącym FPGA z rdzeniem ARM Cortex-A9. Płytka wyposażona jest w złacze DDR4 Eadge (z zasialniem 3,3 V). Terasic P0553

Brak towaru

DE1-SoC + 5 points multitouch display MTL2

Terasic DE10-Lite Board to niskobudżetowa płytka deweloperska z układem FPGA Altera MAX 10. Płyta zawiera szereg komponentów umożliwiających naukę oraz tworzenie prototypów projektów opartych o układy FPGA. Terasic P0466

Brak towaru

Zestaw elementów przeznaczony dla zestawów ewaluacyjnych z układami programowalnymi z rodziny Cyclone V SoC FPGA, w którego skład wchodzą; 7-calowy wyświetlacz TFT z obsługą dotyku (5-punktów), 8 megapikselowa kamera z autofocusem oraz czujniki (światła, akcelerometr, żyroskop, magnetometr). Terasic P0494

Brak towaru

[CENA EDUKACYJNA] Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE i obsługuje PCIe Gen 2x4. Płytka posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0559

Brak towaru

Brak towaru

VEEK-MT2S to płytka deweloperska oparta na układzie Cyclone V SX SoC Cyclone V SX SoC—5CSXFC6D6F31C6N. W zestawie, oprócz płytki z układem programowalnym FPGA, znajdują się również 7-calowy wyświetlacz TFT dotykowy o rozdzielczości 800 x 480 pikseli, kamera o rozdzielczości 8 Megapikseli (3264 x 2448 pikseli), czujnik światła czujnik IMU 9DOF (akcelerometr, żyroskop, magnetometr). Terasic K0161

Brak towaru

[CENA EDUKACYJNA] Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE oraz minikomputer z układem Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). Moduł FPGA posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0650