3 106,99 zł Netto

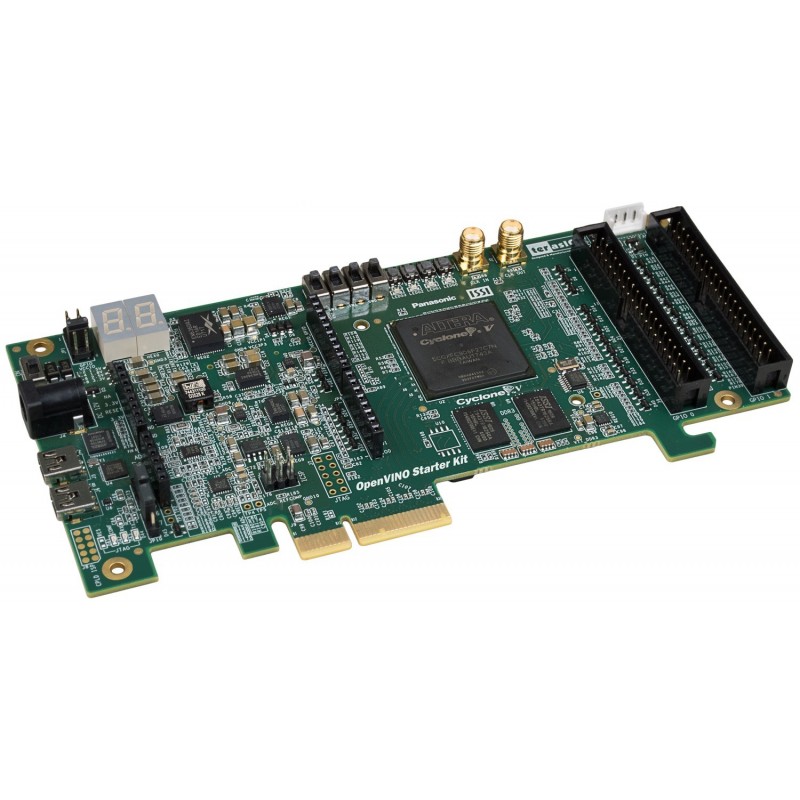

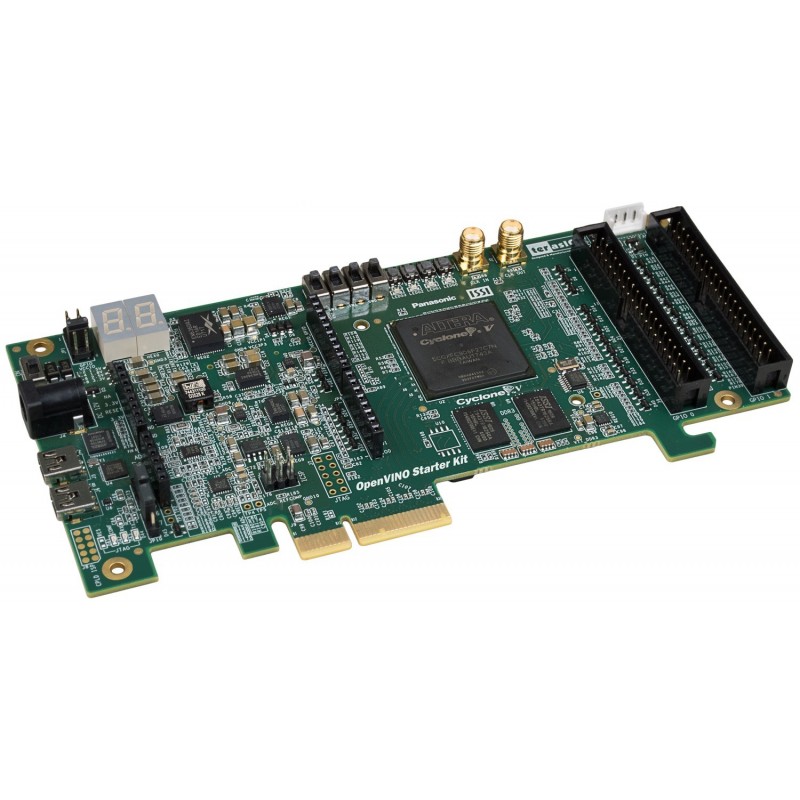

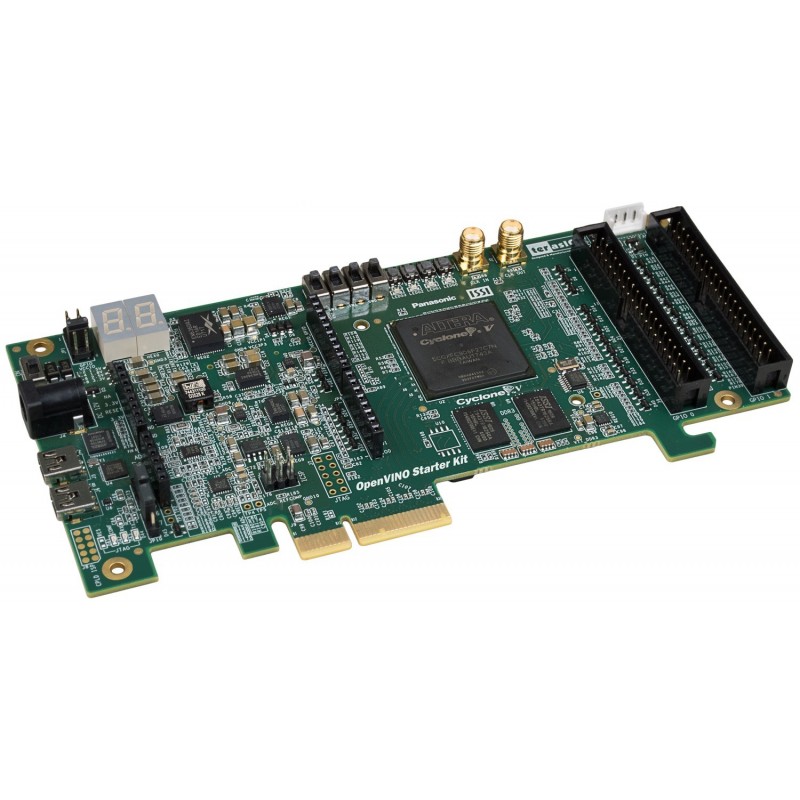

[CENA EDUKACYJNA] Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE i obsługuje PCIe Gen 2x4. Płytka posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0559

Oferta przeznaczona wyłącznie dla odbiorców akademickich (studentów i wykładowców wyższych uczelni)!

Składając zamówienie należy podać:

- imię i nazwisko użytkownika

- stanowisko

- adres e-mail użytkownika (adres e-mail musi być z domeny uczelni)

- pełną nazwę uczelni

- nazwę wydziału/instytutu/zakładu dydaktycznego

- adres uczelni

- stronę internetową uczelni

- telefon

- zastosowanie produktu

W uzasadnionych przypadkach zastrzegamy sobie prawo do odmowy zrealizowania zamówienia z oferty akademickiej.

Wszelkie zapytania można kierować na adres: sprzedaz@kamami.pl.

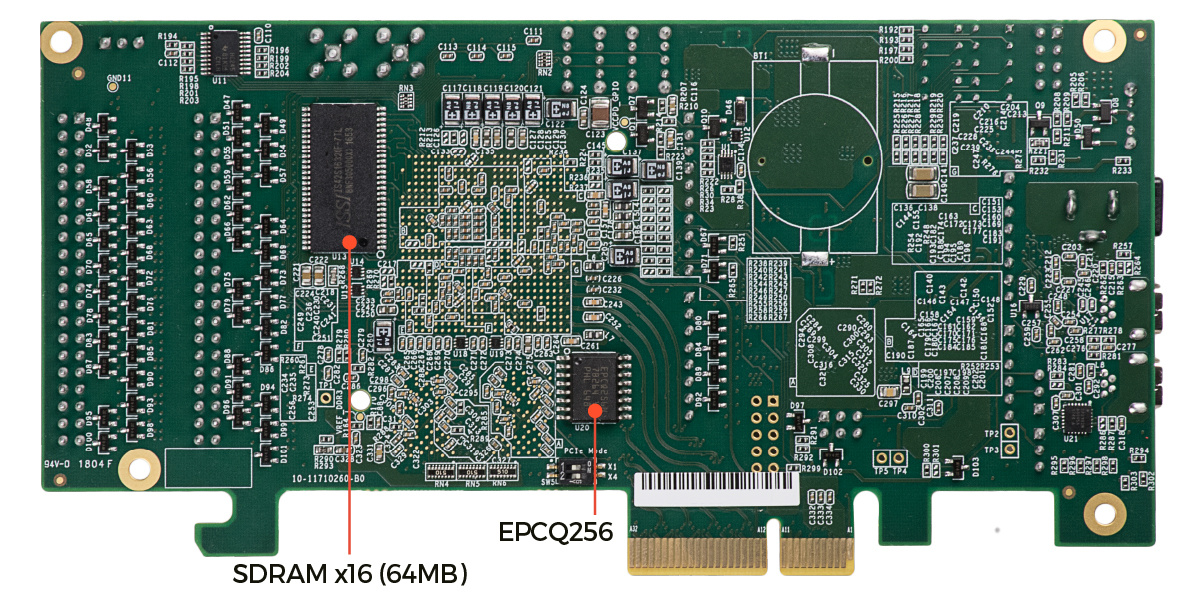

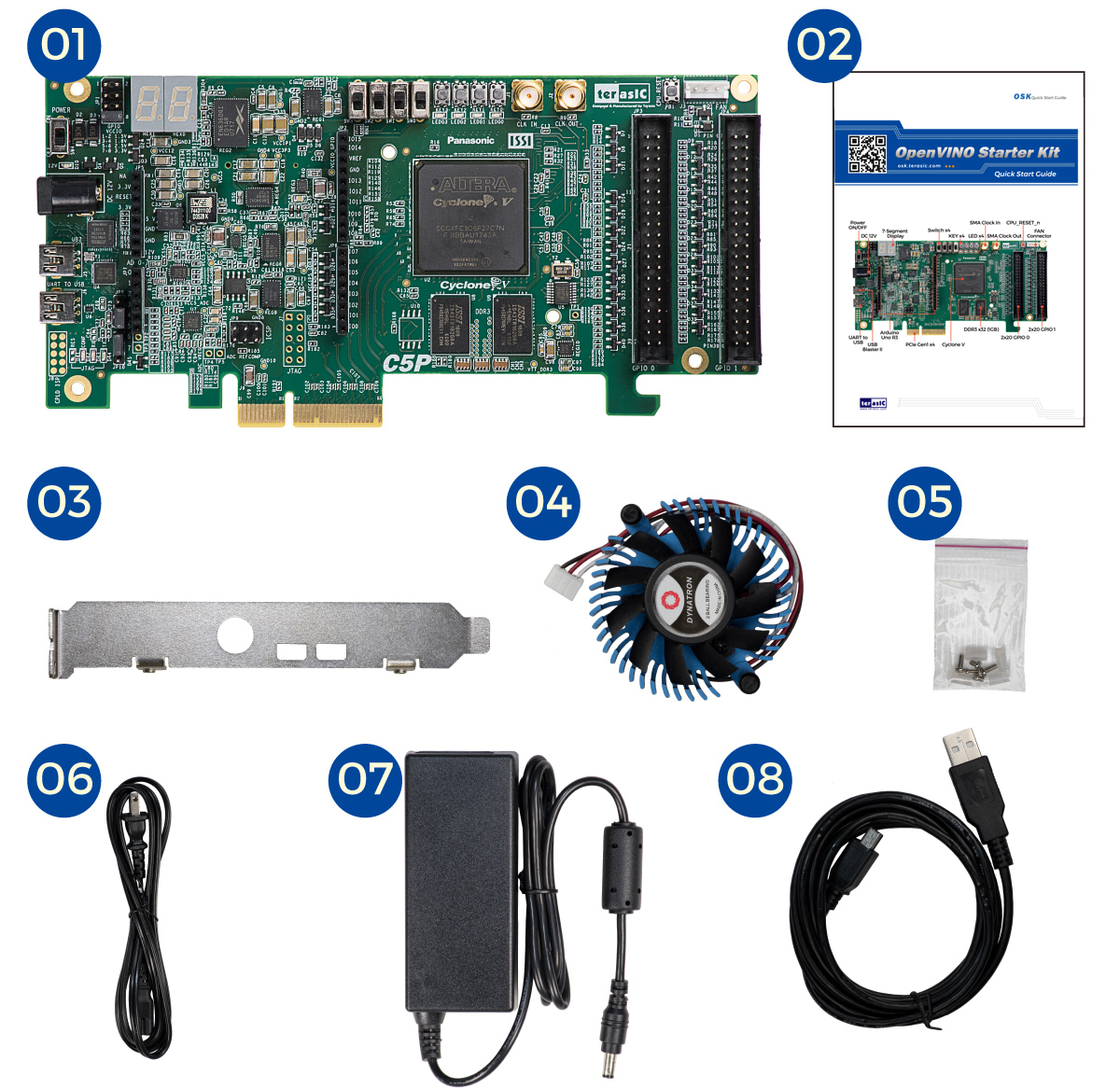

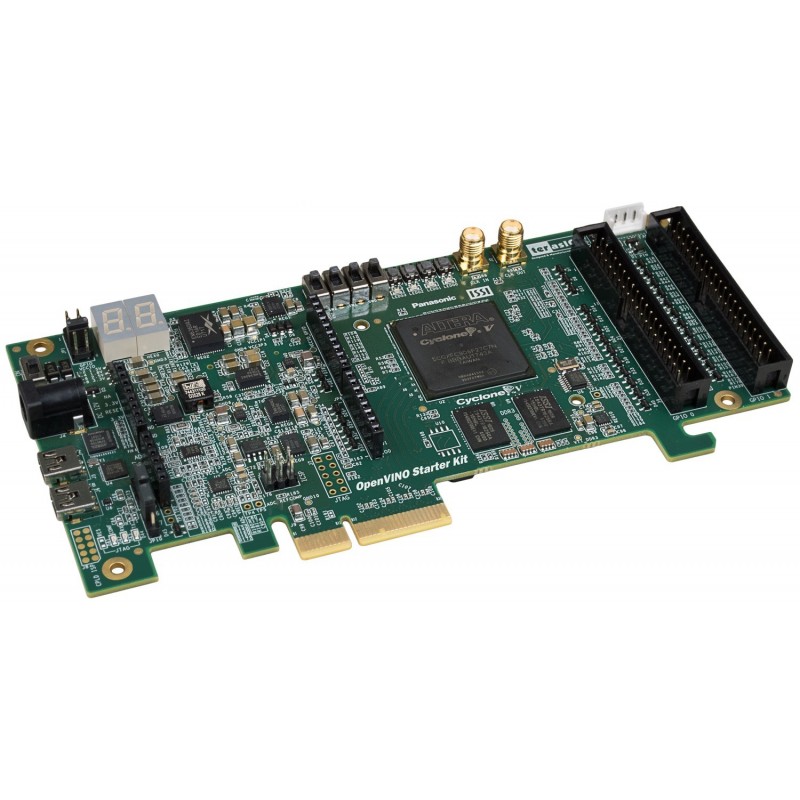

OpenVINO to zestaw startowy FPGA w postaci karty z złączem PCIe o wysokiej wydajności. Jest wyposażony w programowalny układ Cyclone V GT z 301K LE i obsługuje PCIe Gen 2x4. Płytka posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO czy pozwalające podłączyć rozszerzenia Arduino. To sprawia, że zestaw startowy OpenVINO to konfigurowalna platforma łącząca dużą wydajnością obliczeniową i niskie zużycie energii.

Pakiet OpenVINO zawiera projekty referencyjne dla wszystkich urządzeń peryferyjnych zestawu oraz szczegółową instrukcję dla programistów.

Rozmieszczenie i opis złącz

Schemat blokowy

Producent BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

TerasIC DE0 to kompletny zestaw ewaluacyjny oparty na FPGA Cyclone III, zaprojektowany do nauki, testowania i wdrażania systemów cyfrowych. Oferuje szeroki zestaw interfejsów i peryferiów umożliwiających tworzenie złożonych projektów zarówno edukacyjnych, jak i przemysłowych.

Brak towaru

[CENA EDUKACYJNA] Zestaw ewaluacyjny Terasic DE0 Board dla układów FPGA Cyclone III firmy Altera. Wyposażono go we wszystkie podstawowe peryferia umożliwiające prowadzenie prac badawczych i ewaluacyjnych z układami FPGA, w tym programator-konfigurator JTAG. Obniżona cena (w stosunku do klasycznej wersji Terasic DE0) dotyczy wyłącznie szkół, uczelni, wykładowców, uczniów i studentów.

Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE i obsługuje PCIe Gen 2x4. Płytka posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0559

Brak towaru

[CENA EDUKACYJNA] Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE oraz minikomputer z układem Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). Moduł FPGA posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0650

Brak towaru

Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE oraz minikomputer z układem Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). Moduł FPGA posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0650

Brak towaru

Wyświetlacz LCD alfanumeryczny 2x16 bez podświetlenia przeznaczony do zestawów firmy TerasIC (DE0, DE1, DE2 , DE2 -115). P0075

Terasic HDMI-FMC to karta rozszerzająca układy ewaluacyjny o możliwość wyświetlania oraz odbierania obrazu wideo przy pomocy złącz HDMI. Pozwalają wyświetlać obraz w rozdzielczości 4K@30FPS. Wspiera HDMI 1.4a. Terasic P0431

Moduł ewaluacyjny z procesorem Intel Stratix 10 SoC z elementami logicznymi 2800K. Moduł posiada pamięć DDR4 SDRAM (do 64 GB), wbudowany USB-Blaster II, Ethernet, microSD, miniUSB oraz złącza FMC/FMC+ do rozbudowy. TerasIC Apollo S10 SoM Board (P0630)

Brak towaru

Brak towaru

Płytka ewaluacyjna z układem Intel Agilex SoC z 1400 tys. elementów logicznych. Moduł ma gniazda z wbudowaną pamięcią DDR4 SO-DIMM o pojemności 32 GB, złącze QSFP28, PCIe Gen 4x16, wbudowany USB-Blaster II oraz złącza FMC/FMC+ do rozbudowy. TerasIC Apollo Agilex SOM (P0795)

Brak towaru

Moduł XTS-FMC jest rozszerzeniem dla układów FPGA pozwalającym na dostęp do kanałów/interfejsów komunikacyjnych poprzez złącze SMA. TerasIC P0401

Brak towaru

TerasIC XSFP/SFP+HSMC (P0092) umożliwia budowę systemów Ethernet 10G opartych na interfejsie XAUI z dwoma kanałami SFP+ i zegarem referencyjnym 156,25 MHz. Moduł przeznaczony do integracji z płytami FPGA posiadającymi złącze HSMC, m.in. Stratix IV GX i DE4, znajduje zastosowanie w projektach sieciowych, transmisji danych oraz testach interfejsów wysokiej przepustowości.

Brak towaru

[CENA EDUKACYJNA] Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE oraz minikomputer z układem Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). Moduł FPGA posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0650

Brak towaru

TerasIC ADA-GPIO to karta konwersji AD/DA umożliwiająca współpracę z wieloma płytami FPGA przez interfejsy GPIO i HSMC. Dzięki wysokiej szybkości próbkowania oraz szerokiej kompatybilności doskonale nadaje się do zastosowań DSP, edukacyjnych i komunikacyjnych.

Brak towaru

Terasic Spider to sześcionożny robot kroczący z 18 serwomechanizmami sterowanymi przez płytkę Altera DE0-Nano-SoC łączącą układ FPGA oraz procesor ARM Cortex-A9. Zestaw zawiera złożonego robota oraz liczne akcesoria. P0425

MAX 10 Plus jest zestawem deweloperskim opartym o układ FPGA od Intela, wyposażony w 50 000 programowalnych elementów logicznych. Digilent P0638

Brak towaru

Moduł z kamerą przeznaczony do użycia z zestawami Terasic. Kamera posiada przetwornik o rozdzielczości 8 Megapikseli (3264 x 2448), do komunikacji wykorzystuje interfejs MIPI. Na module znalazł się również dekoder MIPI oraz układ HDMI-TX. Terasic P0449

Brak towaru

Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE i obsługuje PCIe Gen 2x4. Płytka posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0559

Brak towaru

Moduł TerasIC HDMI_RX P0083 umożliwia odbiór sygnałów HDMI przez interfejs HSMC w systemach FPGA. Dzięki zgodności ze standardami HDMI i HDCP oraz dostępnemu projektowi referencyjnemu, stanowi kompletne rozwiązanie do implementacji, testowania i analizy transmisji wideo w aplikacjach wbudowanych i systemach przetwarzania obrazu.

Brak towaru

Terasic ADC-SoC to płyta rozwojowa z układem programowalnym FPGA oraz dwukanałowym szybkim przetwornikiem ADC. Płyta bazuje na module Terasic DE0-Nano-SoC. Wbudowany przetwornik ADC wykorzystuje SMA jako interfejs wejściowy, posiada dwa kanały, oferuje rozdzielczość 14-bitową, i szybkość próbkowania do 150 MSPS Megasamples per Second). Terasic (P0435)

Brak towaru

Zestaw TerasIC P0057 umożliwia testowanie, debugowanie i symulację sygnałów w systemach wykorzystujących interfejs HSMC. Przeznaczony do prac projektowych i diagnostycznych z płytami głównymi FPGA i innymi układami wyposażonymi w złącze HSMC.

Brak towaru

[CENA EDUKACYJNA] Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE i obsługuje PCIe Gen 2x4. Płytka posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0559