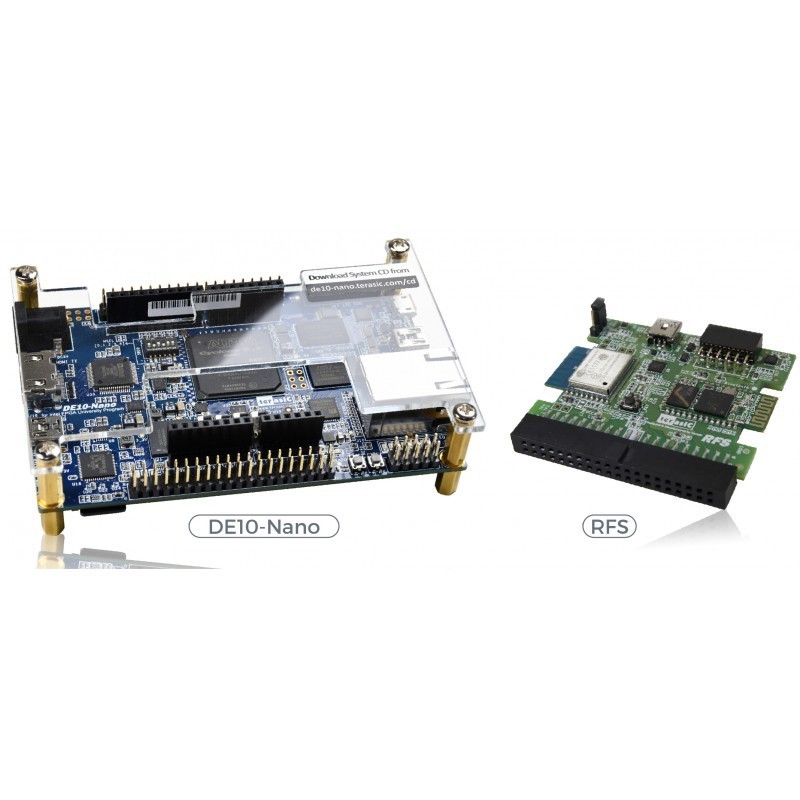

Zestaw z płytką FPGA Terasic DE10-Nano oraz modułem WiFi przeznaczony do projektów wykorzystujących FPGA do pracy w chmurze. Pomaga stworzyć aplikację opartą na FPGA, która może gromadzić, analizować i reagować na dane z urządzeń IoT. Zestaw jest certyfikowany przez kluczowych dostawców usług w chmurze (CSP), takich jak Microsoft Azure, i zawiera przykłady projektów typu open source, które przeprowadzą użytkowników przez proces łączenia urządzenia opartego na FPGA z chmurą.

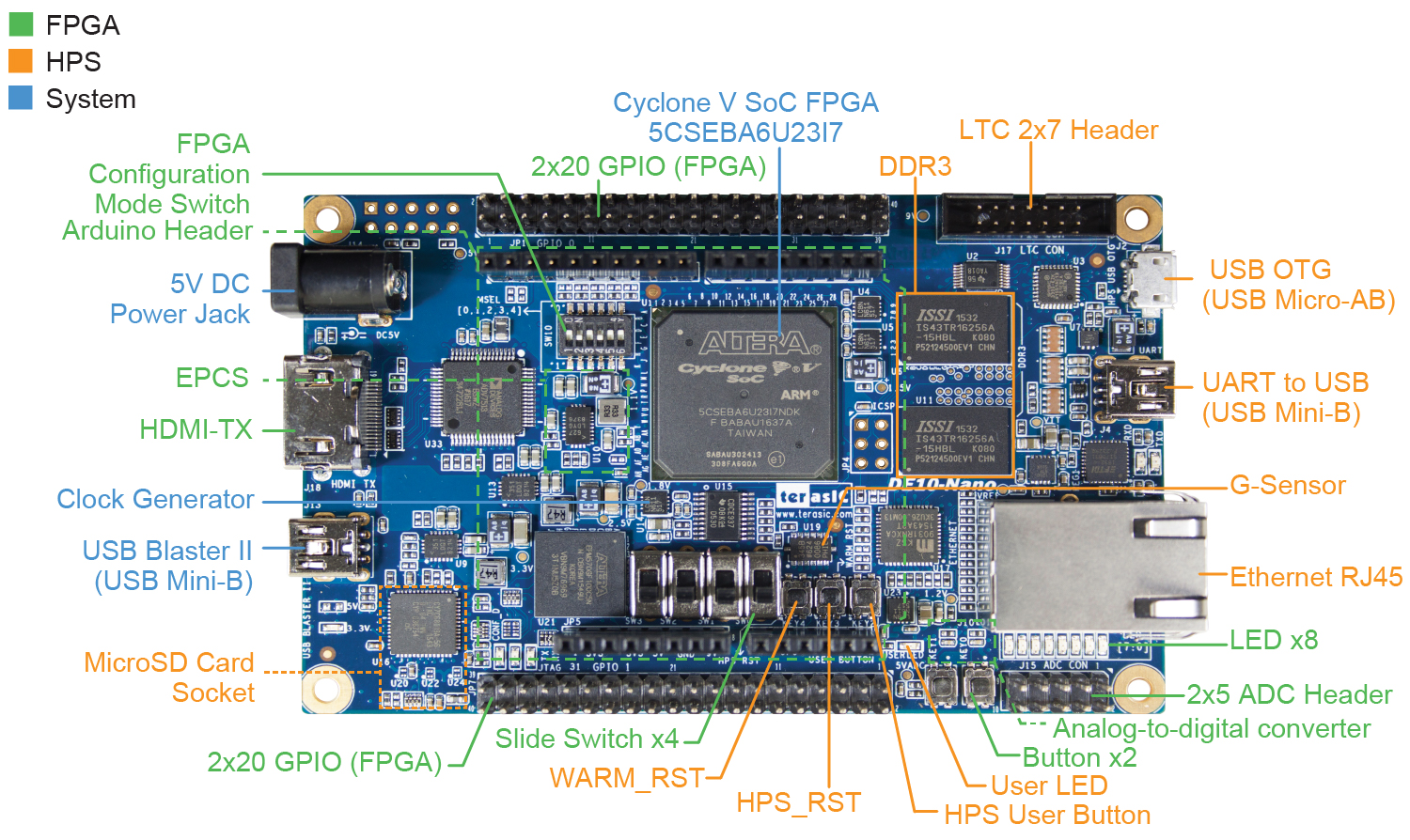

FPGA Cloud Connectivity Kit oparty został na Terasic DE10-Nano. Jest to płytka deweloperska z Cyclone® V SE 5CSEBA6U23I7. Zawiera układ programowalny FPGA, który ma 110 000 elementów logicznych, oraz procesor oparty na architekturze ARM Cortex-A9 o częstotliwości pracy 800 MHz. Płytka dzięki wielu komponentom, jakimi są liczne diody LED, przyciski monostabilne, przełączniki suwakowe, USB-Blaster, SDRAM, akcelerometr, wyjście HDMI oraz listwa wejść i wyjść cyfrowych, to idealne narzędzie do nauki programowania układów FPGA. Płytka również idealnie sprawdzi się do prototypowania projektów związanych z tą tematyką.

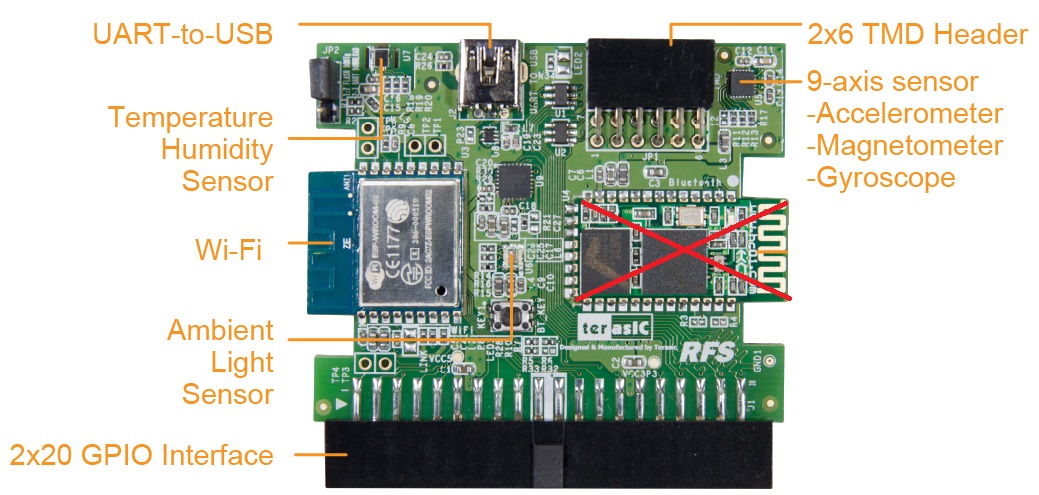

Do zestawu dołączona została płytka z komunikacją bezprzewodową Wi-Fi (ESP_WROOM-02), a także szeroką gamą czujników, takich jak czujniki światła otoczenia, temperatury i wilgotności, akcelerometr i żyroskop.

Uwaga!

Płytka RFS w wersji FCC-WiFi nie ma wbudowanego modułu Bluetooth HC-05. Wersja z modułem BT dostępna jest pod adresem.

Zestaw FPGA Cloud Connectivity Kit umożliwia użytkownikom umieszczenie elastycznego i rekonfigurowalnego układu FPGA w projekcie IoT.

TerasIC DE10-Nano

RFS (FCC-WiFi)

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Zestaw startowy DE10-Nano Kit z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. Terasic P0496

Zestaw startowy DE10-Nano Kit z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. Terasic P0496

Brak towaru

Brak towaru

Terasic NET-FMC to karta rozszerzająca z Gigabajtowym Ethernetem oraz interfejsem FMC. Dzięki temu interfejsowi może być używana z zestawami firmy Terasic. Terasic P0481

Brak towaru

Brak towaru

Moduł pamięci SODIMM firmy TerasIC o pojemności 18MB i częstotliwości pracy 550MHz. Moduł przeznaczony jest do pracy z układami FPGA Intel Stratix 10 w zestawach ewaluacyjnych takich jak TerasIC DE10-Pro-GX-280-4G oraz TerasIC DE10-Pro-GX-280-8G. TerasIC S0534

Brak towaru

Zestaw deweloperski z modułem Apollo S10 oraz płytą bazową. Wyposażony w procesor Intel Stratix 10 SoC z elementami logicznymi 2800K, posiada pamięć DDR4 SDRAM (do 64 GB), wbudowany USB-Blaster II, Ethernet, microSD, miniUSB oraz złącza QSFP i USB typ C. TerasIC Apollo Developer Kit (P0671)

Brak towaru

Brak towaru

[CENA EDUKACYJNA] Zestaw startowy/ewaluacyjny Terasic DE0-Nano Board dla układów FPGA Cyclone IV firmy Altera. Jeden z najmniejszych i najprostszych zestawów startowych dla układów FPGA, wyposażony w podstawowe peryferia, w tym programator-konfigurator JTAG.Obniżona cena (w stosunku do klasycznej wersji Terasic DE0-Nano) dotyczy wyłącznie szkół, uczelni, wykładowców, uczniów i studentów. P0082

Moduł akceleratora obliczeń oparty na układzie FPGA Intel® Agilex™. Ma gniazdo PCI Express Gen 4.0 x16, dwa złącza 200G QSFP-DD i oferuje 32 GB DDR4. Terasic DE10-Agilex (P0701)

Brak towaru

Moduł SoM z układem SoC łączącym FPGA z rdzeniem ARM Cortex-A9. Płytka wyposażona jest w złacze DDR4 Eadge (z zasialniem 3,3 V). Terasic P0553

Brak towaru

Brak towaru

Karta HTG-M przeznaczona jest dla zestawów ewaluacyjnych z układami FPGA, które zostały wyposażone w złącze HSMC (High-Speed Mezzanine connector) lub HSTC (High-Speed Terasic Connector). Karta HTG posiada trzy złącza żeńskie (40-pinowe). Pozwala na konwersje wejść/wyjść HSMC do dwóch 40-pinowych złącz prototypowych lub złącza HSTC do trzech 40-pinowych złącz prototypowych. TerasIC P0024

Brak towaru

VEEK-MT2S to płytka deweloperska oparta na układzie Cyclone V SX SoC Cyclone V SX SoC—5CSXFC6D6F31C6N. W zestawie, oprócz płytki z układem programowalnym FPGA, znajdują się również 7-calowy wyświetlacz TFT dotykowy o rozdzielczości 800 x 480 pikseli, kamera o rozdzielczości 8 Megapikseli (3264 x 2448 pikseli), czujnik światła czujnik IMU 9DOF (akcelerometr, żyroskop, magnetometr). Terasic K0161

Brak towaru

Zestaw ewaluacyjny Terasic DE0 Board dla układów FPGA Cyclone III firmy Altera. Wyposażono go we wszystkie podstawowe peryferia umożliwiające prowadzenie prac badawczych i ewaluacyjnych z układami FPGA, w tym programator-konfigurator JTAG.

Brak towaru

Zestaw startowy DE10-Nano Kit z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. Terasic P0496

Zestaw z płytką FPGA Terasic DE10-Nano oraz modułem WiFi. Przeznaczony do projektów wykorzystujących FPGA do pracy w chmurze. TerasIC P0700