37 395,09 zł Netto

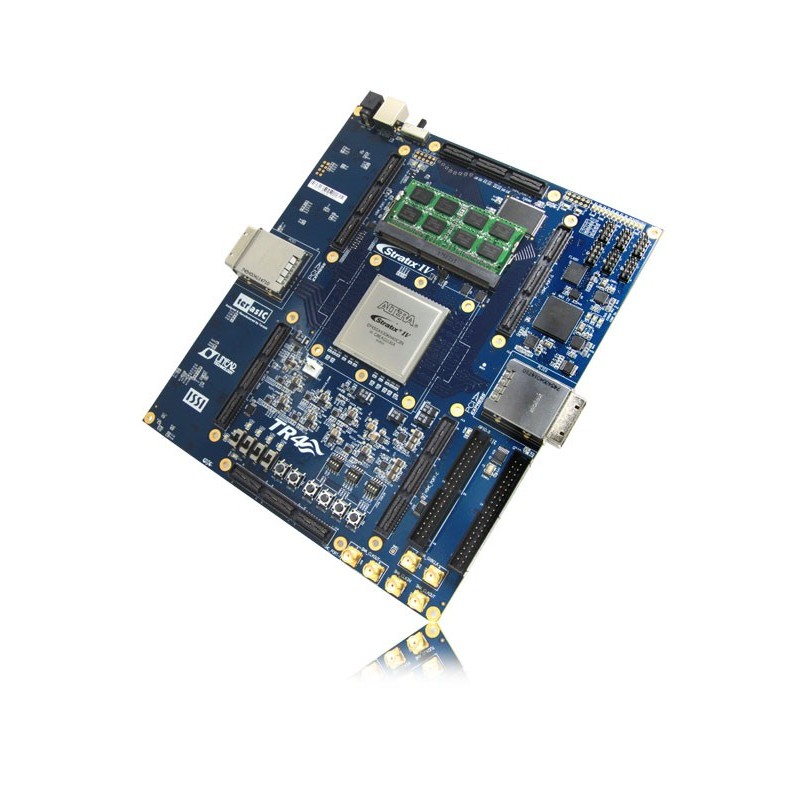

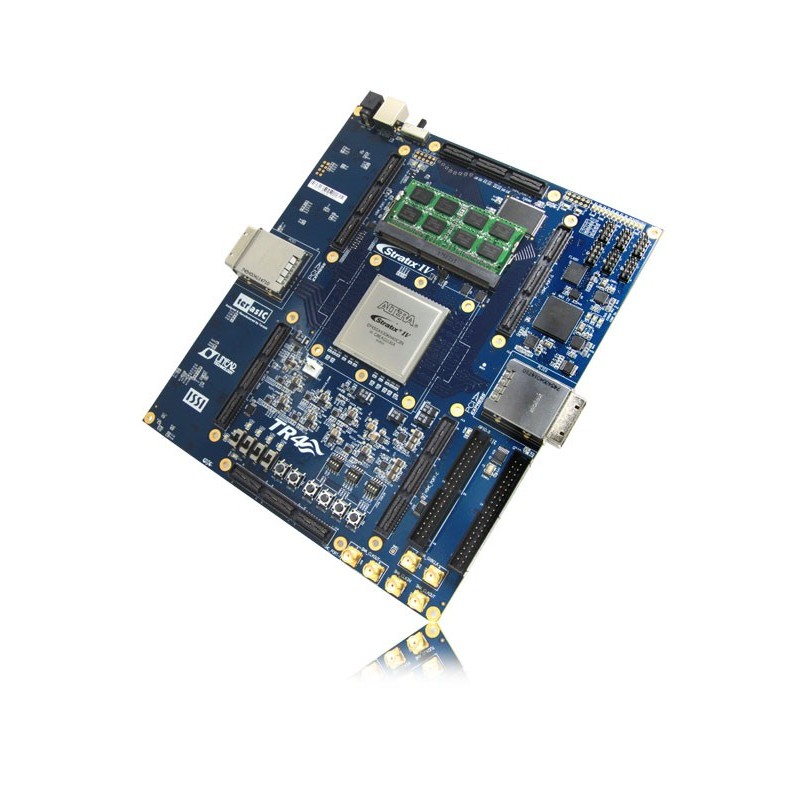

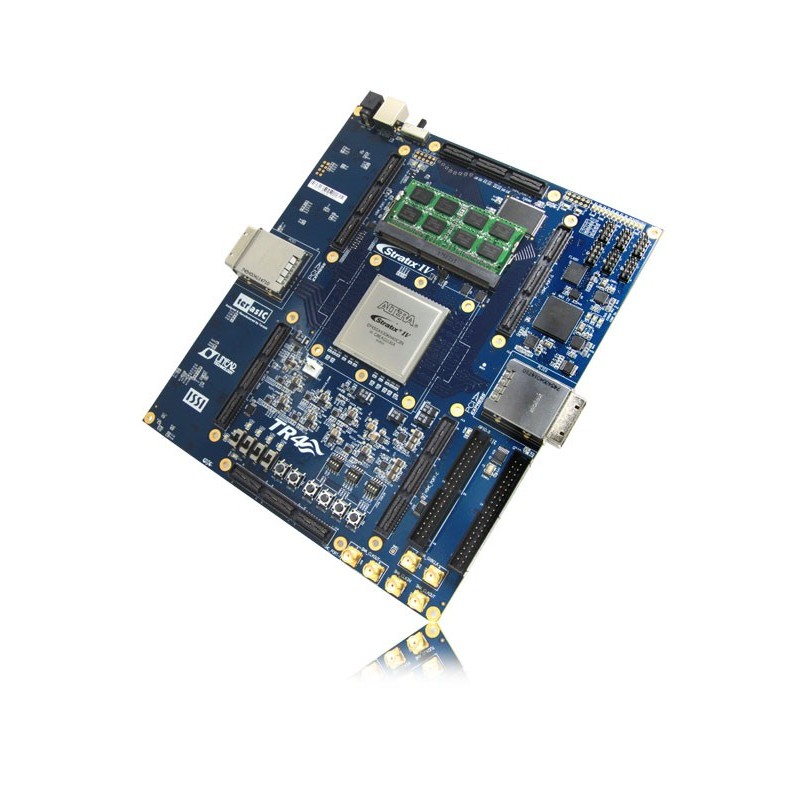

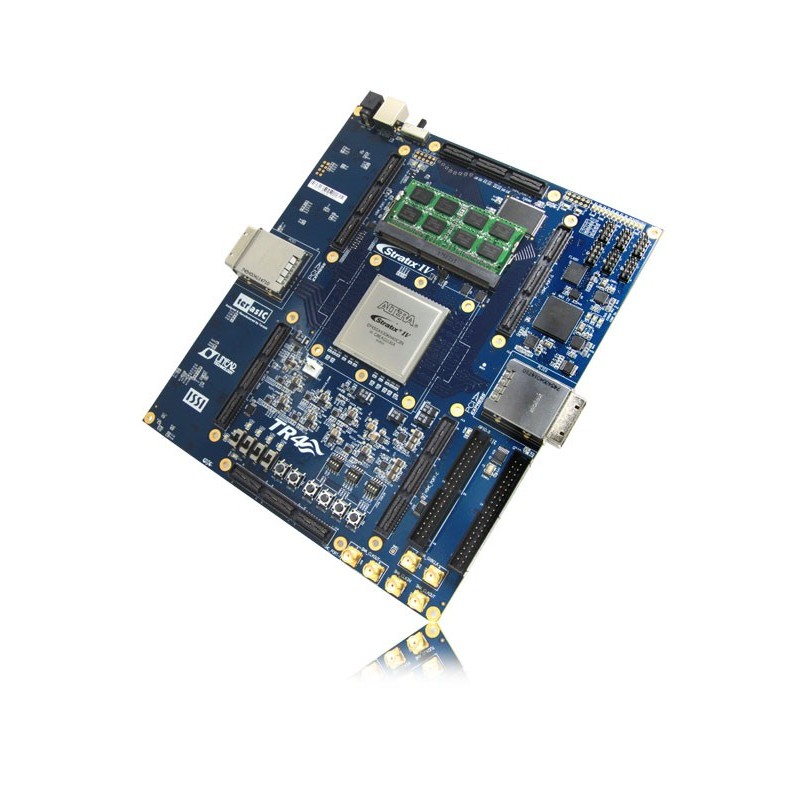

TerasIC TR4-530 (P0109) to zestaw rozwojowy FPGA z układem Stratix IV GX, oferujący wysoką wydajność logiczną, obsługę szybkiej pamięci DDR3 oraz szerokie możliwości rozbudowy przez złącza HSMC i PCIe. Platforma przeznaczona do prototypowania systemów cyfrowych, aplikacji PCI Express i przetwarzania danych w czasie rzeczywistym.

Zestaw rozwojowy TR4-530 oferuje zaawansowaną platformę sprzętową do projektowania systemów wymagających dużej wydajności obliczeniowej, rozbudowanej komunikacji szeregowej oraz zaawansowanego dostępu do pamięci. Płytka oparta na układzie FPGA Intel Stratix IV GX EP4SGX530 wyposażona została w 531 200 elementów logicznych, 1 024 bloków mnożników 18x18 oraz 27 376 Kbit pamięci wewnętrznej. Obsługuje także cztery twarde rdzenie PCIe oraz osiem pętli PLL.

Urządzenie oferuje gniazdo SO-DIMM DDR3 o pojemności do 4 GB z przepustowością teoretyczną do 68 Gb/s. W zestawie dostępna pamięć Flash 64 MB i 2 MB pamięci SSRAM. Płytka posiada sześć złączy HSMC (High Speed Mezzanine Card), które umożliwiają łatwe rozszerzanie funkcjonalności poprzez moduły córki. Złącza te zapewniają łącznie 16 szybkich transceiverów do 6,5 Gb/s oraz 68 kanałów LVDS.

Do komunikacji z komputerem służy wbudowany programator USB Blaster, a konfiguracja FPGA możliwa jest również przez JTAG. Układ zarządzający MAX II CPLD odpowiada za konfigurację oraz kontrolę nad programowalnym generatorem PLL. Zestaw obsługuje zasilanie z zewnętrznego źródła 19 V DC i umożliwia integrację wielu płytek TR4 w systemy wieloukładowe do prototypowania układów ASIC.

Producent BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

TerasIC DVI-HSMC to karta rozszerzeń FPGA z nadajnikiem i odbiornikiem DVI, umożliwiająca obsługę wysokorozdzielczych sygnałów wideo w projektach multimedialnych i systemach przetwarzania obrazu. Dzięki zgodności z platformami Terasic i Altera oferuje szybkie wdrożenie i testowanie aplikacji wizualnych w oparciu o układy FPGA.

TerasIC ICB-HSMC to karta komunikacyjna dla systemów FPGA, wyposażona w interfejsy RS-232, RS-485 i CAN, a także porty GPIO i PIO do rozbudowy. Umożliwia szybkie wdrażanie i testowanie systemów komunikacji przemysłowej oraz implementację magistral polowych w aplikacjach automatyki i sterowania.

Brak towaru

TerasIC NET to moduł Ethernet w standardzie HSMC, umożliwiający szybkie wdrożenie komunikacji sieciowej w systemach FPGA. Dzięki obsłudze prędkości od 10 Mb/s do 1 Gb/s oraz pełnej integracji z układami FPGA stanowi wygodne narzędzie do projektowania aplikacji wymagających niezawodnej komunikacji sieciowej.

Brak towaru

TerasIC USB Blaster Download Cable (UBT) to w pełni zgodny z Altera USB Blaster programator JTAG/ISP dla układów CPLD i FPGA. Dzięki niezawodnej konstrukcji oraz odporności na zakłócenia stanowi uniwersalne narzędzie dla projektantów pracujących z układami programowalnymi Altera. TerasIC P0302

TerasIC ADA-GPIO to karta konwersji AD/DA umożliwiająca współpracę z wieloma płytami FPGA przez interfejsy GPIO i HSMC. Dzięki wysokiej szybkości próbkowania oraz szerokiej kompatybilności doskonale nadaje się do zastosowań DSP, edukacyjnych i komunikacyjnych.

Brak towaru

Karta HTG-M przeznaczona jest dla zestawów ewaluacyjnych z układami FPGA, które zostały wyposażone w złącze HSMC (High-Speed Mezzanine connector) lub HSTC (High-Speed Terasic Connector). Karta HTG posiada trzy złącza męskie (40-pinowe). Pozwala na konwersje wejść/wyjść HSMC do dwóch 40-pinowych złącz prototypowych lub złącza HSTC do trzech 40-pinowych złącz prototypowych. TerasIC P0033

Zestaw TerasIC P0057 umożliwia testowanie, debugowanie i symulację sygnałów w systemach wykorzystujących interfejs HSMC. Przeznaczony do prac projektowych i diagnostycznych z płytami głównymi FPGA i innymi układami wyposażonymi w złącze HSMC.

Brak towaru

Zestaw startowy/ewaluacyjny Terasic DE0-Nano Board dla układów FPGA Cyclone IV firmy Altera. Jest to jeden z najmniejszych i najprostszych i jednocześnie dobrze wyposażonych zestawów startowych dla układów FPGA, jego standardowym wyposażeniem jest programator-konfigurator JTAG.

Brak towaru

[CENA EDUKACYJNA] Zestaw startowy/ewaluacyjny Terasic DE0-Nano Board dla układów FPGA Cyclone IV firmy Altera. Jeden z najmniejszych i najprostszych zestawów startowych dla układów FPGA, wyposażony w podstawowe peryferia, w tym programator-konfigurator JTAG.Obniżona cena (w stosunku do klasycznej wersji Terasic DE0-Nano) dotyczy wyłącznie szkół, uczelni, wykładowców, uczniów i studentów. P0082

Moduł TerasIC HDMI_TX P0084 umożliwia realizację transmisji HDMI z wykorzystaniem interfejsu HSMC w projektach FPGA. Zgodność z najnowszymi standardami HDMI i dostarczony kod źródłowy przyspieszają rozwój oraz testowanie aplikacji wizyjnych i multimedialnych w systemach opartych na układach FPGA.

Brak towaru

Moduł TerasIC HDMI_RX P0083 umożliwia odbiór sygnałów HDMI przez interfejs HSMC w systemach FPGA. Dzięki zgodności ze standardami HDMI i HDCP oraz dostępnemu projektowi referencyjnemu, stanowi kompletne rozwiązanie do implementacji, testowania i analizy transmisji wideo w aplikacjach wbudowanych i systemach przetwarzania obrazu.

Brak towaru

Karta TerasIC AHA-HSMC umożliwia integrację sensorów obrazu Aptina z zestawami FPGA firmy TerasIC wyposażonymi w interfejs HSMC. Zapewnia pełną obsługę komunikacji, transmisji danych i sterowania migawką, stanowiąc kluczowy element w systemach wizyjnych i projektach przetwarzania obrazu w czasie rzeczywistym.

Brak towaru

Moduł TerasIC HDMI v1.4 (P0087) umożliwia implementację pełnego toru nadawczo-odbiorczego HDMI w systemach FPGA. Dzięki obsłudze rozdzielczości Full HD, zgodności z HDMI 1.4a oraz dołączonym projektom referencyjnym, stanowi uniwersalne rozwiązanie do testowania, nauki i wdrażania transmisji wideo w aplikacjach embedded i multimedialnych.

Brak towaru

TerasIC TR4-530 (P0109) to zestaw rozwojowy FPGA z układem Stratix IV GX, oferujący wysoką wydajność logiczną, obsługę szybkiej pamięci DDR3 oraz szerokie możliwości rozbudowy przez złącza HSMC i PCIe. Platforma przeznaczona do prototypowania systemów cyfrowych, aplikacji PCI Express i przetwarzania danych w czasie rzeczywistym.

Brak towaru

TerasIC TR4-230 (P0107) oferuje platformę rozwojową opartą na FPGA Stratix IV GX z szerokim zakresem interfejsów oraz wsparciem dla projektów PCI Express i szybkiej pamięci DDR3. Rozwiązanie przeznaczone do budowy systemów komunikacyjnych, prototypowania ASIC oraz aplikacji o wysokim zapotrzebowaniu na zasoby logiczne.

Brak towaru

TerasIC CLR-HSMC (P0079) umożliwia integrację kamer przemysłowych z interfejsem Camera Link z płytami FPGA przez złącze HSMC, wspierając przesył obrazu w trybach base, medium i dual base. Moduł znajduje zastosowanie w systemach wizyjnych, liniach produkcyjnych oraz projektach z przetwarzaniem obrazu w czasie rzeczywistym.

Brak towaru

TerasIC TR4-530 (P0109) to zestaw rozwojowy FPGA z układem Stratix IV GX, oferujący wysoką wydajność logiczną, obsługę szybkiej pamięci DDR3 oraz szerokie możliwości rozbudowy przez złącza HSMC i PCIe. Platforma przeznaczona do prototypowania systemów cyfrowych, aplikacji PCI Express i przetwarzania danych w czasie rzeczywistym.