546,98 zł Netto

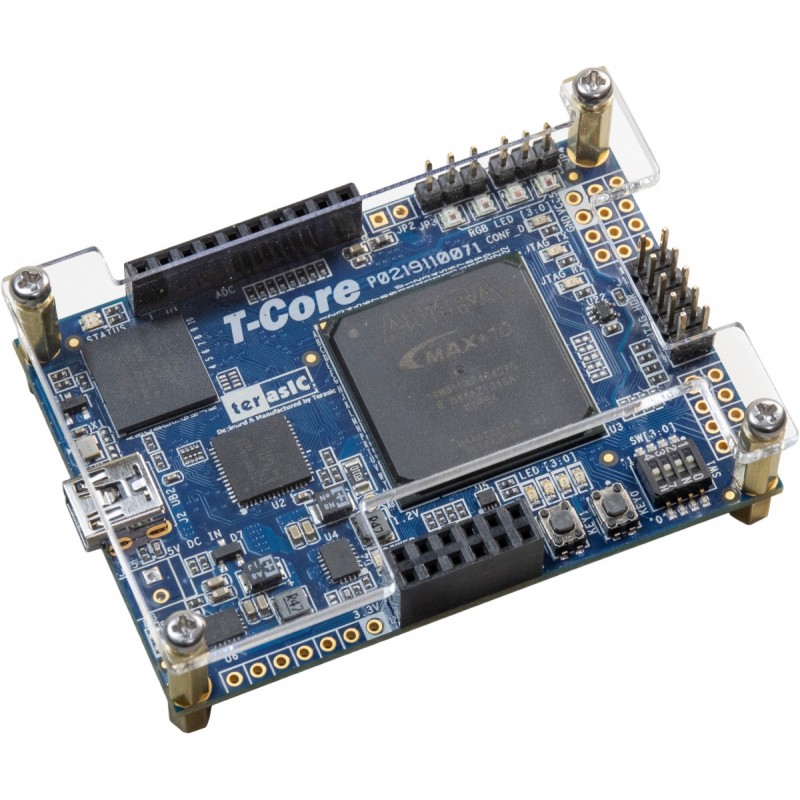

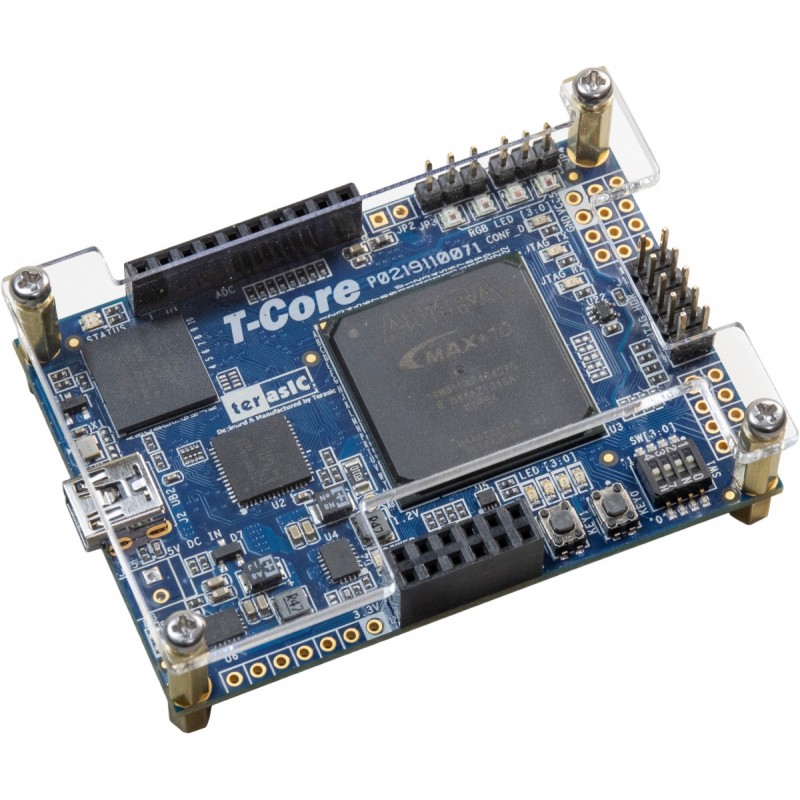

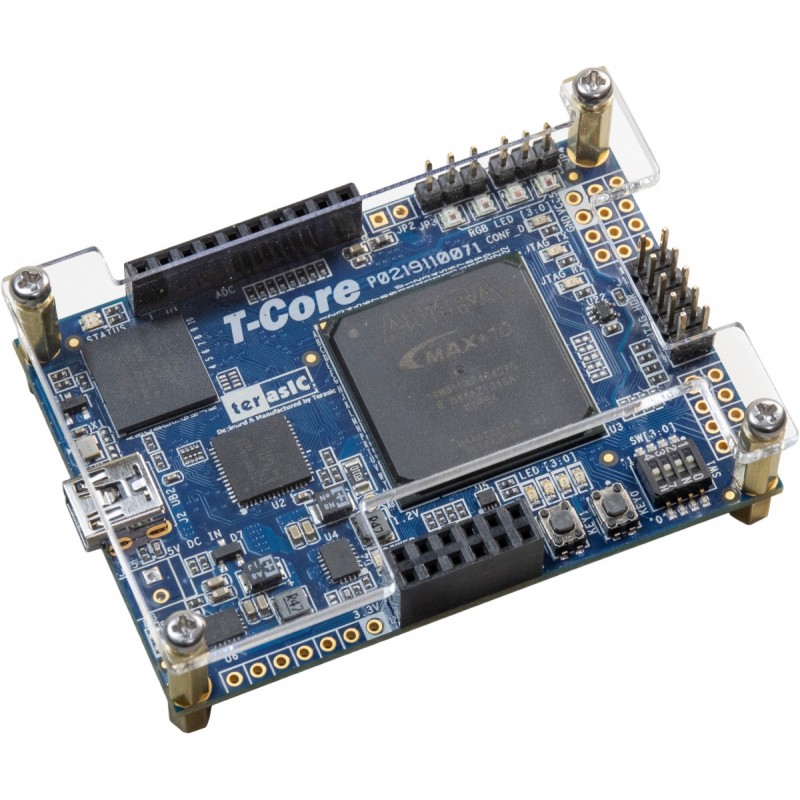

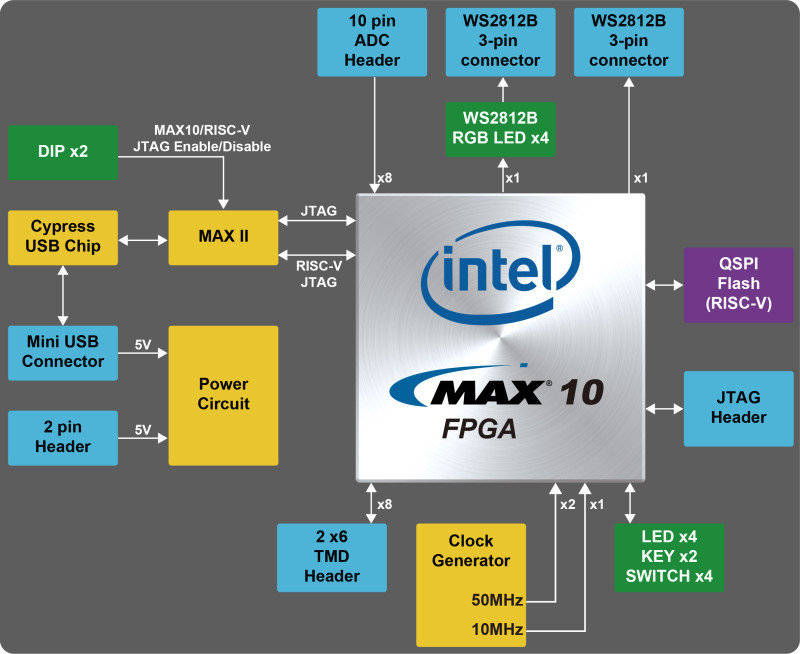

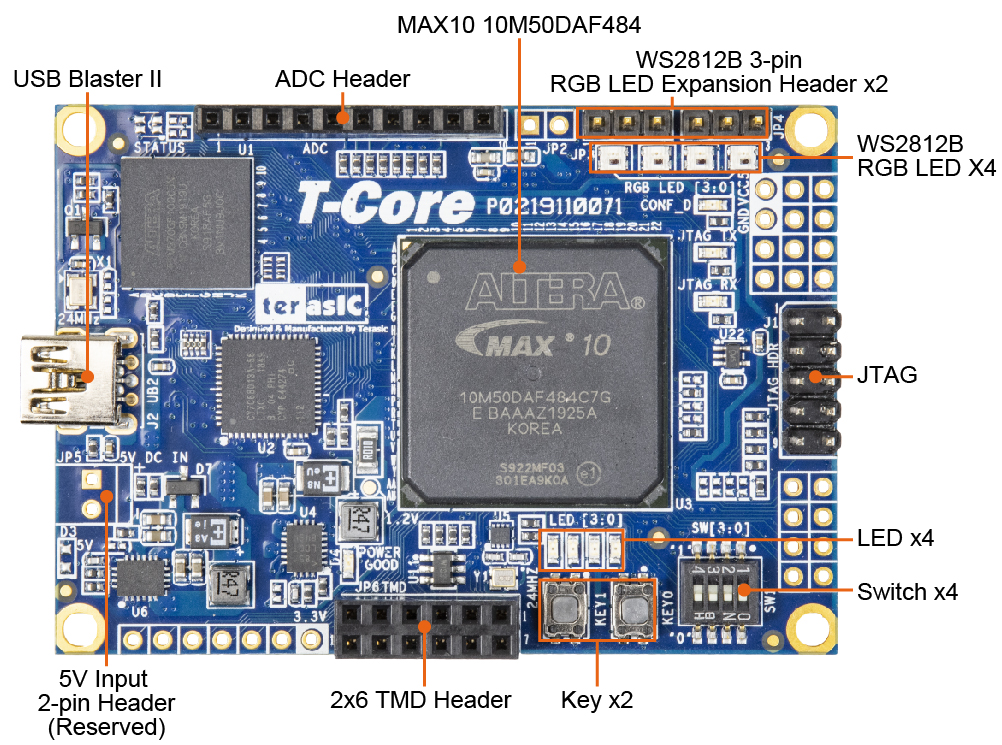

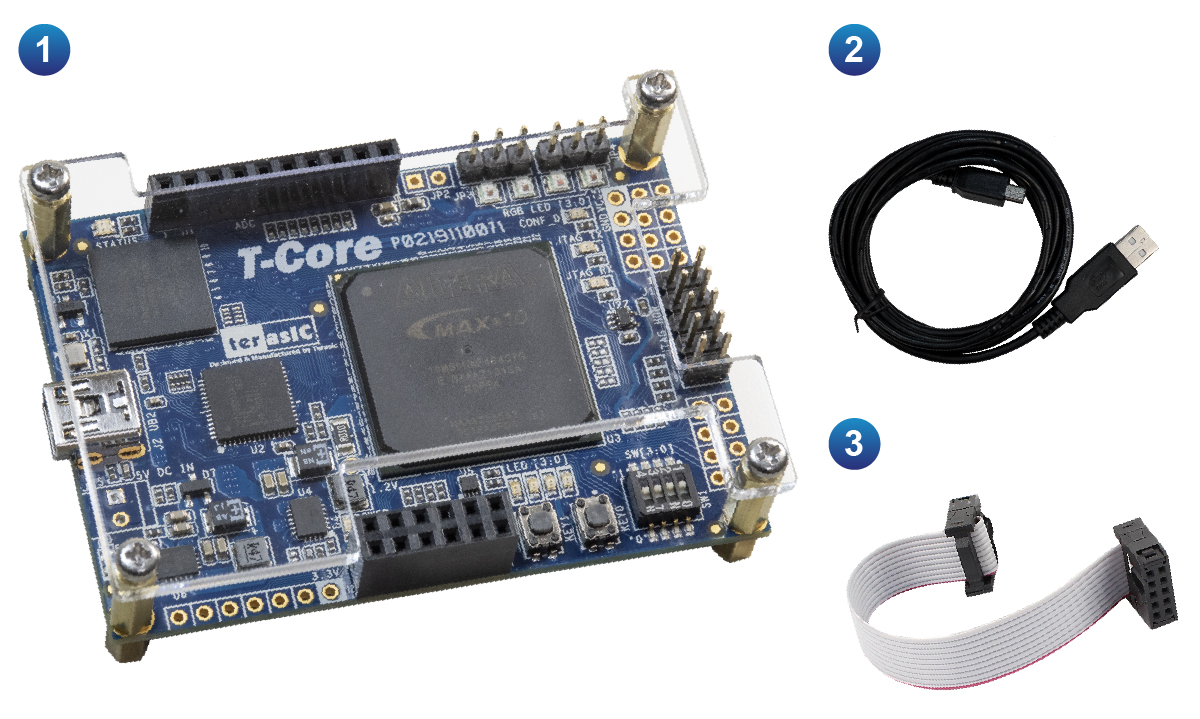

Platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. Wersja edukacyjna. TerasIC T-Core P0633

Oferta przeznaczona wyłącznie dla odbiorców akademickich (studentów i wykładowców wyższych uczelni)!

Składając zamówienie należy podać:

- imię i nazwisko użytkownika

- stanowisko

- adres e-mail użytkownika (adres e-mail musi być z domeny uczelni)

- pełną nazwę uczelni

- nazwę wydziału/instytutu/zakładu dydaktycznego

- adres uczelni

- stronę internetową uczelni

- telefon

- zastosowanie produktu

TerasIC T-Core to platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka rozwojowa T-Core zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. T-Core jest zatem idealnym rozwiązaniem do prototypowania możliwości Intel MAX 10 FPGA.

MAX 10 FPGA pozwala na uzyskanie niższego zużycia energii i wyższą wydajności niż poprzednia generacja. T-Core obsługuje również procesor RISC-V z wbudowanym debugowaniem JTAG. Jest to idealna platforma do nauki projektowania procesorów RISC-V lub projektowania systemów wbudowanych.

Nie jesteś powiązany z żadną uczelnią, lub jesteś klientem biznesowym? Sprawdź:

TerasIC T-Core - zestaw rozwojowy z układem FPGA Intel MAX 10

Producent BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

[CENA EDUKACYJNA] Zestaw startowy/ewaluacyjny Terasic DE0-Nano Board dla układów FPGA Cyclone IV firmy Altera. Jeden z najmniejszych i najprostszych zestawów startowych dla układów FPGA, wyposażony w podstawowe peryferia, w tym programator-konfigurator JTAG.Obniżona cena (w stosunku do klasycznej wersji Terasic DE0-Nano) dotyczy wyłącznie szkół, uczelni, wykładowców, uczniów i studentów. P0082

TerasIC TR4-530 (P0109) to zestaw rozwojowy FPGA z układem Stratix IV GX, oferujący wysoką wydajność logiczną, obsługę szybkiej pamięci DDR3 oraz szerokie możliwości rozbudowy przez złącza HSMC i PCIe. Platforma przeznaczona do prototypowania systemów cyfrowych, aplikacji PCI Express i przetwarzania danych w czasie rzeczywistym.

Brak towaru

MAX 10 Plus jest zestawem deweloperskim opartym o układ FPGA od Intela, wyposażony w 50 000 programowalnych elementów logicznych. Digilent P0638

Brak towaru

Platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. TerasIC T-Core P0633

Brak towaru

MAX 10 Plus jest zestawem deweloperskim opartym o układ FPGA od Intela, wyposażony w 50 000 programowalnych elementów logicznych. Digilent P0638

Brak towaru

Moduł XTS-FMC jest rozszerzeniem dla układów FPGA pozwalającym na dostęp do kanałów/interfejsów komunikacyjnych poprzez złącze SMA. TerasIC P0401

Brak towaru

[CENA EDUKACYJNA] Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE oraz minikomputer z układem Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). Moduł FPGA posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0650

Brak towaru

Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE oraz minikomputer z układem Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). Moduł FPGA posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0650

Brak towaru

Platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. TerasIC T-Core P0633

Brak towaru

Platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. Wersja edukacyjna. TerasIC T-Core P0633

Brak towaru

Kompaktowy zestaw FPGA z układem Intel Arria 10 GX wyposażony w 8 GB pamięci DDR4-2133 oraz złącze komunikacyjne Thunderbolt 3. Może być zastosowany bezpośrednio na laptopach lub innych urządzeniach przenośnych. Terasic FLIK P0642

Brak towaru

Kompaktowy zestaw FPGA z układem Intel Arria 10 GX wyposażony w 8 GB pamięci DDR4-2133 oraz złącze komunikacyjne Thunderbolt 3. Może być zastosowany bezpośrednio na laptopach lub innych urządzeniach przenośnych. Wersja edukacyjna. Terasic FLIK P0642

Brak towaru

Moduł ewaluacyjny z procesorem Intel Stratix 10 SoC z elementami logicznymi 2800K. Moduł posiada pamięć DDR4 SDRAM (do 64 GB), wbudowany USB-Blaster II, Ethernet, microSD, miniUSB oraz złącza FMC/FMC+ do rozbudowy. TerasIC Apollo S10 SoM Board (P0630)

Brak towaru

Zestaw deweloperski z modułem Apollo S10 oraz płytą bazową. Wyposażony w procesor Intel Stratix 10 SoC z elementami logicznymi 2800K, posiada pamięć DDR4 SDRAM (do 64 GB), wbudowany USB-Blaster II, Ethernet, microSD, miniUSB oraz złącza QSFP i USB typ C. TerasIC Apollo Developer Kit (P0671)

Brak towaru

Zestaw startowy FPGA z układem Intel Stratix 10 SX. Moduł posiada zintegrowane urządzenia nadawczo-odbiorcze, które przesyłają dane z prędkością do 28,3 Gb/s, dzięki czemu DE10-Pro jest w pełni zgodny z wersją 3.0 standardu PCI Express. DE10-Pro oferuje szybką pamięć równoległą Flash i cztery pamięci SO-DIMM, które mają 4 GB DDR4 SDRAM. Terasic P0627

Brak towaru

Zestaw startowy FPGA z układem Intel Stratix 10 SX. Moduł posiada zintegrowane urządzenia nadawczo-odbiorcze, które przesyłają dane z prędkością do 28,3 Gb/s, dzięki czemu DE10-Pro jest w pełni zgodny z wersją 3.0 standardu PCI Express. DE10-Pro oferuje szybką pamięć równoległą Flash i cztery pamięci SO-DIMM, które mają 8 GB DDR4 SDRAM. Terasic P0629

Brak towaru

Moduł akceleratora obliczeń oparty na układzie FPGA Intel® Agilex™. Ma gniazdo PCI Express Gen 4.0 x16, dwa złącza 200G QSFP-DD i oferuje 32 GB DDR4. Terasic DE10-Agilex (P0701)

Brak towaru

Zestaw z płytką FPGA Terasic DE10-Nano oraz modułem WiFi. Przeznaczony do projektów wykorzystujących FPGA do pracy w chmurze. TerasIC P0700

Brak towaru

Płytka ewaluacyjna z układem Intel Agilex SoC z 1400 tys. elementów logicznych. Moduł ma dwa gniazda pamięci DDR4 SO-DIMM (do 32 GB), złącze QSFP28, PCIe Gen 4x16, wbudowany USB-Blaster II oraz złącza FMC/FMC+ do rozbudowy. TerasIC Apollo Agilex SOM (P0714)

Brak towaru

Terasic Atum A5 Development Kit – zaawansowany zestaw FPGA Intel Agilex 5 do AI, systemów wizyjnych i aplikacji wymagających dużej przepustowości. Terasic Atum 5 Development Kit

Brak towaru

Platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. Wersja edukacyjna. TerasIC T-Core P0633