814,32 zł Netto

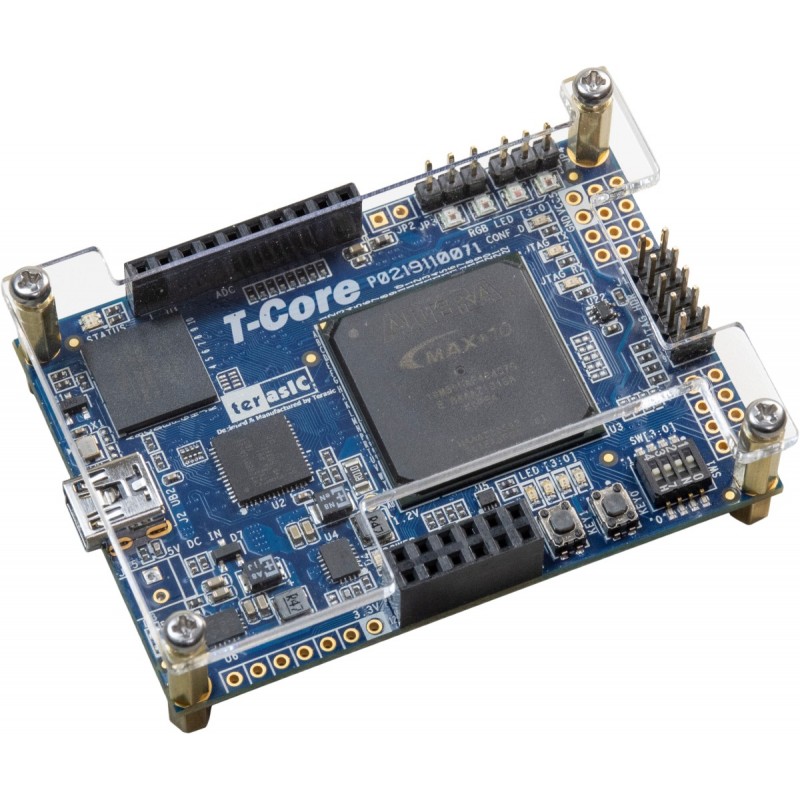

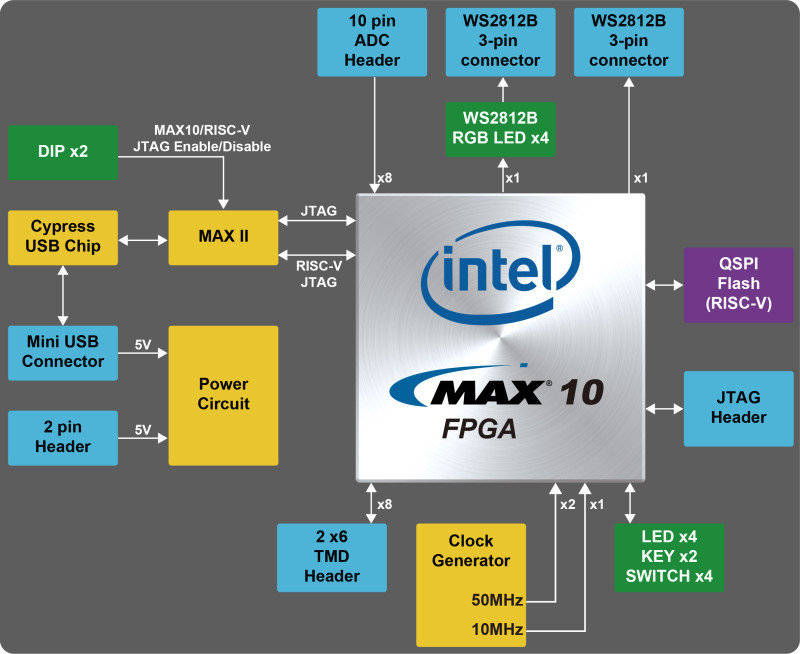

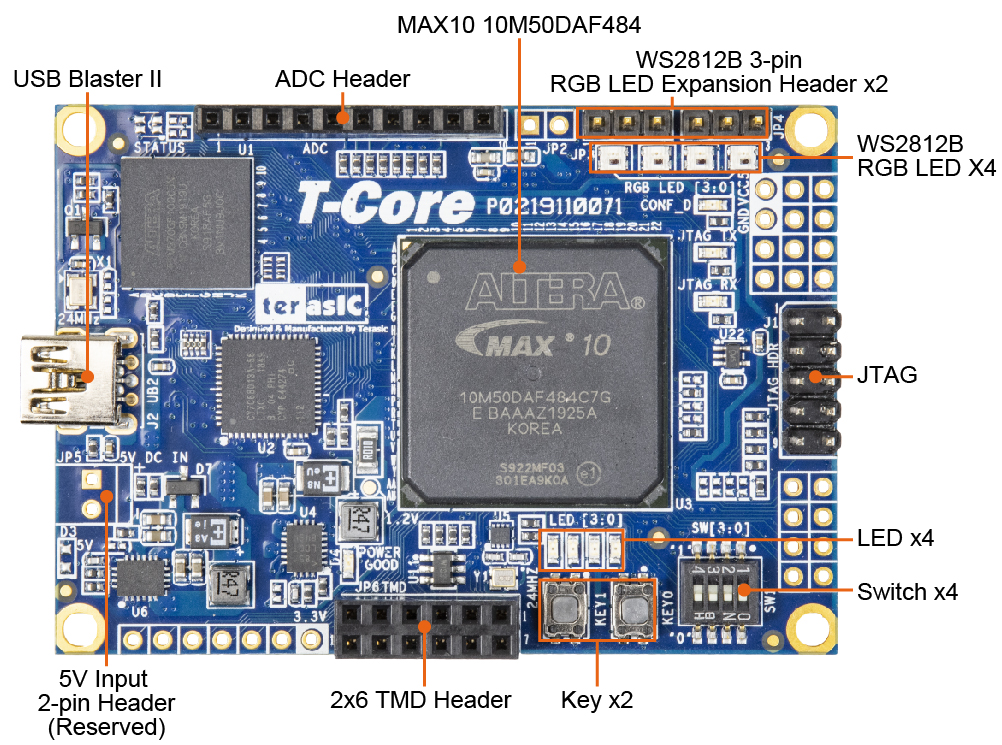

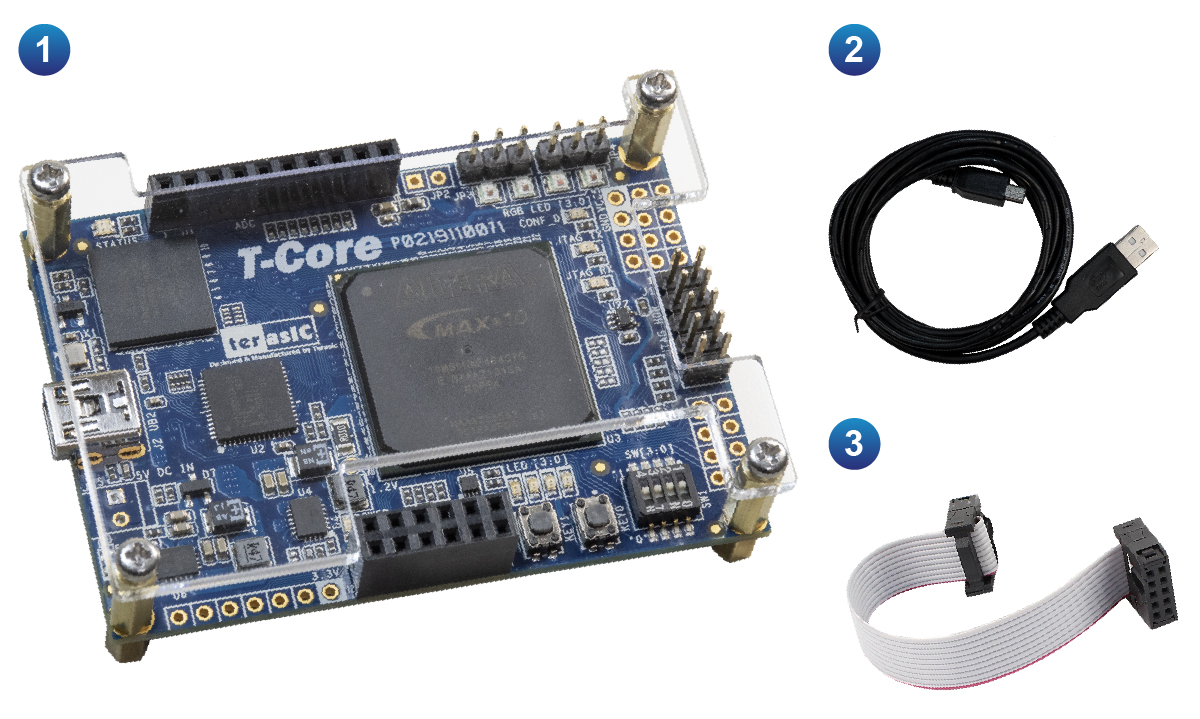

Platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. TerasIC T-Core P0633

TerasIC T-Core to platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka rozwojowa T-Core zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. T-Core jest zatem idealnym rozwiązaniem do prototypowania możliwości Intel MAX 10 FPGA.

MAX 10 FPGA pozwala na uzyskanie niższego zużycia energii i wyższą wydajności niż poprzednia generacja. T-Core obsługuje również procesor RISC-V z wbudowanym debugowaniem JTAG. Jest to idealna platforma do nauki projektowania procesorów RISC-V lub projektowania systemów wbudowanych.

Produkt dostępny również w ofercie akademickiej (EDU) w obniżonej cenie: TerasIC T-Core - zestaw rozwojowy z układem FPGA Intel MAX 10 - EDU

Producent BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

[CENA EDUKACYJNA] Zestaw startowy/ewaluacyjny Terasic DE0-Nano Board dla układów FPGA Cyclone IV firmy Altera. Jeden z najmniejszych i najprostszych zestawów startowych dla układów FPGA, wyposażony w podstawowe peryferia, w tym programator-konfigurator JTAG.Obniżona cena (w stosunku do klasycznej wersji Terasic DE0-Nano) dotyczy wyłącznie szkół, uczelni, wykładowców, uczniów i studentów. P0082

TerasIC TR4-530 (P0109) to zestaw rozwojowy FPGA z układem Stratix IV GX, oferujący wysoką wydajność logiczną, obsługę szybkiej pamięci DDR3 oraz szerokie możliwości rozbudowy przez złącza HSMC i PCIe. Platforma przeznaczona do prototypowania systemów cyfrowych, aplikacji PCI Express i przetwarzania danych w czasie rzeczywistym.

Brak towaru

MAX 10 Plus jest zestawem deweloperskim opartym o układ FPGA od Intela, wyposażony w 50 000 programowalnych elementów logicznych. Digilent P0638

Brak towaru

Platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. Wersja edukacyjna. TerasIC T-Core P0633

Brak towaru

TerasIC DE0 to kompletny zestaw ewaluacyjny oparty na FPGA Cyclone III, zaprojektowany do nauki, testowania i wdrażania systemów cyfrowych. Oferuje szeroki zestaw interfejsów i peryferiów umożliwiających tworzenie złożonych projektów zarówno edukacyjnych, jak i przemysłowych.

Brak towaru

[CENA EDUKACYJNA] Zestaw ewaluacyjny Terasic DE0 Board dla układów FPGA Cyclone III firmy Altera. Wyposażono go we wszystkie podstawowe peryferia umożliwiające prowadzenie prac badawczych i ewaluacyjnych z układami FPGA, w tym programator-konfigurator JTAG. Obniżona cena (w stosunku do klasycznej wersji Terasic DE0) dotyczy wyłącznie szkół, uczelni, wykładowców, uczniów i studentów.

Zestaw startowy/ewaluacyjny Terasic DE0-Nano Board dla układów FPGA Cyclone IV firmy Altera. Jest to jeden z najmniejszych i najprostszych i jednocześnie dobrze wyposażonych zestawów startowych dla układów FPGA, jego standardowym wyposażeniem jest programator-konfigurator JTAG.

Brak towaru

[CENA EDUKACYJNA] Zestaw startowy/ewaluacyjny Terasic DE0-Nano Board dla układów FPGA Cyclone IV firmy Altera. Jeden z najmniejszych i najprostszych zestawów startowych dla układów FPGA, wyposażony w podstawowe peryferia, w tym programator-konfigurator JTAG.Obniżona cena (w stosunku do klasycznej wersji Terasic DE0-Nano) dotyczy wyłącznie szkół, uczelni, wykładowców, uczniów i studentów. P0082

Karta TerasIC AHA-HSMC umożliwia integrację sensorów obrazu Aptina z zestawami FPGA firmy TerasIC wyposażonymi w interfejs HSMC. Zapewnia pełną obsługę komunikacji, transmisji danych i sterowania migawką, stanowiąc kluczowy element w systemach wizyjnych i projektach przetwarzania obrazu w czasie rzeczywistym.

Brak towaru

Moduł TerasIC HDMI v1.4 (P0087) umożliwia implementację pełnego toru nadawczo-odbiorczego HDMI w systemach FPGA. Dzięki obsłudze rozdzielczości Full HD, zgodności z HDMI 1.4a oraz dołączonym projektom referencyjnym, stanowi uniwersalne rozwiązanie do testowania, nauki i wdrażania transmisji wideo w aplikacjach embedded i multimedialnych.

Brak towaru

TerasIC TR4-530 (P0109) to zestaw rozwojowy FPGA z układem Stratix IV GX, oferujący wysoką wydajność logiczną, obsługę szybkiej pamięci DDR3 oraz szerokie możliwości rozbudowy przez złącza HSMC i PCIe. Platforma przeznaczona do prototypowania systemów cyfrowych, aplikacji PCI Express i przetwarzania danych w czasie rzeczywistym.

Brak towaru

TerasIC TR4-230 (P0107) oferuje platformę rozwojową opartą na FPGA Stratix IV GX z szerokim zakresem interfejsów oraz wsparciem dla projektów PCI Express i szybkiej pamięci DDR3. Rozwiązanie przeznaczone do budowy systemów komunikacyjnych, prototypowania ASIC oraz aplikacji o wysokim zapotrzebowaniu na zasoby logiczne.

Brak towaru

TerasIC CLR-HSMC (P0079) umożliwia integrację kamer przemysłowych z interfejsem Camera Link z płytami FPGA przez złącze HSMC, wspierając przesył obrazu w trybach base, medium i dual base. Moduł znajduje zastosowanie w systemach wizyjnych, liniach produkcyjnych oraz projektach z przetwarzaniem obrazu w czasie rzeczywistym.

Brak towaru

TerasIC XSFP/SFP+HSMC (P0092) umożliwia budowę systemów Ethernet 10G opartych na interfejsie XAUI z dwoma kanałami SFP+ i zegarem referencyjnym 156,25 MHz. Moduł przeznaczony do integracji z płytami FPGA posiadającymi złącze HSMC, m.in. Stratix IV GX i DE4, znajduje zastosowanie w projektach sieciowych, transmisji danych oraz testach interfejsów wysokiej przepustowości.

Brak towaru

Stratix V GX FPGA Video Development System

Brak towaru

Cyclone V E FPGA Video Development System

Brak towaru

Płytka TerasIC C5G (P0150) umożliwia rozwój zaawansowanych aplikacji FPGA wymagających wysokiej przepustowości i elastycznej komunikacji. Płytka sprawdza się w projektach badawczo-rozwojowych, telekomunikacyjnych i przemysłowych, gdzie istotne pozostają wydajność, dostęp do szybkich interfejsów oraz kompatybilność z narzędziami projektowymi Cyclone V.

Brak towaru

Wszechstronna i niezwykle popularna platforma do nauki oraz rozwoju projektów opartych o architekturę ARM + FPGA. Dzięki bogatemu wyposażeniu, dużej ilości pamięci, licznym interfejsom oraz wsparciu narzędzi firmy Intel/Altera, płytka doskonale sprawdzi się w edukacji akademickiej, badaniach naukowych oraz prototypowaniu zaawansowanych systemów wbudowanych i multimedialnych. To idealny wybór dla studentów, inżynierów i hobbystów chcących poznać pełne możliwości systemów SoC.DE1-SoC Development Kit

Brak towaru

Platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. TerasIC T-Core P0633