546,98 zł Netto

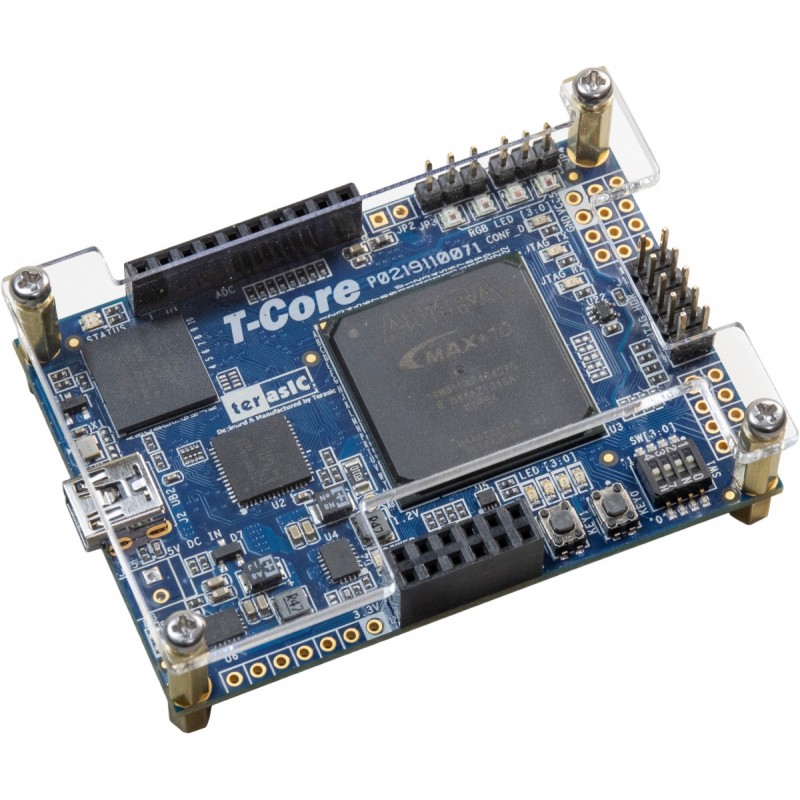

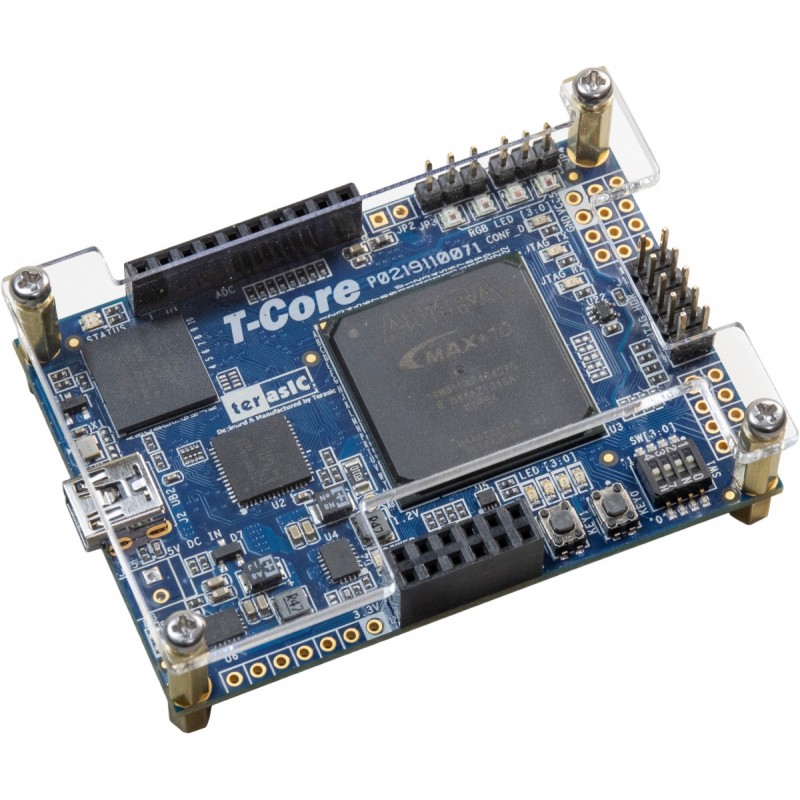

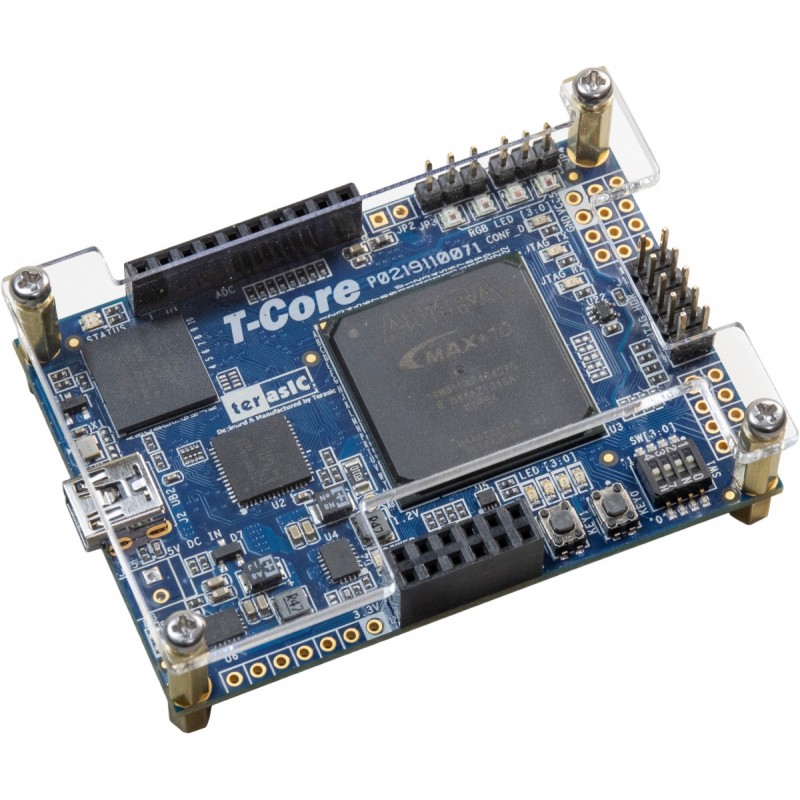

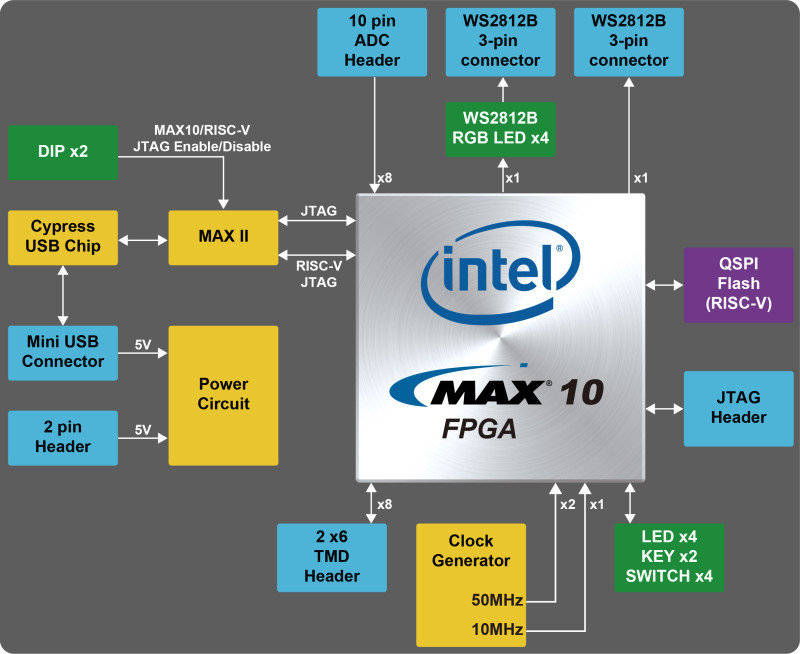

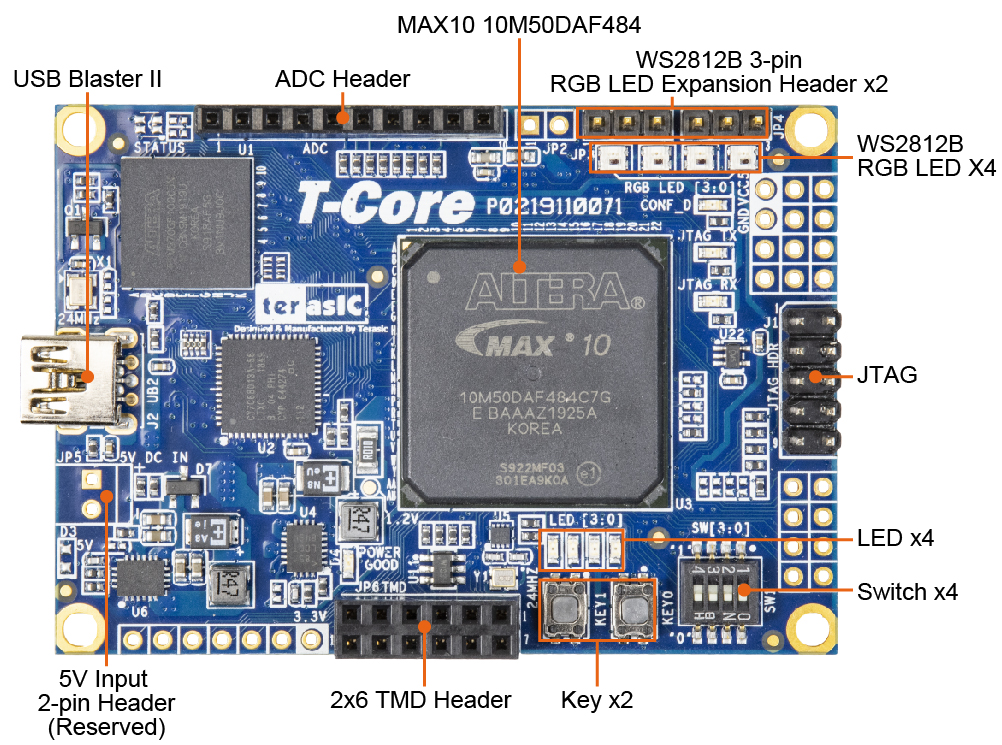

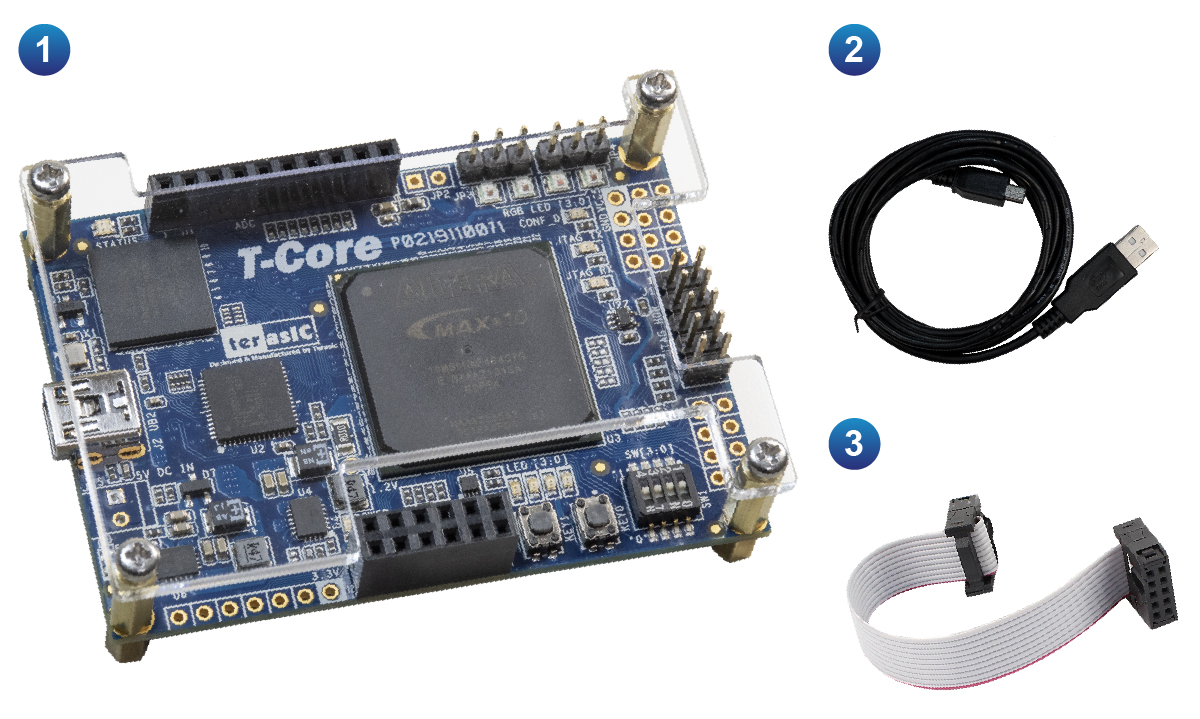

Platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. Wersja edukacyjna. TerasIC T-Core P0633

Oferta przeznaczona wyłącznie dla odbiorców akademickich (studentów i wykładowców wyższych uczelni)!

Składając zamówienie należy podać:

- imię i nazwisko użytkownika

- stanowisko

- adres e-mail użytkownika (adres e-mail musi być z domeny uczelni)

- pełną nazwę uczelni

- nazwę wydziału/instytutu/zakładu dydaktycznego

- adres uczelni

- stronę internetową uczelni

- telefon

- zastosowanie produktu

TerasIC T-Core to platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka rozwojowa T-Core zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. T-Core jest zatem idealnym rozwiązaniem do prototypowania możliwości Intel MAX 10 FPGA.

MAX 10 FPGA pozwala na uzyskanie niższego zużycia energii i wyższą wydajności niż poprzednia generacja. T-Core obsługuje również procesor RISC-V z wbudowanym debugowaniem JTAG. Jest to idealna platforma do nauki projektowania procesorów RISC-V lub projektowania systemów wbudowanych.

Nie jesteś powiązany z żadną uczelnią, lub jesteś klientem biznesowym? Sprawdź:

TerasIC T-Core - zestaw rozwojowy z układem FPGA Intel MAX 10

Producent BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

[CENA EDUKACYJNA] Zestaw startowy/ewaluacyjny Terasic DE0-Nano Board dla układów FPGA Cyclone IV firmy Altera. Jeden z najmniejszych i najprostszych zestawów startowych dla układów FPGA, wyposażony w podstawowe peryferia, w tym programator-konfigurator JTAG.Obniżona cena (w stosunku do klasycznej wersji Terasic DE0-Nano) dotyczy wyłącznie szkół, uczelni, wykładowców, uczniów i studentów. P0082

TerasIC TR4-530 (P0109) to zestaw rozwojowy FPGA z układem Stratix IV GX, oferujący wysoką wydajność logiczną, obsługę szybkiej pamięci DDR3 oraz szerokie możliwości rozbudowy przez złącza HSMC i PCIe. Platforma przeznaczona do prototypowania systemów cyfrowych, aplikacji PCI Express i przetwarzania danych w czasie rzeczywistym.

Brak towaru

MAX 10 Plus jest zestawem deweloperskim opartym o układ FPGA od Intela, wyposażony w 50 000 programowalnych elementów logicznych. Digilent P0638

Brak towaru

Platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. TerasIC T-Core P0633

Brak towaru

TerasIC NET to moduł Ethernet w standardzie HSMC, umożliwiający szybkie wdrożenie komunikacji sieciowej w systemach FPGA. Dzięki obsłudze prędkości od 10 Mb/s do 1 Gb/s oraz pełnej integracji z układami FPGA stanowi wygodne narzędzie do projektowania aplikacji wymagających niezawodnej komunikacji sieciowej.

Brak towaru

TerasIC USB Blaster Download Cable (UBT) to w pełni zgodny z Altera USB Blaster programator JTAG/ISP dla układów CPLD i FPGA. Dzięki niezawodnej konstrukcji oraz odporności na zakłócenia stanowi uniwersalne narzędzie dla projektantów pracujących z układami programowalnymi Altera. TerasIC P0302

TerasIC ADA-GPIO to karta konwersji AD/DA umożliwiająca współpracę z wieloma płytami FPGA przez interfejsy GPIO i HSMC. Dzięki wysokiej szybkości próbkowania oraz szerokiej kompatybilności doskonale nadaje się do zastosowań DSP, edukacyjnych i komunikacyjnych.

Brak towaru

Karta HTG-M przeznaczona jest dla zestawów ewaluacyjnych z układami FPGA, które zostały wyposażone w złącze HSMC (High-Speed Mezzanine connector) lub HSTC (High-Speed Terasic Connector). Karta HTG posiada trzy złącza męskie (40-pinowe). Pozwala na konwersje wejść/wyjść HSMC do dwóch 40-pinowych złącz prototypowych lub złącza HSTC do trzech 40-pinowych złącz prototypowych. TerasIC P0033

Zestaw TerasIC P0057 umożliwia testowanie, debugowanie i symulację sygnałów w systemach wykorzystujących interfejs HSMC. Przeznaczony do prac projektowych i diagnostycznych z płytami głównymi FPGA i innymi układami wyposażonymi w złącze HSMC.

Brak towaru

Zestaw startowy/ewaluacyjny Terasic DE0-Nano Board dla układów FPGA Cyclone IV firmy Altera. Jest to jeden z najmniejszych i najprostszych i jednocześnie dobrze wyposażonych zestawów startowych dla układów FPGA, jego standardowym wyposażeniem jest programator-konfigurator JTAG.

Brak towaru

[CENA EDUKACYJNA] Zestaw startowy/ewaluacyjny Terasic DE0-Nano Board dla układów FPGA Cyclone IV firmy Altera. Jeden z najmniejszych i najprostszych zestawów startowych dla układów FPGA, wyposażony w podstawowe peryferia, w tym programator-konfigurator JTAG.Obniżona cena (w stosunku do klasycznej wersji Terasic DE0-Nano) dotyczy wyłącznie szkół, uczelni, wykładowców, uczniów i studentów. P0082

Moduł TerasIC HDMI_TX P0084 umożliwia realizację transmisji HDMI z wykorzystaniem interfejsu HSMC w projektach FPGA. Zgodność z najnowszymi standardami HDMI i dostarczony kod źródłowy przyspieszają rozwój oraz testowanie aplikacji wizyjnych i multimedialnych w systemach opartych na układach FPGA.

Brak towaru

Moduł TerasIC HDMI_RX P0083 umożliwia odbiór sygnałów HDMI przez interfejs HSMC w systemach FPGA. Dzięki zgodności ze standardami HDMI i HDCP oraz dostępnemu projektowi referencyjnemu, stanowi kompletne rozwiązanie do implementacji, testowania i analizy transmisji wideo w aplikacjach wbudowanych i systemach przetwarzania obrazu.

Brak towaru

Karta TerasIC AHA-HSMC umożliwia integrację sensorów obrazu Aptina z zestawami FPGA firmy TerasIC wyposażonymi w interfejs HSMC. Zapewnia pełną obsługę komunikacji, transmisji danych i sterowania migawką, stanowiąc kluczowy element w systemach wizyjnych i projektach przetwarzania obrazu w czasie rzeczywistym.

Brak towaru

Moduł TerasIC HDMI v1.4 (P0087) umożliwia implementację pełnego toru nadawczo-odbiorczego HDMI w systemach FPGA. Dzięki obsłudze rozdzielczości Full HD, zgodności z HDMI 1.4a oraz dołączonym projektom referencyjnym, stanowi uniwersalne rozwiązanie do testowania, nauki i wdrażania transmisji wideo w aplikacjach embedded i multimedialnych.

Brak towaru

TerasIC TR4-530 (P0109) to zestaw rozwojowy FPGA z układem Stratix IV GX, oferujący wysoką wydajność logiczną, obsługę szybkiej pamięci DDR3 oraz szerokie możliwości rozbudowy przez złącza HSMC i PCIe. Platforma przeznaczona do prototypowania systemów cyfrowych, aplikacji PCI Express i przetwarzania danych w czasie rzeczywistym.

Brak towaru

TerasIC TR4-230 (P0107) oferuje platformę rozwojową opartą na FPGA Stratix IV GX z szerokim zakresem interfejsów oraz wsparciem dla projektów PCI Express i szybkiej pamięci DDR3. Rozwiązanie przeznaczone do budowy systemów komunikacyjnych, prototypowania ASIC oraz aplikacji o wysokim zapotrzebowaniu na zasoby logiczne.

Brak towaru

TerasIC CLR-HSMC (P0079) umożliwia integrację kamer przemysłowych z interfejsem Camera Link z płytami FPGA przez złącze HSMC, wspierając przesył obrazu w trybach base, medium i dual base. Moduł znajduje zastosowanie w systemach wizyjnych, liniach produkcyjnych oraz projektach z przetwarzaniem obrazu w czasie rzeczywistym.

Brak towaru

TerasIC XSFP/SFP+HSMC (P0092) umożliwia budowę systemów Ethernet 10G opartych na interfejsie XAUI z dwoma kanałami SFP+ i zegarem referencyjnym 156,25 MHz. Moduł przeznaczony do integracji z płytami FPGA posiadającymi złącze HSMC, m.in. Stratix IV GX i DE4, znajduje zastosowanie w projektach sieciowych, transmisji danych oraz testach interfejsów wysokiej przepustowości.

Brak towaru

Wyświetlacz LCD alfanumeryczny 2x16 bez podświetlenia przeznaczony do zestawów firmy TerasIC (DE0, DE1, DE2 , DE2 -115). P0075

Platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. Wersja edukacyjna. TerasIC T-Core P0633