3 909,05 zł Netto

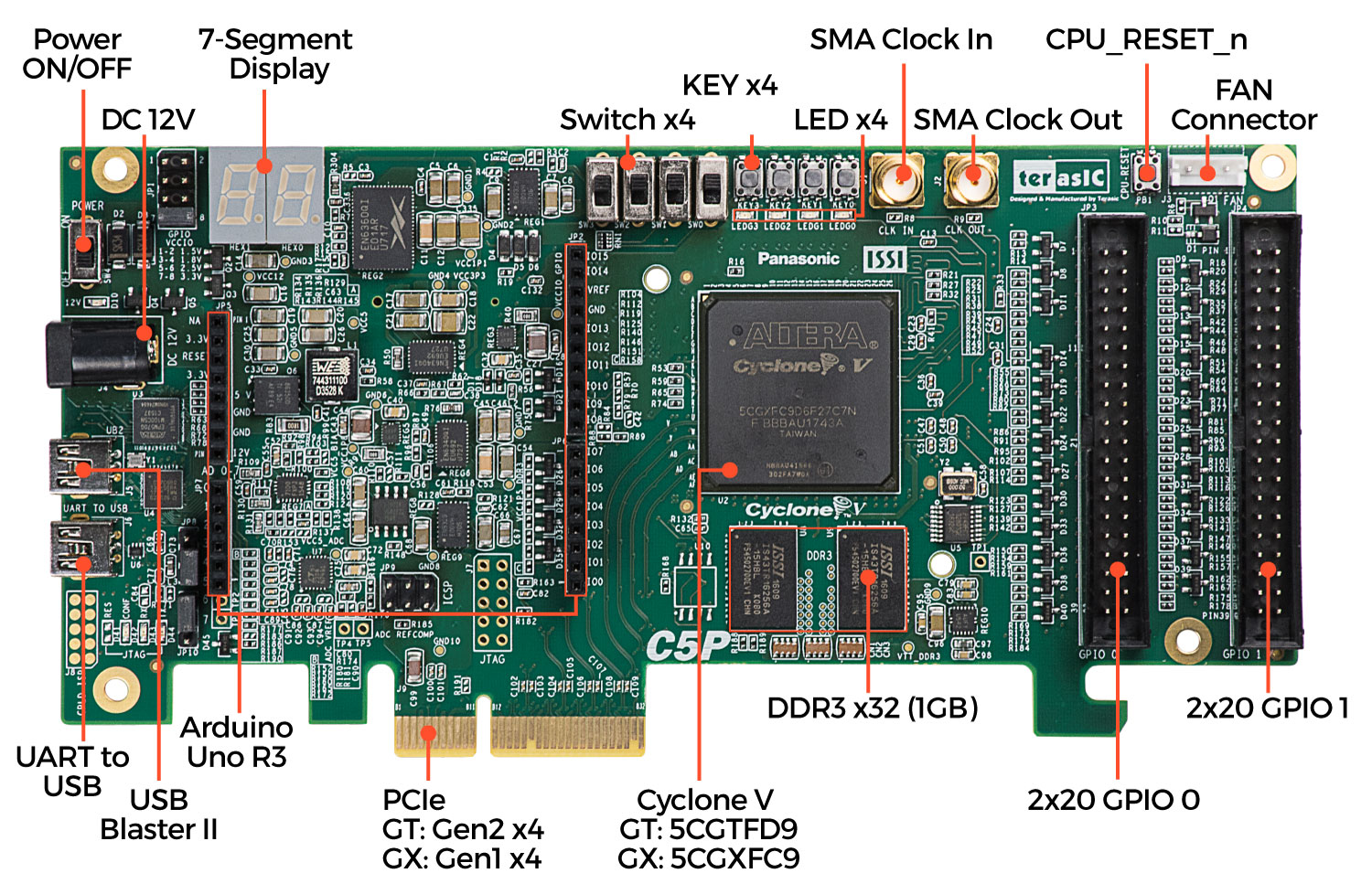

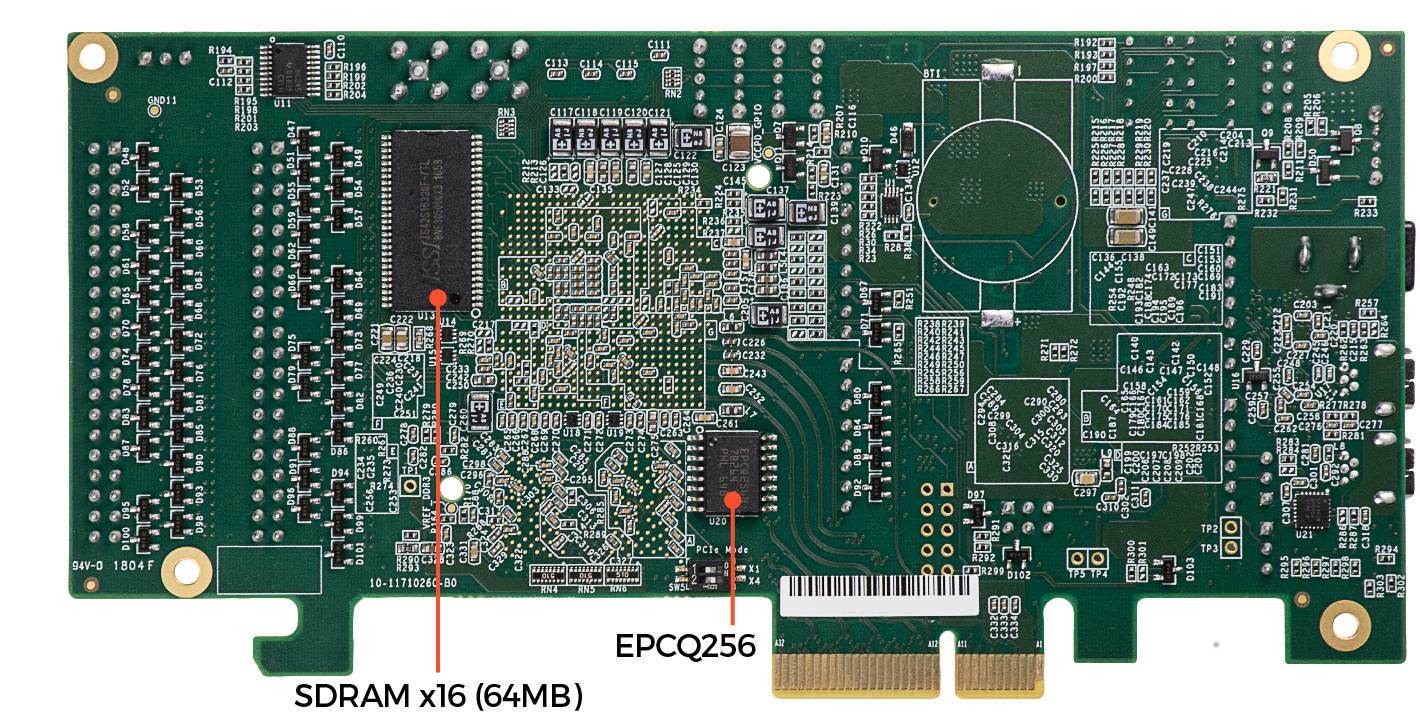

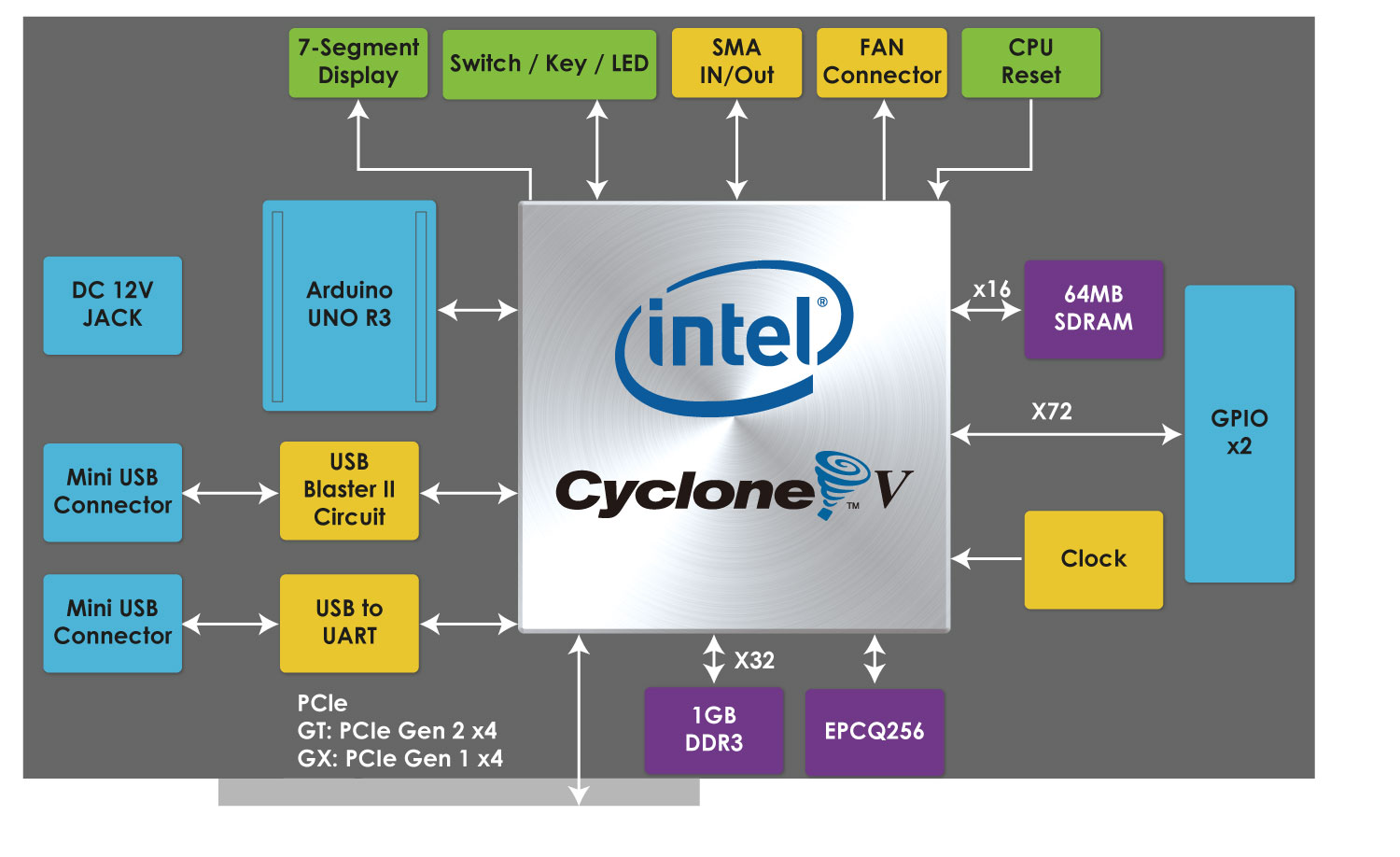

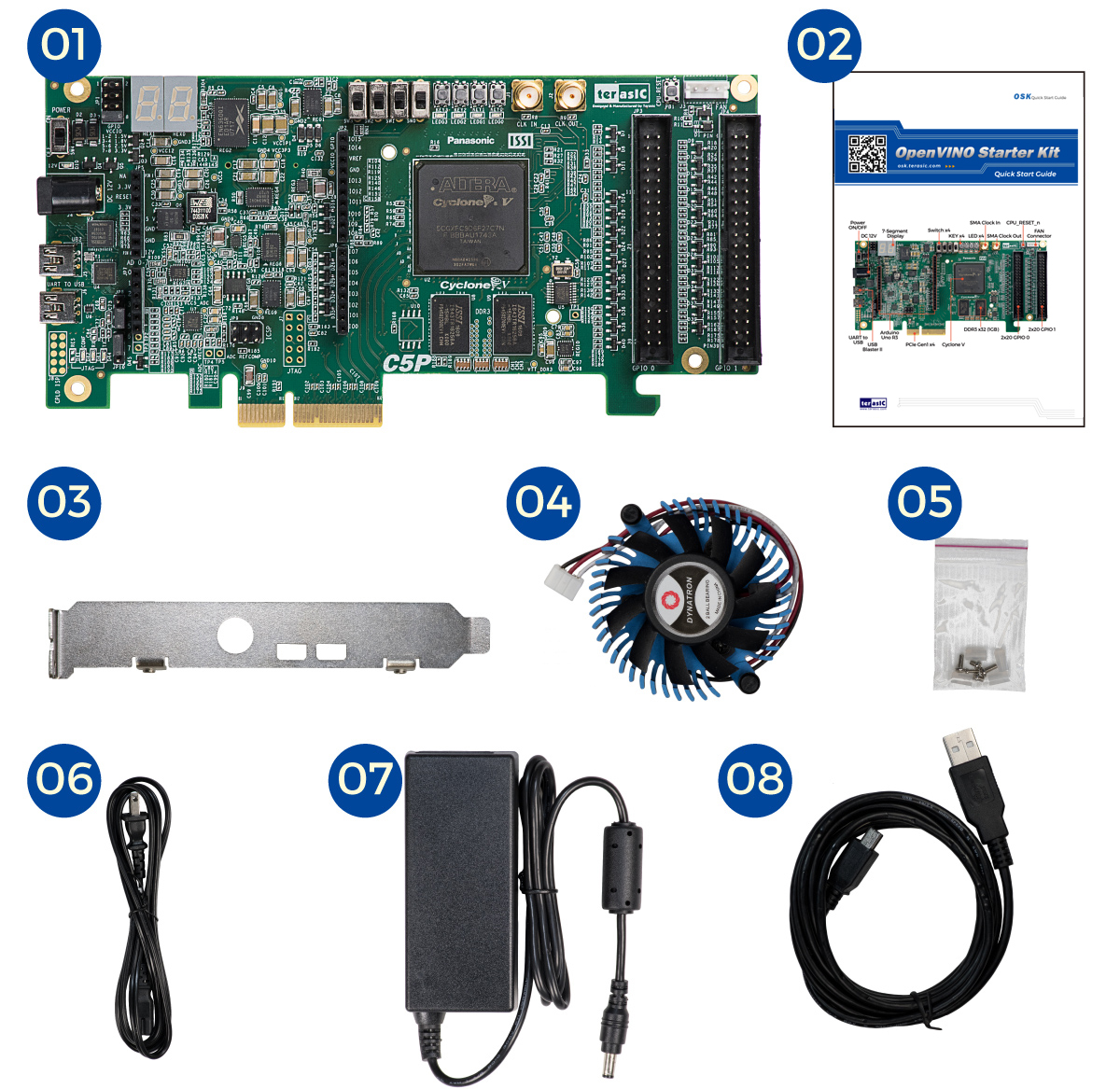

Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE i obsługuje PCIe Gen 2x4. Płytka posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0559

OpenVINO to zestaw startowy FPGA w postaci karty z złączem PCIe o wysokiej wydajności. Jest wyposażony w programowalny układ Cyclone V GT z 301K LE i obsługuje PCIe Gen 2x4. Płytka posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO czy pozwalające podłączyć rozszerzenia Arduino. To sprawia, że zestaw startowy OpenVINO to konfigurowalna platforma łącząca dużą wydajnością obliczeniową i niskie zużycie energii.

Pakiet OpenVINO zawiera projekty referencyjne dla wszystkich urządzeń peryferyjnych zestawu oraz szczegółową instrukcję dla programistów.

Producent BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

TerasIC DE0 to kompletny zestaw ewaluacyjny oparty na FPGA Cyclone III, zaprojektowany do nauki, testowania i wdrażania systemów cyfrowych. Oferuje szeroki zestaw interfejsów i peryferiów umożliwiających tworzenie złożonych projektów zarówno edukacyjnych, jak i przemysłowych.

Brak towaru

VEEK-MT2S to płytka deweloperska oparta na układzie Cyclone V SX SoC Cyclone V SX SoC—5CSXFC6D6F31C6N. W zestawie, oprócz płytki z układem programowalnym FPGA, znajdują się również 7-calowy wyświetlacz TFT dotykowy o rozdzielczości 800 x 480 pikseli, kamera o rozdzielczości 8 Megapikseli (3264 x 2448 pikseli), czujnik światła czujnik IMU 9DOF (akcelerometr, żyroskop, magnetometr). Terasic K0161

Brak towaru

Moduł akceleratora obliczeń oparty na układzie FPGA Intel® Agilex™. Ma gniazdo PCI Express Gen 4.0 x16, dwa złącza 200G QSFP-DD i oferuje 32 GB DDR4. Terasic DE10-Agilex (P0701)

Brak towaru

Płytka rozwojowa Terasic DE25-Nano z układem FPGA Agilex™ 5 i systemem HPS ARM Cortex-A76/A55 stanowi nowoczesną platformę dla aplikacji AI, przetwarzania wizyjnego i systemów wbudowanych. Bogaty zestaw interfejsów oraz pamięci, aktywne chłodzenie i kompaktowe wymiary pozwalają na wykorzystanie zarówno w prototypowaniu, jak i docelowych rozwiązaniach przemysłowych.

Wyświetlacz LCD alfanumeryczny 2x16 bez podświetlenia przeznaczony do zestawów firmy TerasIC (DE0, DE1, DE2 , DE2 -115). P0075

Terasic ADC-SoC to płyta rozwojowa z układem programowalnym FPGA oraz dwukanałowym szybkim przetwornikiem ADC. Płyta bazuje na module Terasic DE0-Nano-SoC. Wbudowany przetwornik ADC wykorzystuje SMA jako interfejs wejściowy, posiada dwa kanały, oferuje rozdzielczość 14-bitową, i szybkość próbkowania do 150 MSPS Megasamples per Second). Terasic (P0435)

Brak towaru

Cyclone V E FPGA Video Development System

Brak towaru

Moduł ewaluacyjny z procesorem Intel Stratix 10 SoC z elementami logicznymi 2800K. Moduł posiada pamięć DDR4 SDRAM (do 64 GB), wbudowany USB-Blaster II, Ethernet, microSD, miniUSB oraz złącza FMC/FMC+ do rozbudowy. TerasIC Apollo S10 SoM Board (P0630)

Brak towaru

Płytka ewaluacyjna z układem Intel Agilex SoC z 1400 tys. elementów logicznych. Moduł ma gniazda z wbudowaną pamięcią DDR4 SO-DIMM o pojemności 32 GB, złącze QSFP28, PCIe Gen 4x16, wbudowany USB-Blaster II oraz złącza FMC/FMC+ do rozbudowy. TerasIC Apollo Agilex SOM (P0795)

Brak towaru

Moduł XTS-FMC jest rozszerzeniem dla układów FPGA pozwalającym na dostęp do kanałów/interfejsów komunikacyjnych poprzez złącze SMA. TerasIC P0401

Brak towaru

Terasic DE10-Lite Board to niskobudżetowa płytka deweloperska z układem FPGA Altera MAX 10. Płyta zawiera szereg komponentów umożliwiających naukę oraz tworzenie prototypów projektów opartych o układy FPGA. Terasic P0466

Brak towaru

Karta HTG-M przeznaczona jest dla zestawów ewaluacyjnych z układami FPGA, które zostały wyposażone w złącze HSMC (High-Speed Mezzanine connector) lub HSTC (High-Speed Terasic Connector). Karta HTG posiada trzy złącza żeńskie (40-pinowe). Pozwala na konwersje wejść/wyjść HSMC do dwóch 40-pinowych złącz prototypowych lub złącza HSTC do trzech 40-pinowych złącz prototypowych. TerasIC P0024

Zestaw rozwojowy z układem SoC FPGA Intel Arria 10. Dedykowany do przemysłowych aplikacji wbudowanych o wysokich wymaganiach wydajności. Terasic P0506

Brak towaru

Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE oraz minikomputer z układem Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). Moduł FPGA posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0650

Brak towaru

Sterownik serwomechanizmów do zestawów FPGA TerasIC serii DE umożliwia sterowanie maksymalnie 24 serwomechanizmami. Dostarcza napięcie 6 V do zasilania serwomechanizmów. W zestawie serwomechanizm MG966R i taśma do połączenia z zestawem FPGA. P0288

Platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. TerasIC T-Core P0633

Brak towaru

Płytka rozwojowa Terasic DE25-Nano z układem FPGA Agilex™ 5 i systemem HPS ARM Cortex-A76/A55 stanowi nowoczesną platformę dla aplikacji AI, przetwarzania wizyjnego i systemów wbudowanych. Bogaty zestaw interfejsów oraz pamięci, aktywne chłodzenie i kompaktowe wymiary pozwalają na wykorzystanie zarówno w prototypowaniu, jak i docelowych rozwiązaniach przemysłowych.

Brak towaru

Zestaw z płytką FPGA Terasic DE10-Nano oraz modułem WiFi. Przeznaczony do projektów wykorzystujących FPGA do pracy w chmurze. TerasIC P0700

Brak towaru

Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE i obsługuje PCIe Gen 2x4. Płytka posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0559