21 487,65 zł Netto

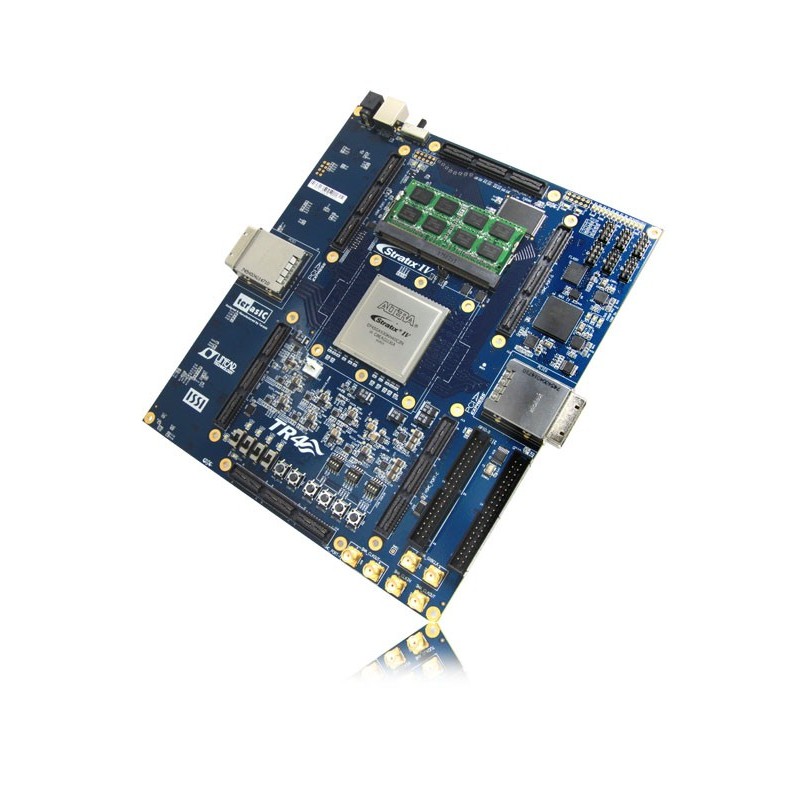

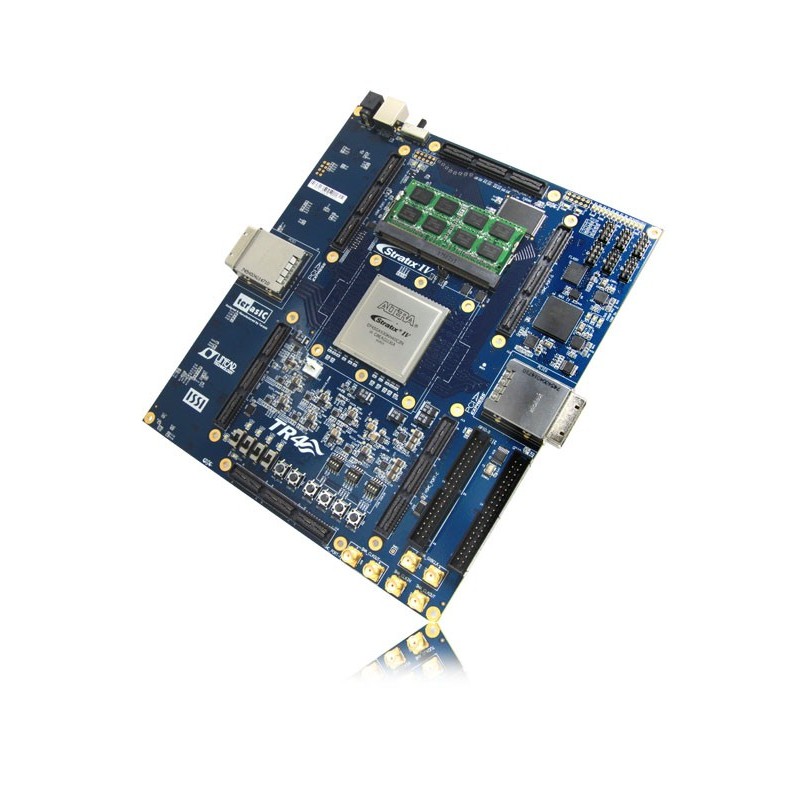

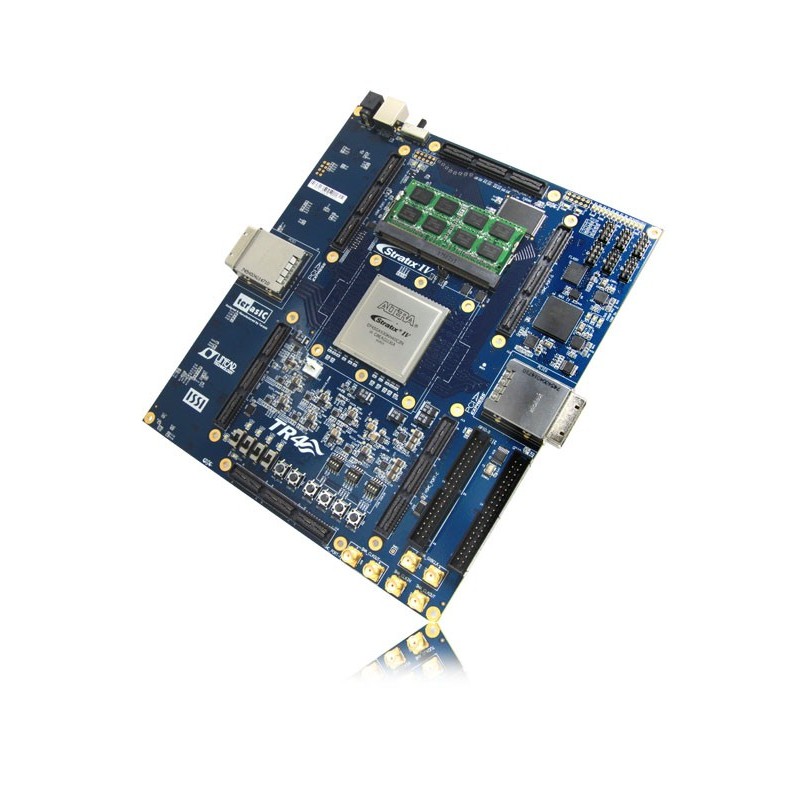

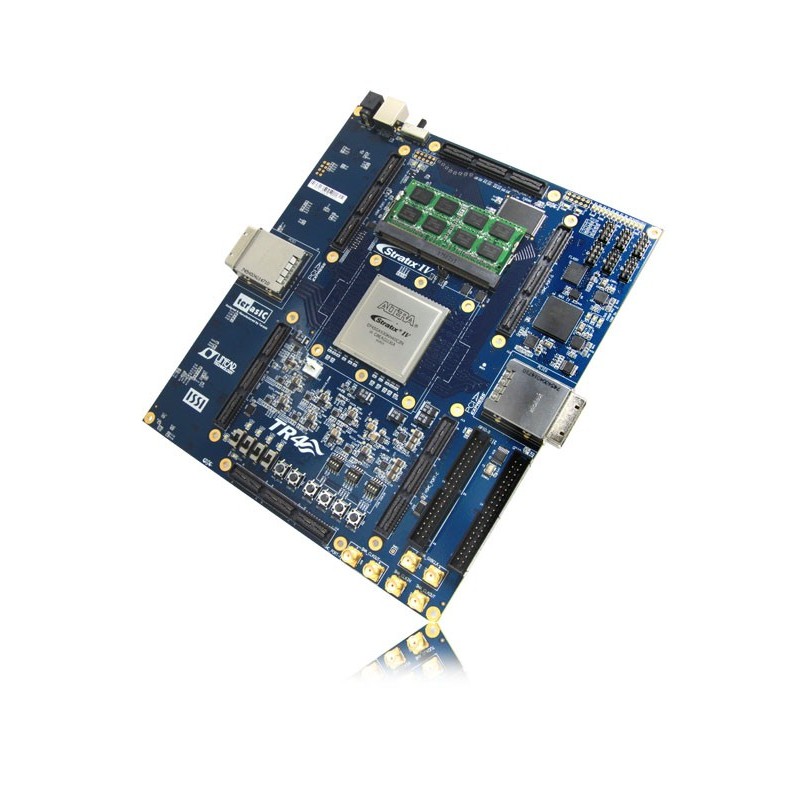

TerasIC TR4-230 (P0107) oferuje platformę rozwojową opartą na FPGA Stratix IV GX z szerokim zakresem interfejsów oraz wsparciem dla projektów PCI Express i szybkiej pamięci DDR3. Rozwiązanie przeznaczone do budowy systemów komunikacyjnych, prototypowania ASIC oraz aplikacji o wysokim zapotrzebowaniu na zasoby logiczne.

Zestaw rozwojowy TR4-230 oferuje zaawansowaną platformę sprzętową przeznaczoną do projektowania systemów cyfrowych wymagających dużej przepustowości, wysokiej wydajności logicznej oraz rozbudowanych interfejsów pamięci. Układ FPGA Stratix IV GX EP4SGX230 dostarcza 228 000 elementów logicznych, 1 288 bloków mnożników 18x18 oraz 17 133 Kbit pamięci wewnętrznej, wspierając projektowanie aplikacji intensywnie wykorzystujących zasoby FPGA.

Płytka wyposażona została w gniazdo SO-DIMM DDR3 z obsługą do 4 GB pamięci przy maksymalnym taktowaniu 533 MHz, co przekłada się na teoretyczną przepustowość do 68 Gb/s. Na pokładzie znajdują się również pamięć Flash 64 MB i pamięć SSRAM 2 MB. Układ MAX II CPLD EPM2210 odpowiada za konfigurację FPGA, a wbudowany programator USB Blaster umożliwia bezpośrednią współpracę z oprogramowaniem Quartus II.

Rozszerzalność systemu zapewniają sześć złączy HSMC, dwa złącza PCIe x4 oraz dwa 40-pinowe złącza rozszerzeń. Obsługa transceiverów do 8,5 Gb/s oraz 52 kanałów LVDS umożliwia tworzenie zaawansowanych systemów komunikacyjnych i wielopłytowych układów FPGA. Całość zasilana jest napięciem 19 V DC, a zastosowane złącza SMA pozwalają na podłączenie zewnętrznych źródeł zegarowych oraz testowanie sygnałów różnicowych.

Producent BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Zestaw rozwojowy z układem SoC FPGA Intel Arria 10. Dedykowany do przemysłowych aplikacji wbudowanych o wysokich wymaganiach wydajności. Terasic P0506

Brak towaru

Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE i obsługuje PCIe Gen 2x4. Płytka posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0559

Brak towaru

[CENA EDUKACYJNA] Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE i obsługuje PCIe Gen 2x4. Płytka posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0559

Brak towaru

Moduł pamięci SODIMM firmy TerasIC o pojemności 18MB i częstotliwości pracy 550MHz. Moduł przeznaczony jest do pracy z układami FPGA Intel Stratix 10 w zestawach ewaluacyjnych takich jak TerasIC DE10-Pro-GX-280-4G oraz TerasIC DE10-Pro-GX-280-8G. TerasIC S0534

Brak towaru

Moduł SoM z układem SoC łączącym FPGA z rdzeniem ARM Cortex-A9. Płytka wyposażona jest w złacze DDR4 Eadge (z zasialniem 3,3 V). Terasic P0553

Brak towaru

MAX 10 Plus jest zestawem deweloperskim opartym o układ FPGA od Intela, wyposażony w 50 000 programowalnych elementów logicznych. Digilent P0638

Brak towaru

Moduł XTS-FMC jest rozszerzeniem dla układów FPGA pozwalającym na dostęp do kanałów/interfejsów komunikacyjnych poprzez złącze SMA. TerasIC P0401

Brak towaru

[CENA EDUKACYJNA] Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE oraz minikomputer z układem Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). Moduł FPGA posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0650

Brak towaru

Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE oraz minikomputer z układem Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). Moduł FPGA posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0650

Brak towaru

Platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. TerasIC T-Core P0633

Brak towaru

Platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. Wersja edukacyjna. TerasIC T-Core P0633

Brak towaru

Kompaktowy zestaw FPGA z układem Intel Arria 10 GX wyposażony w 8 GB pamięci DDR4-2133 oraz złącze komunikacyjne Thunderbolt 3. Może być zastosowany bezpośrednio na laptopach lub innych urządzeniach przenośnych. Terasic FLIK P0642

Brak towaru

Kompaktowy zestaw FPGA z układem Intel Arria 10 GX wyposażony w 8 GB pamięci DDR4-2133 oraz złącze komunikacyjne Thunderbolt 3. Może być zastosowany bezpośrednio na laptopach lub innych urządzeniach przenośnych. Wersja edukacyjna. Terasic FLIK P0642

Brak towaru

Moduł ewaluacyjny z procesorem Intel Stratix 10 SoC z elementami logicznymi 2800K. Moduł posiada pamięć DDR4 SDRAM (do 64 GB), wbudowany USB-Blaster II, Ethernet, microSD, miniUSB oraz złącza FMC/FMC+ do rozbudowy. TerasIC Apollo S10 SoM Board (P0630)

Brak towaru

Zestaw deweloperski z modułem Apollo S10 oraz płytą bazową. Wyposażony w procesor Intel Stratix 10 SoC z elementami logicznymi 2800K, posiada pamięć DDR4 SDRAM (do 64 GB), wbudowany USB-Blaster II, Ethernet, microSD, miniUSB oraz złącza QSFP i USB typ C. TerasIC Apollo Developer Kit (P0671)

Brak towaru

Zestaw startowy FPGA z układem Intel Stratix 10 SX. Moduł posiada zintegrowane urządzenia nadawczo-odbiorcze, które przesyłają dane z prędkością do 28,3 Gb/s, dzięki czemu DE10-Pro jest w pełni zgodny z wersją 3.0 standardu PCI Express. DE10-Pro oferuje szybką pamięć równoległą Flash i cztery pamięci SO-DIMM, które mają 4 GB DDR4 SDRAM. Terasic P0627

Brak towaru

TerasIC TR4-230 (P0107) oferuje platformę rozwojową opartą na FPGA Stratix IV GX z szerokim zakresem interfejsów oraz wsparciem dla projektów PCI Express i szybkiej pamięci DDR3. Rozwiązanie przeznaczone do budowy systemów komunikacyjnych, prototypowania ASIC oraz aplikacji o wysokim zapotrzebowaniu na zasoby logiczne.