546,98 zł Netto

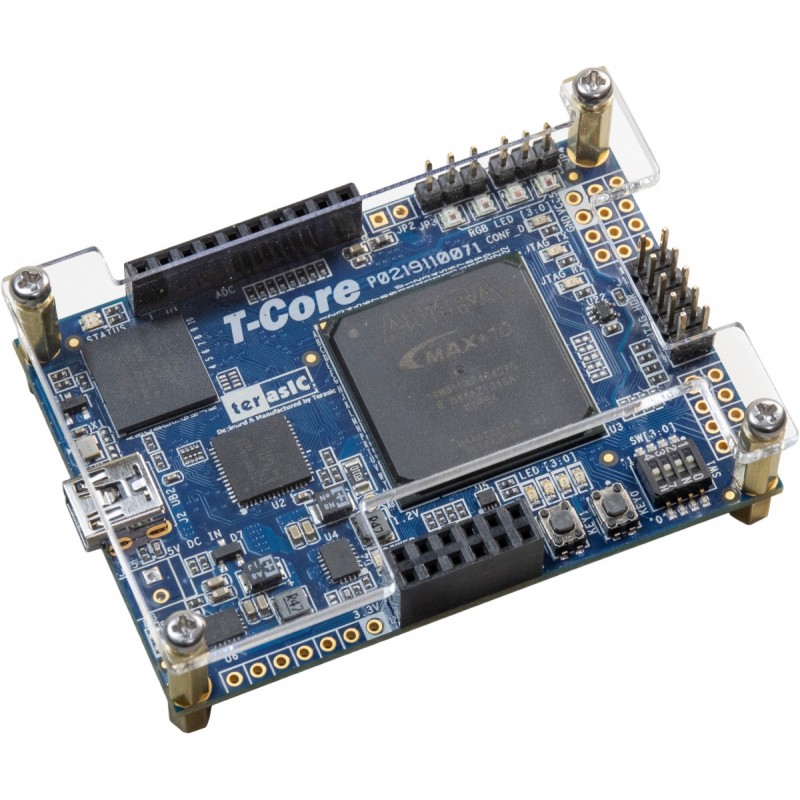

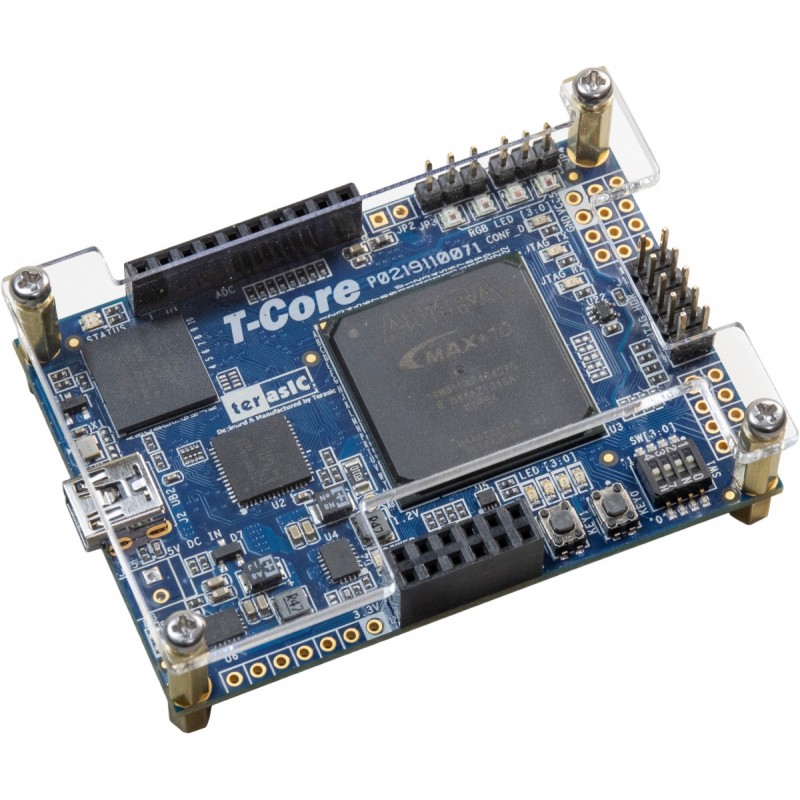

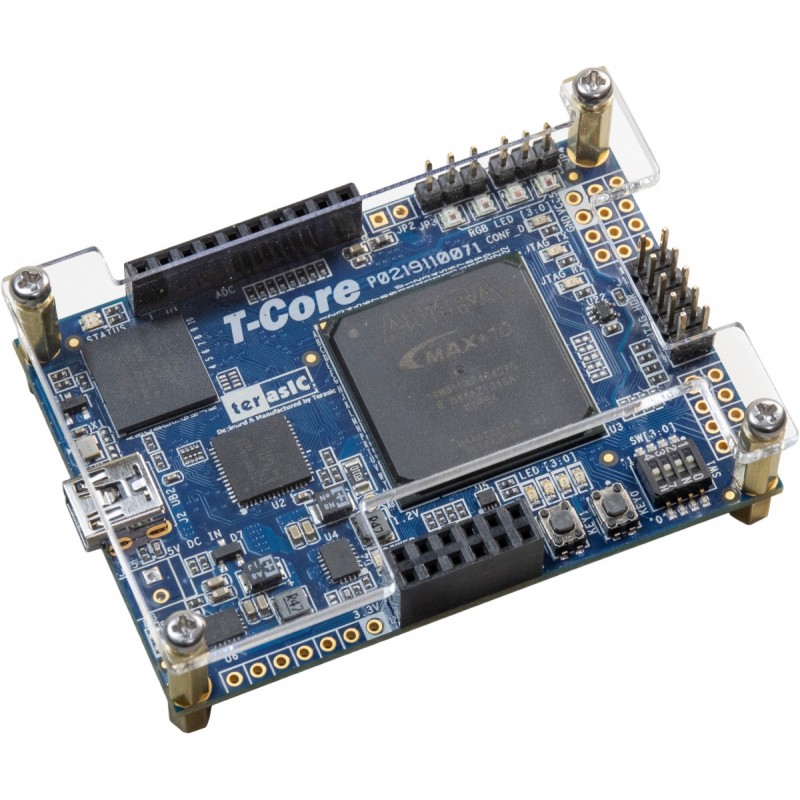

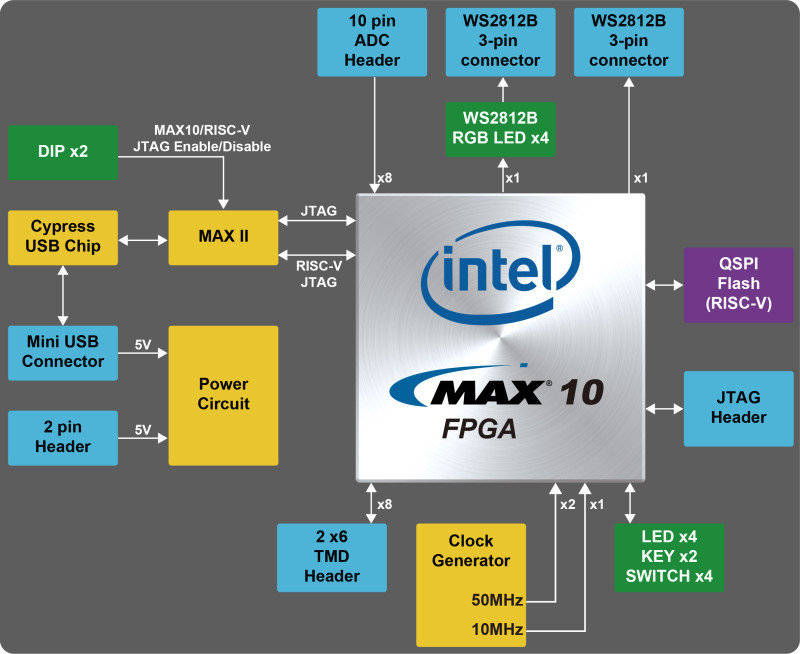

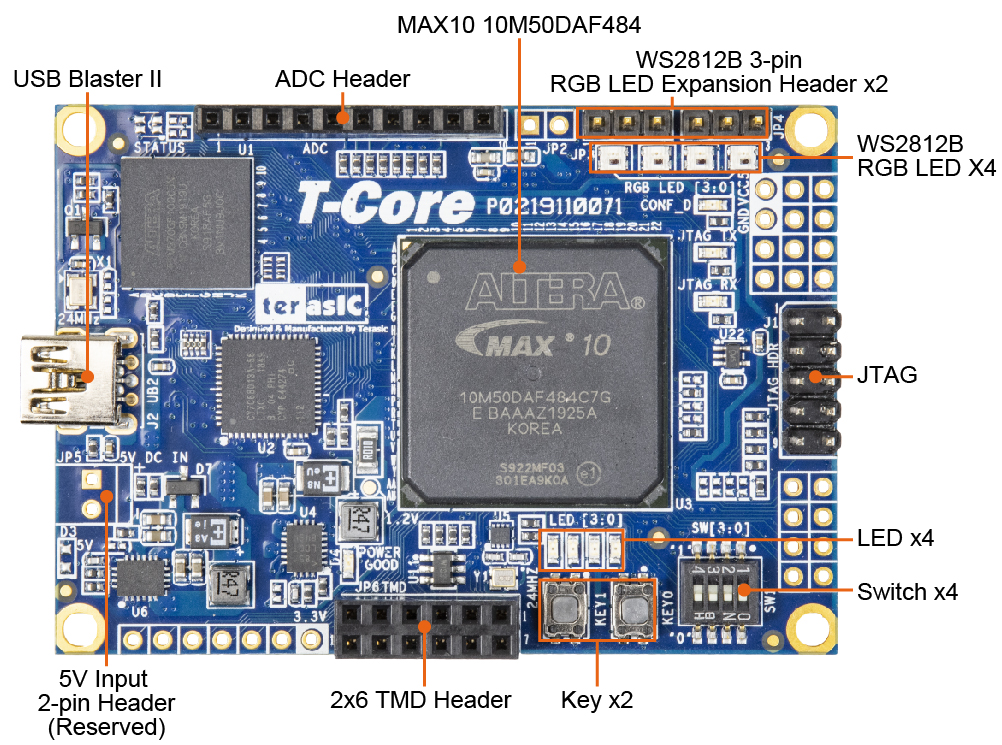

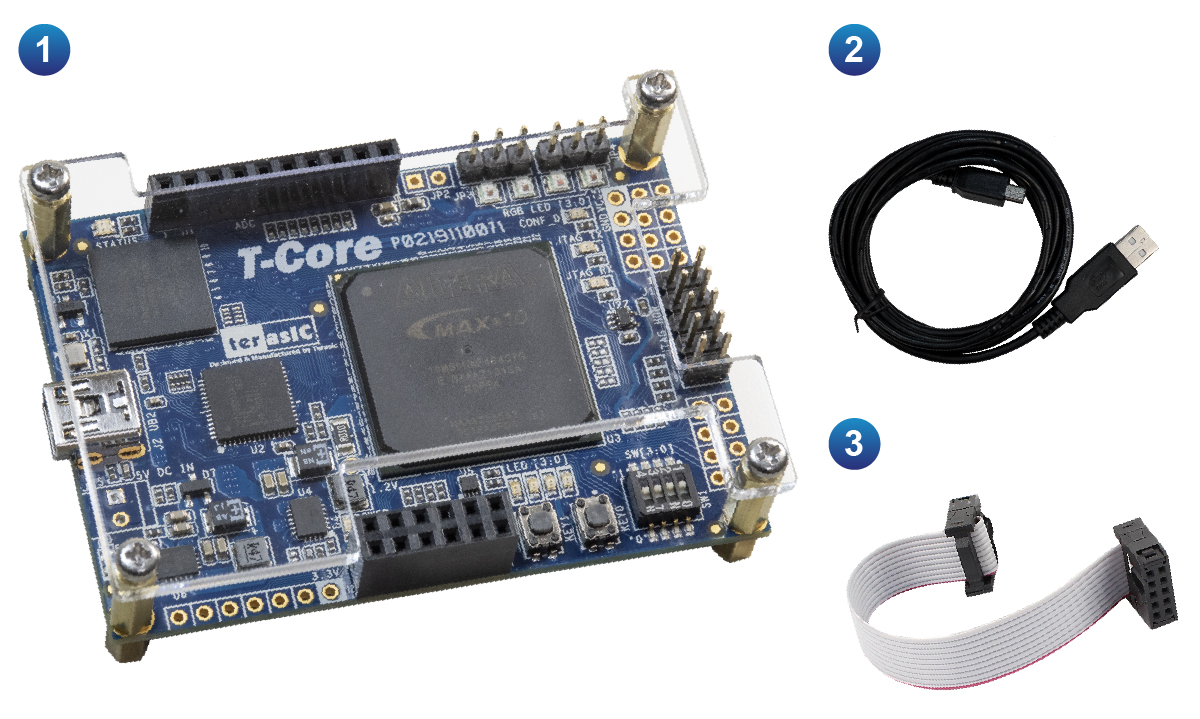

Platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. Wersja edukacyjna. TerasIC T-Core P0633

Oferta przeznaczona wyłącznie dla odbiorców akademickich (studentów i wykładowców wyższych uczelni)!

Składając zamówienie należy podać:

- imię i nazwisko użytkownika

- stanowisko

- adres e-mail użytkownika (adres e-mail musi być z domeny uczelni)

- pełną nazwę uczelni

- nazwę wydziału/instytutu/zakładu dydaktycznego

- adres uczelni

- stronę internetową uczelni

- telefon

- zastosowanie produktu

TerasIC T-Core to platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka rozwojowa T-Core zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. T-Core jest zatem idealnym rozwiązaniem do prototypowania możliwości Intel MAX 10 FPGA.

MAX 10 FPGA pozwala na uzyskanie niższego zużycia energii i wyższą wydajności niż poprzednia generacja. T-Core obsługuje również procesor RISC-V z wbudowanym debugowaniem JTAG. Jest to idealna platforma do nauki projektowania procesorów RISC-V lub projektowania systemów wbudowanych.

Nie jesteś powiązany z żadną uczelnią, lub jesteś klientem biznesowym? Sprawdź:

TerasIC T-Core - zestaw rozwojowy z układem FPGA Intel MAX 10

Producent BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

Osoba odpowiedzialna BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Polska sprzedaz@kamami.pl 22 767 36 20

[CENA EDUKACYJNA] Zestaw startowy/ewaluacyjny Terasic DE0-Nano Board dla układów FPGA Cyclone IV firmy Altera. Jeden z najmniejszych i najprostszych zestawów startowych dla układów FPGA, wyposażony w podstawowe peryferia, w tym programator-konfigurator JTAG.Obniżona cena (w stosunku do klasycznej wersji Terasic DE0-Nano) dotyczy wyłącznie szkół, uczelni, wykładowców, uczniów i studentów. P0082

TerasIC TR4-530 (P0109) to zestaw rozwojowy FPGA z układem Stratix IV GX, oferujący wysoką wydajność logiczną, obsługę szybkiej pamięci DDR3 oraz szerokie możliwości rozbudowy przez złącza HSMC i PCIe. Platforma przeznaczona do prototypowania systemów cyfrowych, aplikacji PCI Express i przetwarzania danych w czasie rzeczywistym.

Brak towaru

MAX 10 Plus jest zestawem deweloperskim opartym o układ FPGA od Intela, wyposażony w 50 000 programowalnych elementów logicznych. Digilent P0638

Brak towaru

Platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. TerasIC T-Core P0633

Brak towaru

Zestaw startowy DE10-Nano Kit z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. Terasic P0496

TerasIC INK to kompleksowa platforma sprzętowa do tworzenia i testowania aplikacji przemysłowych opartych na FPGA, oferująca pełną obsługę komunikacji szeregowej i Ethernetu przemysłowego. Zestaw pozwala na szybki rozwój rozwiązań automatyki i transmisji danych w środowiskach wymagających wysokiej niezawodności.

Brak towaru

Moduł pamięci SODIMM firmy TerasIC o pojemności 18MB i częstotliwości pracy 550MHz. Moduł przeznaczony jest do pracy z układami FPGA Intel Stratix 10 w zestawach ewaluacyjnych takich jak TerasIC DE10-Pro-GX-280-4G oraz TerasIC DE10-Pro-GX-280-8G. TerasIC S0534

Brak towaru

[CENA EDUKACYJNA] Zestaw ewaluacyjny Terasic DE0 Board dla układów FPGA Cyclone III firmy Altera. Wyposażono go we wszystkie podstawowe peryferia umożliwiające prowadzenie prac badawczych i ewaluacyjnych z układami FPGA, w tym programator-konfigurator JTAG. Obniżona cena (w stosunku do klasycznej wersji Terasic DE0) dotyczy wyłącznie szkół, uczelni, wykładowców, uczniów i studentów.

DE1-SoC + 5 points multitouch display MTL2

TerasIC TR4-530 (P0109) to zestaw rozwojowy FPGA z układem Stratix IV GX, oferujący wysoką wydajność logiczną, obsługę szybkiej pamięci DDR3 oraz szerokie możliwości rozbudowy przez złącza HSMC i PCIe. Platforma przeznaczona do prototypowania systemów cyfrowych, aplikacji PCI Express i przetwarzania danych w czasie rzeczywistym.

Brak towaru

Karta TerasIC AHA-HSMC umożliwia integrację sensorów obrazu Aptina z zestawami FPGA firmy TerasIC wyposażonymi w interfejs HSMC. Zapewnia pełną obsługę komunikacji, transmisji danych i sterowania migawką, stanowiąc kluczowy element w systemach wizyjnych i projektach przetwarzania obrazu w czasie rzeczywistym.

Brak towaru

TerasIC DE0 to kompletny zestaw ewaluacyjny oparty na FPGA Cyclone III, zaprojektowany do nauki, testowania i wdrażania systemów cyfrowych. Oferuje szeroki zestaw interfejsów i peryferiów umożliwiających tworzenie złożonych projektów zarówno edukacyjnych, jak i przemysłowych.

Brak towaru

Zestaw rozwojowy z układem SoC FPGA Intel Arria 10. Dedykowany do przemysłowych aplikacji wbudowanych o wysokich wymaganiach wydajności. Terasic P0506

Brak towaru

Sterownik serwomechanizmów do zestawów FPGA TerasIC serii DE umożliwia sterowanie maksymalnie 24 serwomechanizmami. Dostarcza napięcie 6 V do zasilania serwomechanizmów. W zestawie serwomechanizm MG966R i taśma do połączenia z zestawem FPGA. P0288

Brak towaru

TerasIC CLR-HSMC (P0079) umożliwia integrację kamer przemysłowych z interfejsem Camera Link z płytami FPGA przez złącze HSMC, wspierając przesył obrazu w trybach base, medium i dual base. Moduł znajduje zastosowanie w systemach wizyjnych, liniach produkcyjnych oraz projektach z przetwarzaniem obrazu w czasie rzeczywistym.

Brak towaru

A-Cute Car Robotic Kit to kompletne 3-kołowe podwozie robota mobilnego wraz ze sterownikiem opartym o układ FPGA do samodzielnego programowania. P0467

Brak towaru

Adapter przeznaczony do łączenia płytek ze złączem PCIe z komputerem. Może obsługiwać interfejs PCIe Gen3 x4. Terasic P0492

Płytka rozwojowa z układem FPGA Aria 10 GX to idealne rozwiązanie dla projektów wymagajacych dużej pojemności pamięci, szybkiej transmisji danych oraz efektywnego zarzadzania mocą. Terasic P0489

Brak towaru

Platforma rozwojowa oparta na układzie Intel MAX 10 FPGA. Układ dostarcza użytkownikowi 50 000 elementów logicznych oraz 1638 kbit pamięci M9K i 5888 kbit Flash. Płytka zawiera elementy takie jak wbudowany USB-Blaster II, QSPI Flash, złącze ADC, WS2812B RGB LED i złącze 2x6 TMD. Wersja edukacyjna. TerasIC T-Core P0633