zł2,642.92 tax excl.

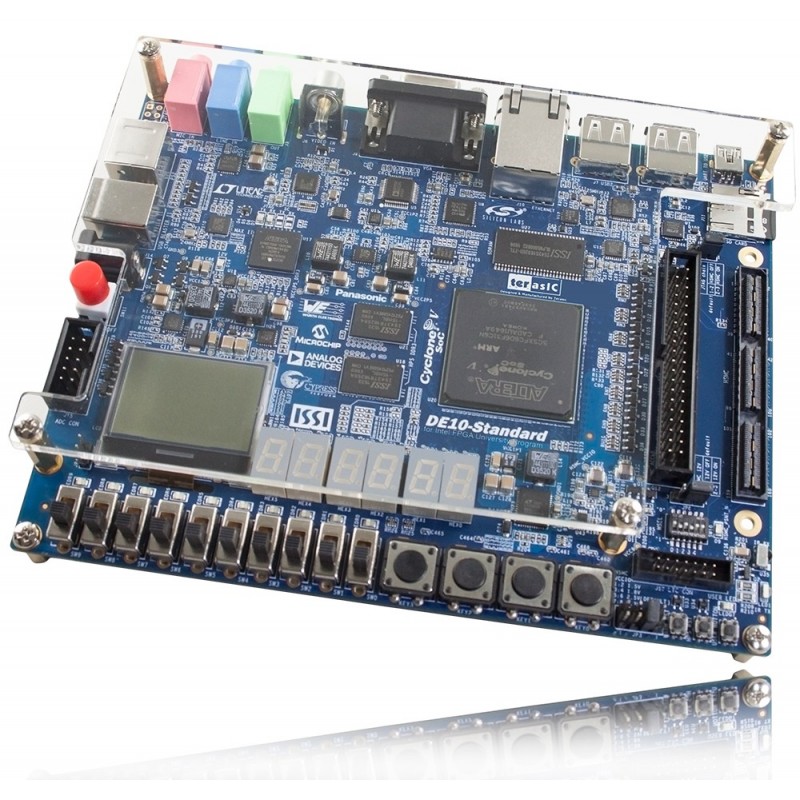

The DE10-Standard Development Kit presents a robust hardware design platform built around the Intel System-on-Chip (SoC) FPGA, which combines the latest dual-core Cortex-A9 embedded cores with industry-leading programmable logic for ultimate design flexibility. P0493

free shipping in Poland for all orders over 500 PLN

If your payment will be credited to our account by 11:00

Each consumer can return the purchased goods within 14 days

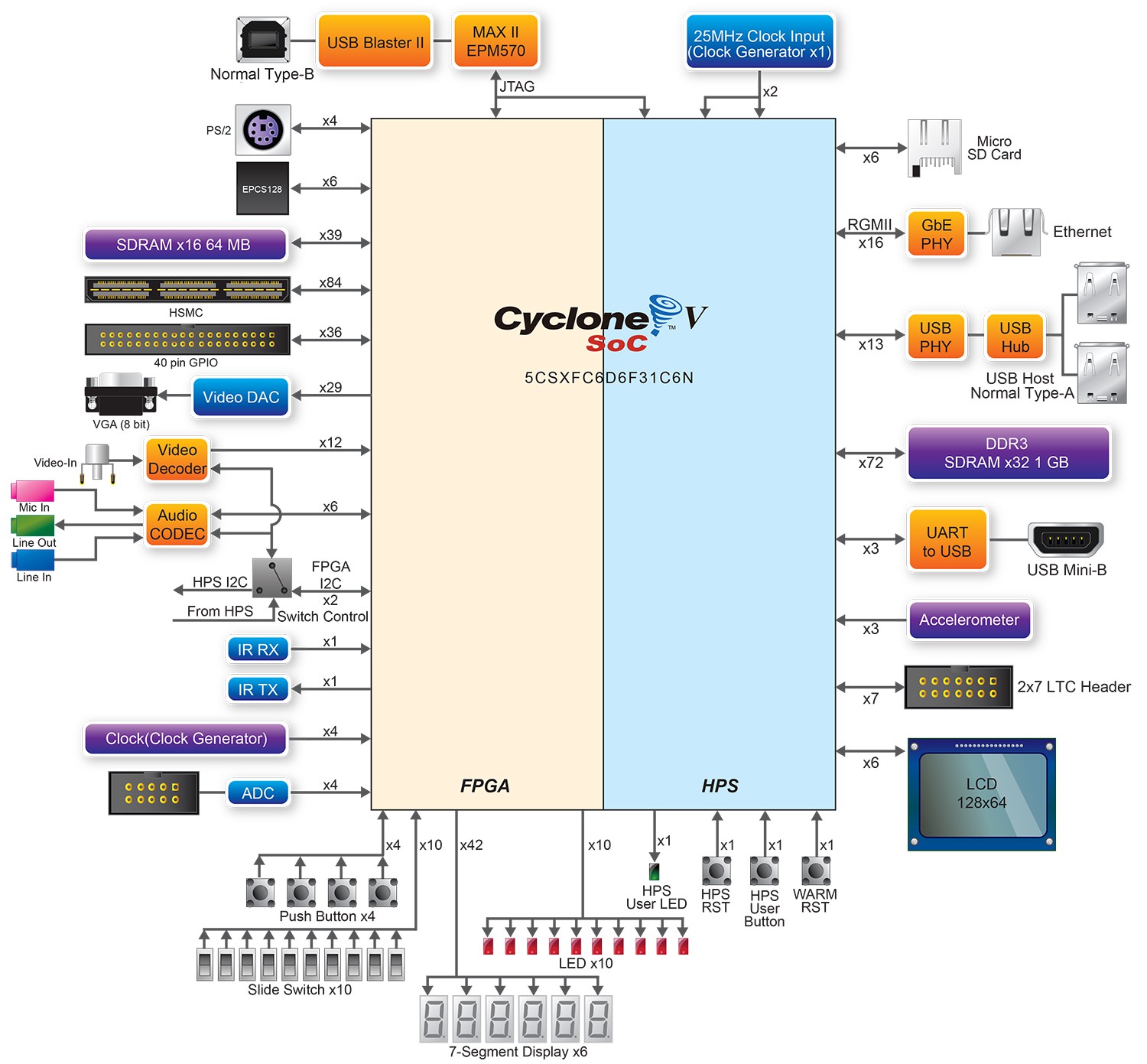

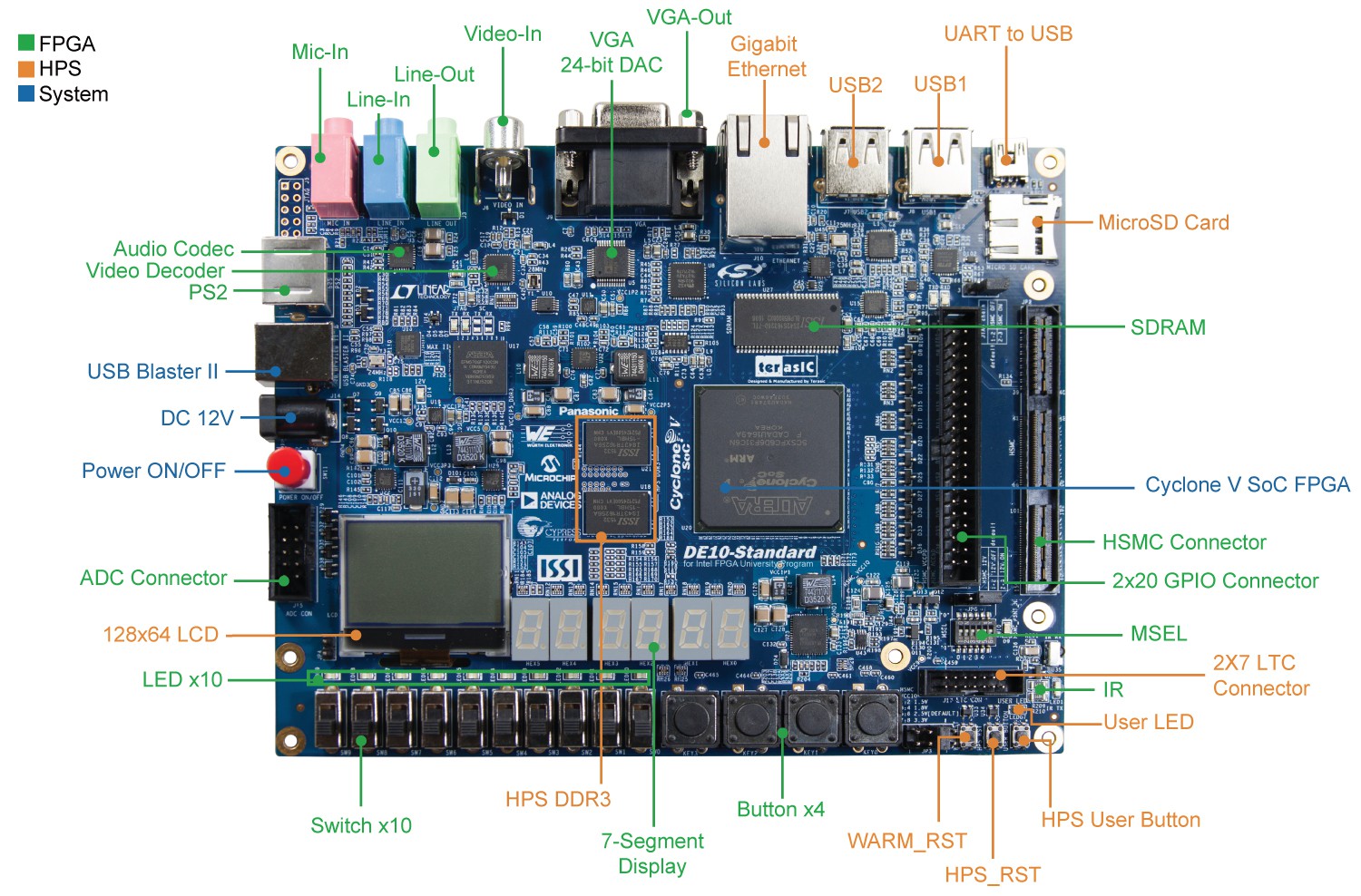

The DE10-Standard Development Kit presents a robust hardware design platform built around the Intel System-on-Chip (SoC) FPGA, which combines the latest dual-core Cortex-A9 embedded cores with industry-leading programmable logic for ultimate design flexibility. Users can now leverage the power of tremendous re-configurability paired with a high-performance, low-power processor system. Altera’s SoC integrates an ARM-based hard processor system (HPS) consisting of processor, peripherals and memory interfaces tied seamlessly with the FPGA fabric using a high-bandwidth interconnect backbone. The DE10-Standard development board includes hardware such as high-speed DDR3 memory, video and audio capabilities, Ethernet networking, and much more.

Block Diagram of the DE10-Standard Board

Layout (Size:166*130 mm)

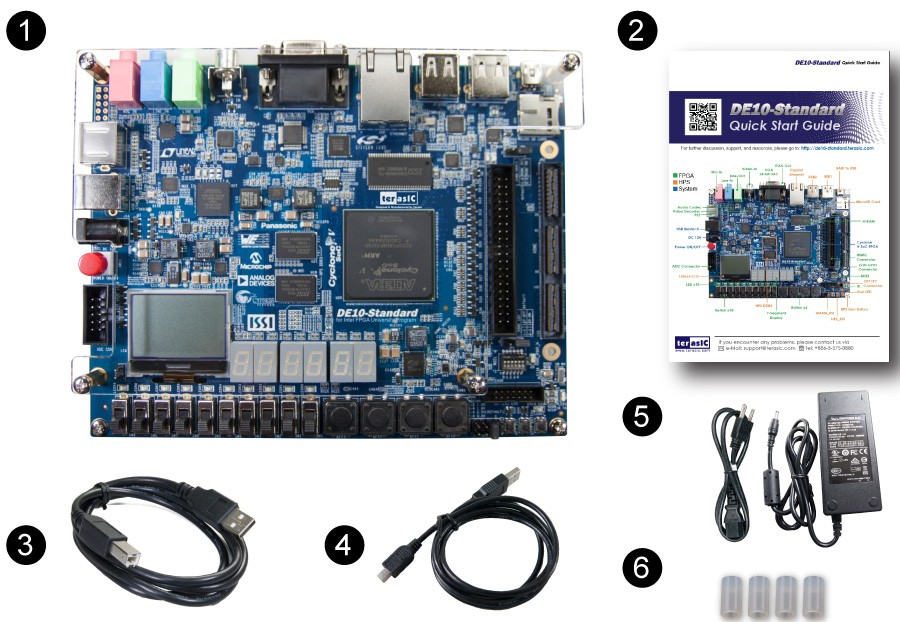

Kit contents:

1. DE10-Standard Board

1. DE10-Standard Board

2. DE10-Standard Quick Start Guide

3. Type A to B USB Cable

4. Type A to Mini-B USB Cable

5. Power DC Adapter (12V)

6. Four Silicon Footstands

Terasic DE10-Lite is a cost-effective Altera MAX 10 based FPGA board. Kit contains lots of reference designs and software utilities for users to easily develop their applications based on these design resources

Gigabit Ethernet transceiver with an FMC interface. Up to 1 Gbps network transfers with the host board using an FMC connector. NET-FMC can be connected any FMC(HPC) interfaces. Terasic P0481

No product available!

Programmable Logic IC Development Tools Cyclone V SE 5CSEMA4U23C6N + 800MHz Dual-core ARM Cortex-A9 processor. Terasic P0496

Development kit with Apollo S10 module and base board. Equipped with an Intel Stratix 10 SoC processor with 2800K logic elements, has a DDR4 SDRAM memory (up to 64 GB), built-in USB-Blaster II, Ethernet, microSD, miniUSB and QSFP connectors and USB type C. TerasIC Apollo Developer Kit (P0671)

No product available!

Computation accelerator module based on Intel® Agilex ™ FPGA. It has a PCI Express Gen 4.0 x16 slot, two 200G QSFP-DD connectors, and offers 32GB DDR4. Terasic DE10-Agilex (P0701)

No product available!

VEEK-MT2S is a development board based on the Cyclone V SX SoC Cyclone V SX SoC-5CSXFC6D6F31C6N chip. Included in addition to the board with programmable FPGA, there are also a 7-inch TFT touchscreen with a resolution of 800 x 480 pixels, 8 megapixel camera (3264 x 2448 pixels), light sensor IMU 9DOF sensor (accelerometer, gyroscope, magnetometer) . Terasic K0161

No product available!

Terasic HDMI-FMC is a HDMI transmitter/receiver daughter board with FMC (FPGA Mezzanine card) interface

[EDUCATIONAL PRICE] FPGA starter kit equipped with Cyclone V GT with 301K LE and minicomputer with Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). The FPGA module has 1 GB DDR3 memory, 64 MB SDRAM memory, UART-USB interface and extensions such as GPIO and Arduino. Terasic P0650

No product available!

The adapter is designed to connect boards with a PCIe connector to a computer. Can support PCIe Gen3 x4 interface. Terasic P0492

The A-Cute Car is an FPGA-based three-wheeled robotic car kit. This car can provide higher operation performance than the MCU based robotic car, because the FPGA provides more powerful computing power than the MCU. P0467

No product available!

FPGA starter kit with Intel Stratix 10 SX chip. The module has integrated transceivers that transmit data at speeds up to 28.3 Gb/s, making DE10-Pro fully compatible with version 3.0 of the PCI Express standard. The DE10-Pro offers fast parallel Flash memory and four SO-DIMMs that have 4 GB DDR4 SDRAM. Terasic P0627

No product available!

Integrated single board computer with Cyclone V SoC core. SoC SoM includes DDR3 memory, Flash memory, energy management system, common interface controllers and disc software (BSP). Terasic P0581

No product available!

No product available!

No product available!

No product available!

VEEK-MT2S is a development board based on the Cyclone V SX SoC Cyclone V SX SoC-5CSXFC6D6F31C6N chip. Included in addition to the board with programmable FPGA, there are also a 7-inch TFT touchscreen with a resolution of 800 x 480 pixels, 8 megapixel camera (3264 x 2448 pixels), light sensor IMU 9DOF sensor (accelerometer, gyroscope, magnetometer) . Terasic K0161

No product available!

[EDUCATIONAL PRICE] FPGA starter kit equipped with Cyclone V GT with 301K LE and supports PCIe Gen 2x4. The board has 1 GB DDR3 memory, 64 MB SDRAM memory, UART-USB interface and extensions such as GPIO and Arduino. Terasic P0559

No product available!

The DE10-Standard Development Kit presents a robust hardware design platform built around the Intel System-on-Chip (SoC) FPGA, which combines the latest dual-core Cortex-A9 embedded cores with industry-leading programmable logic for ultimate design flexibility. P0493