zł2,642.92 tax excl.

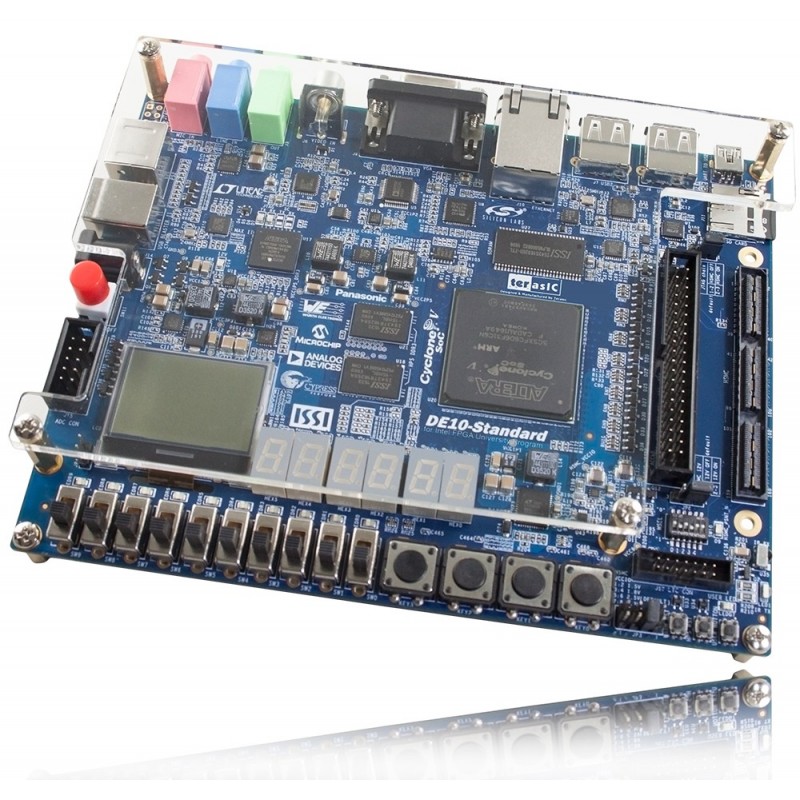

The DE10-Standard Development Kit presents a robust hardware design platform built around the Intel System-on-Chip (SoC) FPGA, which combines the latest dual-core Cortex-A9 embedded cores with industry-leading programmable logic for ultimate design flexibility. P0493

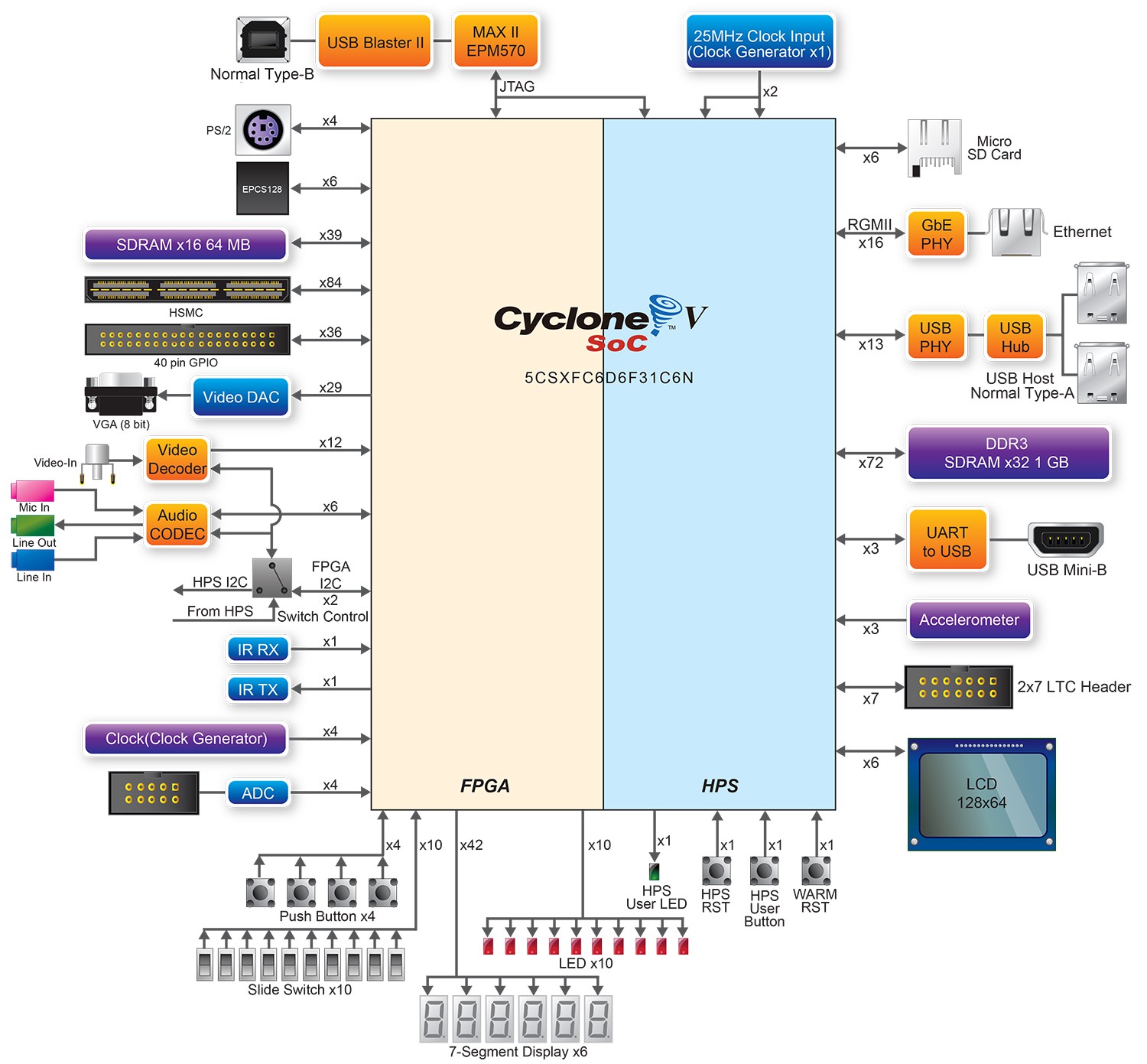

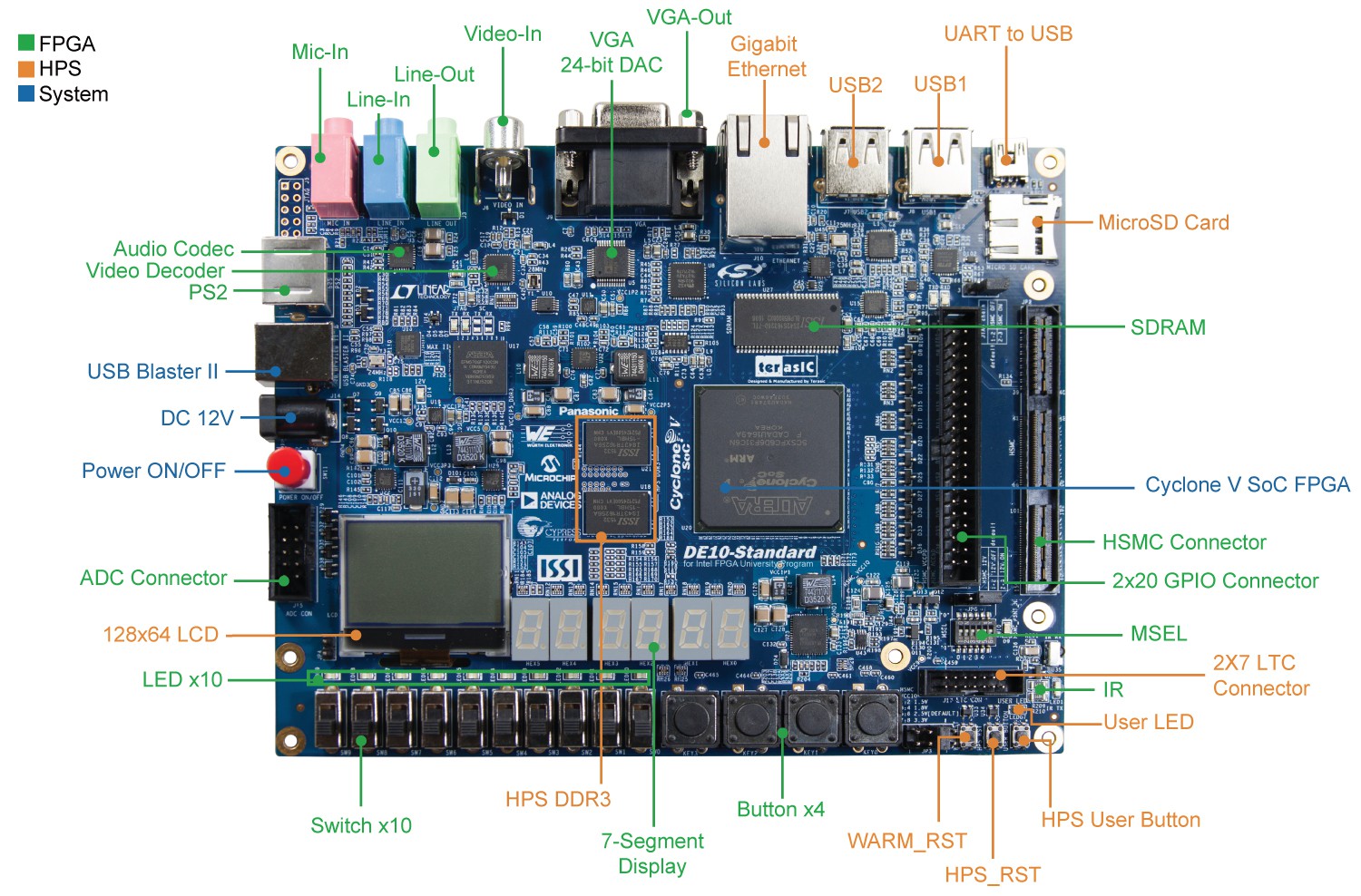

The DE10-Standard Development Kit presents a robust hardware design platform built around the Intel System-on-Chip (SoC) FPGA, which combines the latest dual-core Cortex-A9 embedded cores with industry-leading programmable logic for ultimate design flexibility. Users can now leverage the power of tremendous re-configurability paired with a high-performance, low-power processor system. Altera’s SoC integrates an ARM-based hard processor system (HPS) consisting of processor, peripherals and memory interfaces tied seamlessly with the FPGA fabric using a high-bandwidth interconnect backbone. The DE10-Standard development board includes hardware such as high-speed DDR3 memory, video and audio capabilities, Ethernet networking, and much more.

Block Diagram of the DE10-Standard Board

Layout (Size:166*130 mm)

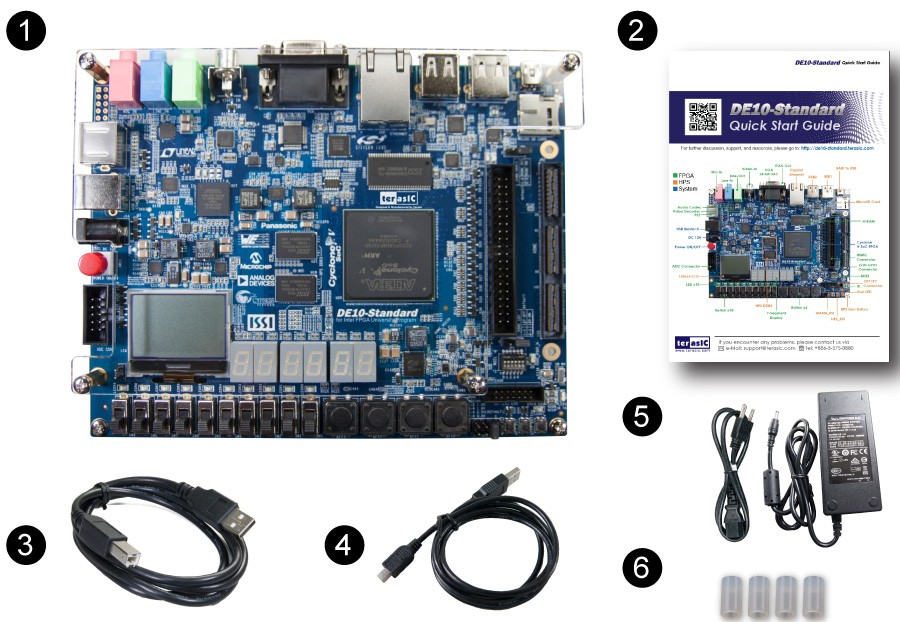

Kit contents:

1. DE10-Standard Board

1. DE10-Standard Board

2. DE10-Standard Quick Start Guide

3. Type A to B USB Cable

4. Type A to Mini-B USB Cable

5. Power DC Adapter (12V)

6. Four Silicon Footstands

Manufacturer BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Poland sprzedaz@kamami.pl 22 767 36 20

Responsible person BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Poland sprzedaz@kamami.pl 22 767 36 20

Terasic DE10-Lite is a cost-effective Altera MAX 10 based FPGA board. Kit contains lots of reference designs and software utilities for users to easily develop their applications based on these design resources

Gigabit Ethernet transceiver with an FMC interface. Up to 1 Gbps network transfers with the host board using an FMC connector. NET-FMC can be connected any FMC(HPC) interfaces. Terasic P0481

No product available!

Programmable Logic IC Development Tools Cyclone V SE 5CSEMA4U23C6N + 800MHz Dual-core ARM Cortex-A9 processor. Terasic P0496

No product available!

Terasic Spider is a six-legged robot rolling with 18 servos controlled by the Altera DE0-Nano-SoC board connecting the FPGA chip and the ARM Cortex-A9 processor. The set contains a complex robot and numerous accessories. P0425

The A-Cute Car is an FPGA-based three-wheeled robotic car kit. This car can provide higher operation performance than the MCU based robotic car, because the FPGA provides more powerful computing power than the MCU. P0467

No product available!

Terasic DE10-Lite is a cost-effective Altera MAX 10 based FPGA board. Kit contains lots of reference designs and software utilities for users to easily develop their applications based on these design resources

Terasic DE10-Lite Board is a low-budget development board with the Altera MAX 10 FPGA chip. The board contains a number of components enabling learning and prototyping of projects based on FPGA chips

The motor driver card can drive 24 servo motors at most. It can be used to drive a multiple-joint robot machine, such as Hexapod Robot, Biped Robot, and Arm Robot. P0288

8 Mega Pixel Digital Camera Package with FMC interface

No product available!

The Video and Embedded Evaluation Kit - Multi-touch, Second Edition, on Cyclone® V SoC Development Board (VEEK-MT2-C5SoC)

No product available!

The ADC-SoC is a SoC FPGA motherboard with dual-channel high-speed ADC

No product available!

A set of elements designed for evaluation sets with programmable circuits of the Cyclone V SoC FPGA family, which includes; 7-inch TFT display with touch support (5-points), 8 megapixel camera with autofocus and sensors (light, accelerometer, gyroscope, magnetometer). Terasic P0494

No product available!

Terasic HDMI-FMC is a HDMI transmitter/receiver daughter board with FMC (FPGA Mezzanine card) interface

Gigabit Ethernet transceiver with an FMC interface. Up to 1 Gbps network transfers with the host board using an FMC connector. NET-FMC can be connected any FMC(HPC) interfaces. Terasic P0481

No product available!

The DE10-Standard Development Kit presents a robust hardware design platform built around the Intel System-on-Chip (SoC) FPGA, which combines the latest dual-core Cortex-A9 embedded cores with industry-leading programmable logic for ultimate design flexibility. P0493

The DE10-Standard Development Kit presents a robust hardware design platform built around the Intel System-on-Chip (SoC) FPGA, which combines the latest dual-core Cortex-A9 embedded cores with industry-leading programmable logic for ultimate design flexibility. P0493

No product available!

Programmable Logic IC Development Tools Cyclone V SE 5CSEMA4U23C6N + 800MHz Dual-core ARM Cortex-A9 processor. Terasic P0496

No product available!

Programmable Logic IC Development Tools Cyclone V SE 5CSEMA4U23C6N + 800MHz Dual-core ARM Cortex-A9 processor. Terasic P0496

VEEK-MT2S is a development board based on the Cyclone V SX SoC Cyclone V SX SoC-5CSXFC6D6F31C6N chip. Included in addition to the board with programmable FPGA, there are also a 7-inch TFT touchscreen with a resolution of 800 x 480 pixels, 8 megapixel camera (3264 x 2448 pixels), light sensor IMU 9DOF sensor (accelerometer, gyroscope, magnetometer) . Terasic K0161

No product available!

The DE10-Standard Development Kit presents a robust hardware design platform built around the Intel System-on-Chip (SoC) FPGA, which combines the latest dual-core Cortex-A9 embedded cores with industry-leading programmable logic for ultimate design flexibility. P0493