zł5,085.72 tax excl.

FPGA starter kit equipped with Cyclone V GT with 301K LE and minicomputer with Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). The FPGA module has 1 GB DDR3 memory, 64 MB SDRAM memory, UART-USB interface and extensions such as GPIO and Arduino. Terasic P0650

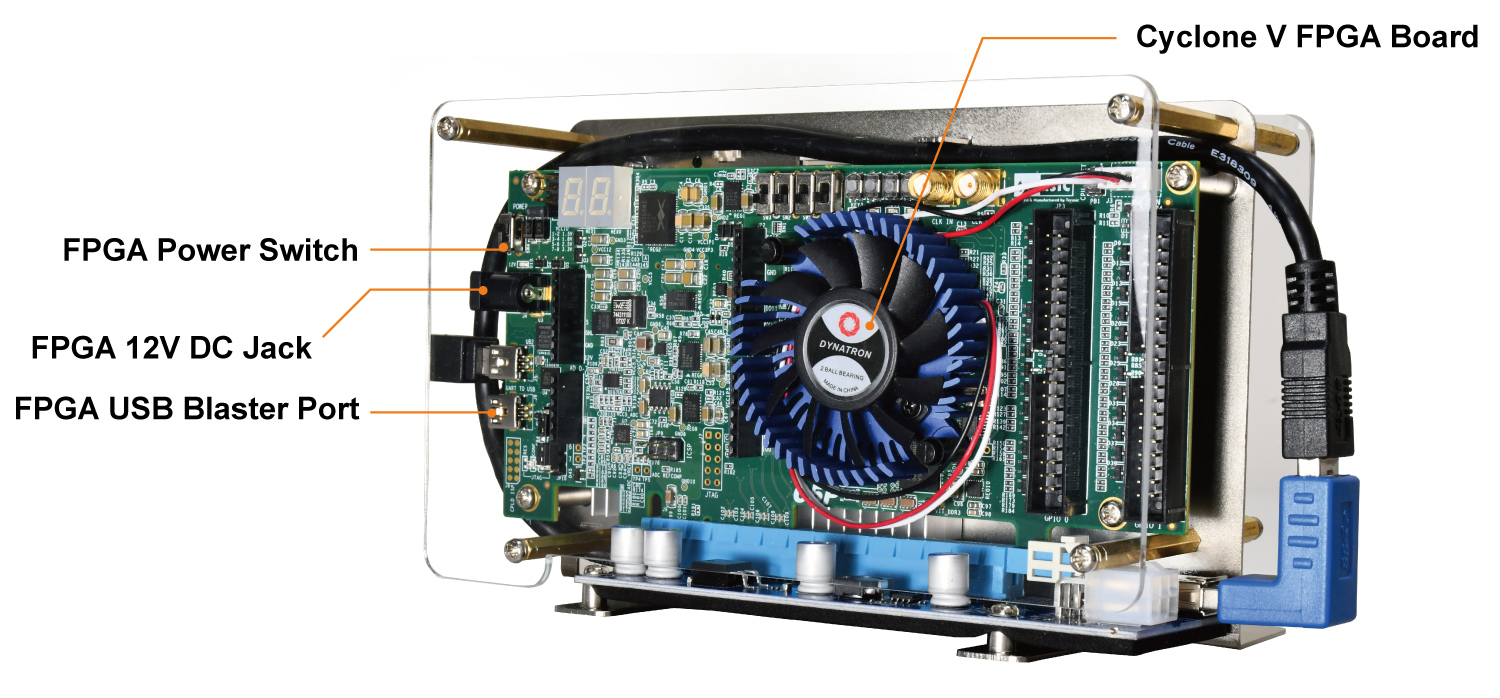

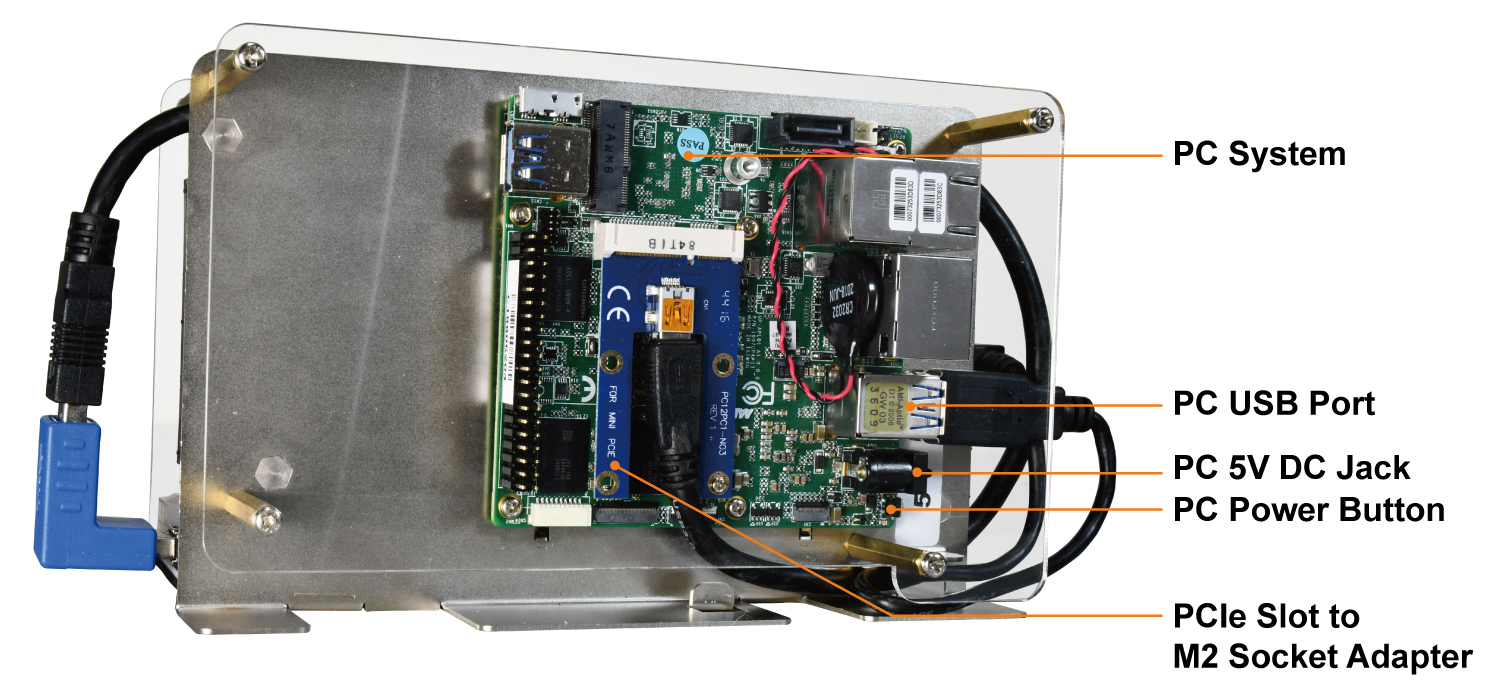

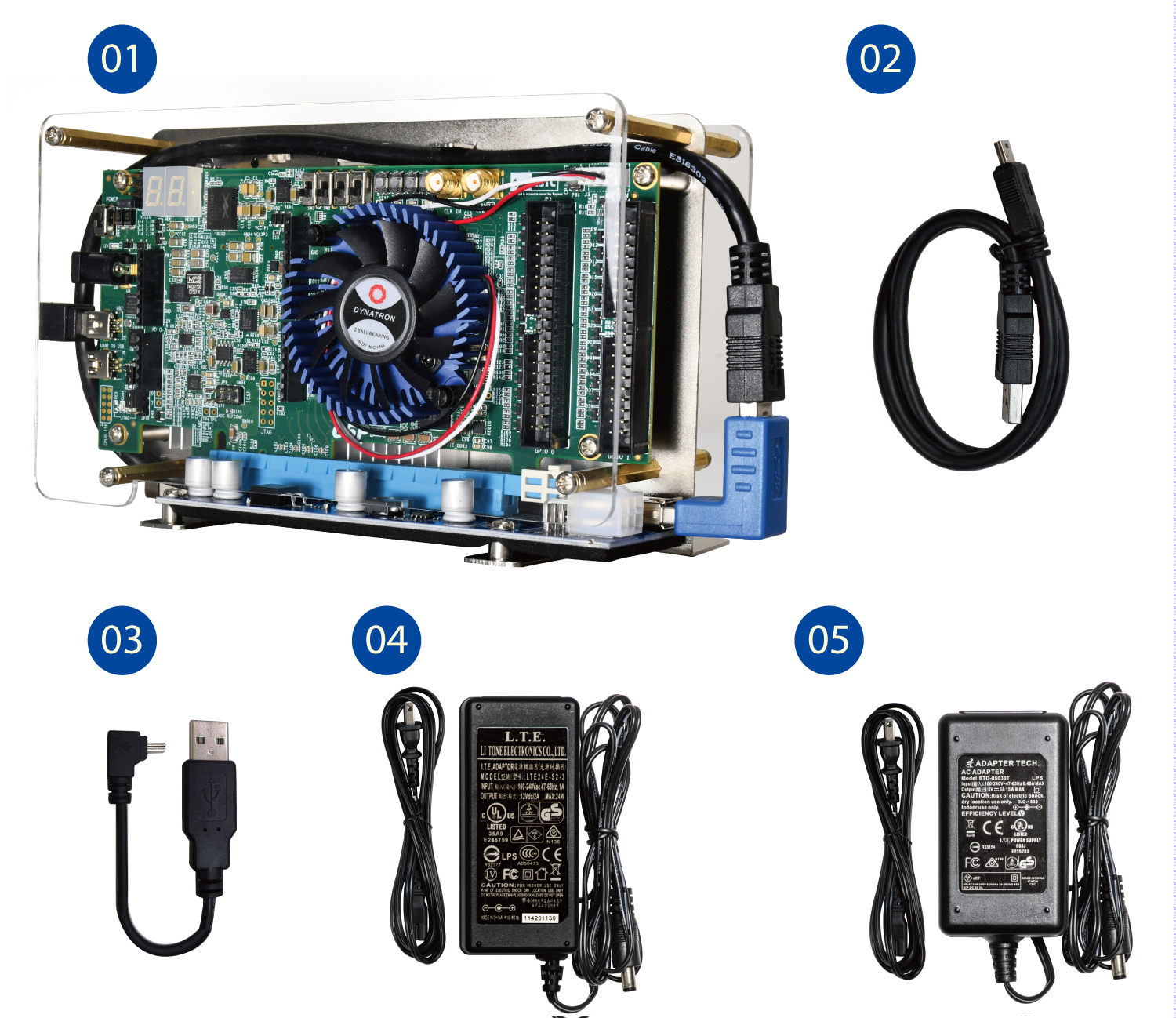

OpenVINO is an FPGA starter kit in the form of a card with a PCIe connector and a PC kit with an Intel Celeron Dual Core chip. The kit is equipped with a programmable Cyclone V GT system with 301K LE and supports PCIe Gen 2x4. FPGA has 1 GB of DDR3 memory, 64 MB of SDRAM memory, UART-USB interface and extensions such as GPIO or allowing to connect Arduino extensions. The PC system is equipped with 64 GB eMMC memory and 4 GB DDR4 RAM. This makes the OpenVINO starter kit a configurable platform combining high computing performance and low energy consumption.

The OpenVINO package contains reference projects for all peripherals of the set and detailed instructions for programmers.

CPU system (PC)

FPGA OpenVINO Starter Kit

Description of components and connectors

Block diagram

Manufacturer BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Poland sprzedaz@kamami.pl 22 767 36 20

Responsible person BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Poland sprzedaz@kamami.pl 22 767 36 20

FPGA starter kit equipped with Cyclone V GT with 301K LE and supports PCIe Gen 2x4. The board has 1 GB DDR3 memory, 64 MB SDRAM memory, UART-USB interface and extensions such as GPIO and Arduino. Terasic P0559

No product available!

[EDUCATIONAL PRICE] FPGA starter kit equipped with Cyclone V GT with 301K LE and supports PCIe Gen 2x4. The board has 1 GB DDR3 memory, 64 MB SDRAM memory, UART-USB interface and extensions such as GPIO and Arduino. Terasic P0559

No product available!

[EDUCATIONAL PRICE] FPGA starter kit equipped with Cyclone V GT with 301K LE and minicomputer with Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). The FPGA module has 1 GB DDR3 memory, 64 MB SDRAM memory, UART-USB interface and extensions such as GPIO and Arduino. Terasic P0650

No product available!

TerasIC SDI HSMC is a specialized module for FPGA projects in the field of video transmission, offering support for SDI and AES standards and full compatibility with HSMC platforms. It is ideal for developing broadcasting solutions, signal analyzers, and professional video applications.

TerasIC INK is a comprehensive hardware platform for developing and testing industrial FPGA-based applications, offering full support for serial communication and industrial Ethernet. The kit enables rapid development of automation and data transmission solutions in environments requiring high reliability.

No product available!

TerasIC DE0 is a complete evaluation kit based on the Cyclone III FPGA, designed for learning, testing, and implementing digital systems. It offers a wide range of interfaces and peripherals enabling the creation of complex projects for both educational and industrial purposes.

No product available!

[EDUCATIONAL PRICE] Terasic DE0 Board evaluation kit for Altera Cyclone III FPGA devices. It is equipped with all basic peripherals enabling research and evaluation work with FPGAs, including a JTAG programmer-configurator. The reduced price (compared to the standard Terasic DE0 version) applies exclusively to schools, universities, lecturers, pupils, and students.

TerasIC SATA/SAS HSMC is a specialized expansion card enabling the implementation and testing of mass storage interfaces in FPGA systems. With support for SATA and SAS protocols and compatibility with advanced FPGA devices, it serves as a tool for developing data storage applications, compliance testing, and SoC system development.

No product available!

TerasIC XTS-HSMC is an expansion card for FPGA platforms with transceivers, enabling signal conversion to SMA connectors and rapid prototyping of high-throughput interfaces. It is useful in compliance testing, transmission quality evaluation, and projects requiring reliable data transfer at gigabit speeds.

No product available!

TerasIC AD/DA Data Conversion Card is a universal analog-to-digital and digital-to-analog data conversion card designed for FPGA systems. With high sampling speed and a built-in audio codec, it is well-suited for DSP, telecommunications, and educational applications.

No product available!

TerasIC ADA-HSMC is a high-performance AD/DA conversion card for FPGA systems, offering high precision and flexibility in DSP and communication applications. With support for HSMC and GPIO interfaces, it provides wide compatibility with Terasic and Altera development boards, enabling rapid development of signal processing systems.

No product available!

TerasIC DVI-HSMC is an FPGA expansion card with a DVI transmitter and receiver, enabling support for high-resolution video signals in multimedia projects and image processing systems. With compatibility with Terasic and Altera platforms, it offers rapid deployment and testing of visual applications based on FPGA devices.

TerasIC ICB-HSMC is a communication card for FPGA systems, equipped with RS-232, RS-485, and CAN interfaces, as well as GPIO and PIO ports for expansion. It enables rapid deployment and testing of industrial communication systems and the implementation of fieldbuses in automation and control applications.

No product available!

TerasIC NET is an HSMC-standard Ethernet module enabling rapid implementation of network communication in FPGA systems. With support for speeds from 10 Mb/s to 1 Gb/s and full integration with FPGA devices, it is a convenient tool for designing applications that require reliable network communication.

No product available!

TerasIC USB Blaster Download Cable (UBT) is a fully Altera USB Blaster–compatible JTAG/ISP programmer for CPLD and FPGA devices. With a reliable design and resistance to interference, it is a universal tool for designers working with Altera programmable devices. TerasIC P0302

TerasIC ADA-GPIO is an AD/DA conversion card enabling compatibility with multiple FPGA boards through GPIO and HSMC interfaces. With high sampling speed and wide compatibility, it is well-suited for DSP, educational, and communication applications.

No product available!

The TerasIC P0057 kit enables testing, debugging, and signal simulation in systems using the HSMC interface. It is intended for design and diagnostic work with FPGA main boards and other systems equipped with an HSMC connector.

No product available!

FPGA starter kit equipped with Cyclone V GT with 301K LE and minicomputer with Intel Celeron Dual Core (64 GB eMMC, 4 GB RAM). The FPGA module has 1 GB DDR3 memory, 64 MB SDRAM memory, UART-USB interface and extensions such as GPIO and Arduino. Terasic P0650