- Out-of-Stock

Overview

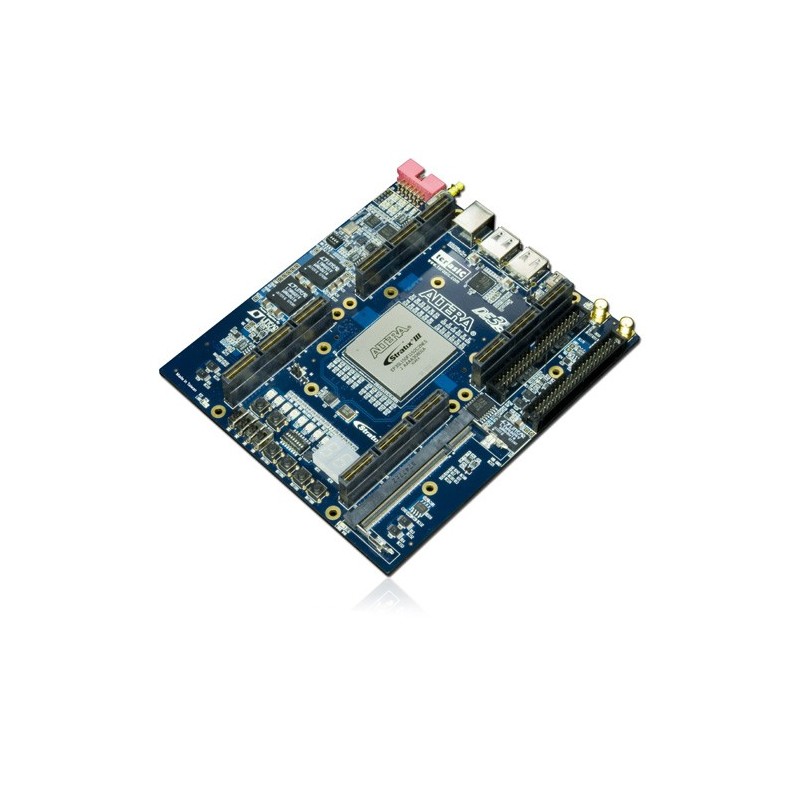

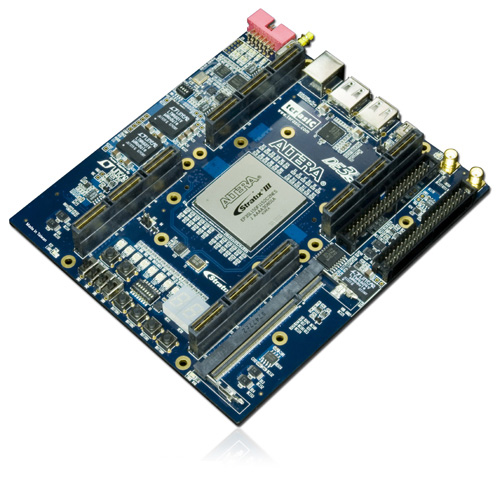

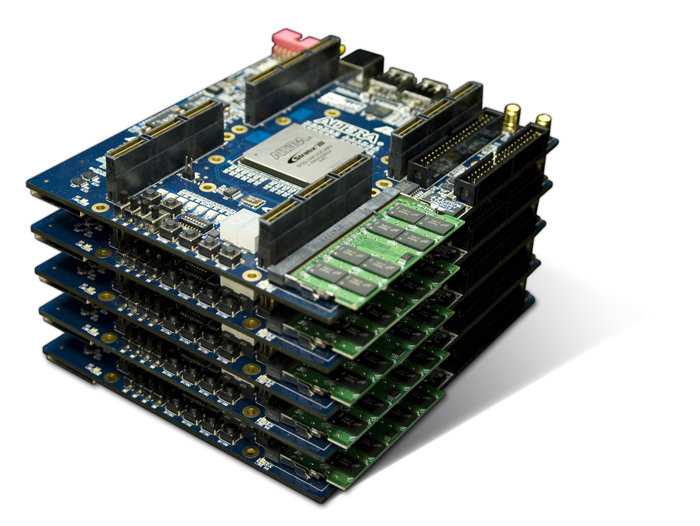

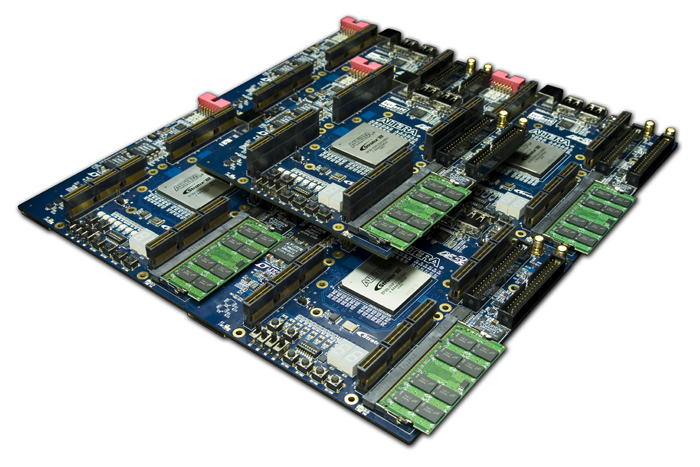

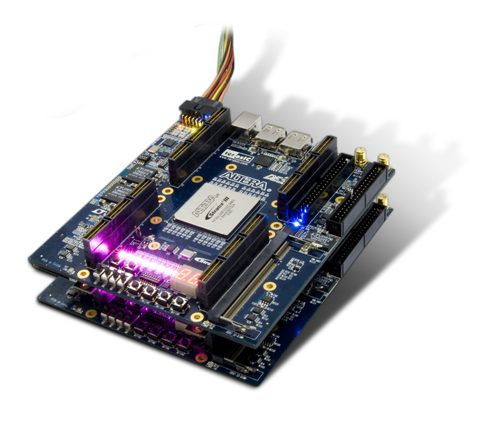

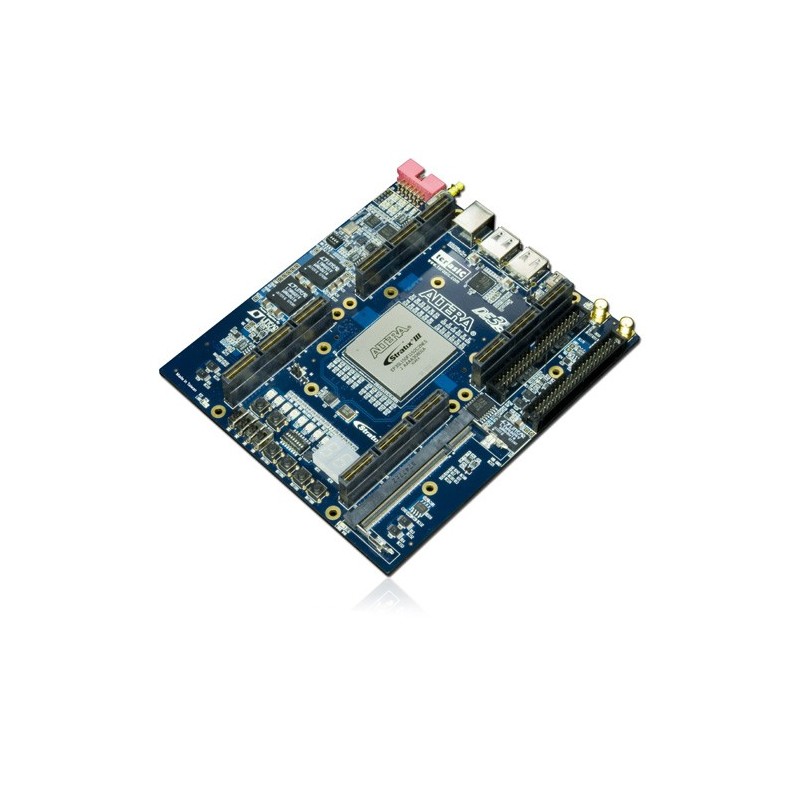

The Altera DE3-150 Development and Education board allows researchers and engineers to access the world's highest density and highest performance FPGA - the new Stratix III. Starting with the Stratix III 3SL150 (142K logic elements), DE3 is the perfect platform for creating your cutting edge design in programmable logic. The DE3-150 board can be stacked up to create a programmable fabric that is unequaled by anything other board system in the world.

DE3 boards include the DE3-340 (338K logic elements) and the DE3-260 (254.4K logic elements) that is optimized with extra on-chip multipliers needed for DSP research and development. All of the DE3s can be stacked and all share the same set of function from the Terasic's daughter cards connected to them.

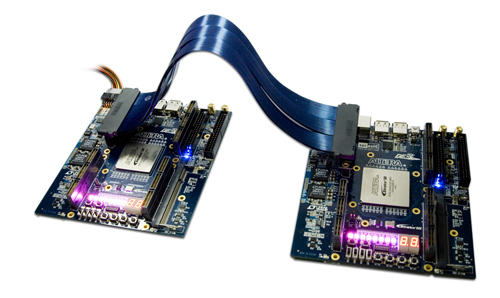

Multiple DE3s can be joined together to increase design gate count and performance.

|

|

||

|

|

* Power Solution for Altera FPGAs

Linear Power Chips on DE3

LTM4601IV#PBF

LTC3026EMSE

LT1963AES8

LTM4604EV#PBF

Specification

FPGA Devices

The DE3 board has powerful features that allow the user to implement resource and time consuming designed circuits, specifically for high-speed application and projects with complex algorithms.

High Speed Samtec Cable: REF-136223-02 (QSH-090-01-F-D-A-K)

High speed I/O performance: The live test shows that the highest speed I/O transmission reaches the ultimate 1.25 Gbps (the top limitation of Stratix III).

![]() Connect COMM

Connect COMM

Connect COMM with DE3

Layout

Resources

| Title | Version | Size(KB) | Date Added | Download |

|---|---|---|---|---|

| DE3 User manual | - | 6006 | 2009-11-09 |  |

DE3 System Builder, a powerful tool comes with the DE3 board. This tool can help users to create the Quartus II project files for DE3 board basic on their custom design. The top-level design file, pin assignment, and I/O standard setting for the DE3 board will be generated automatically by the DE3 System Builder.

The generated Quartus II project files include:

The DE3 board comes with a PC-based Control Panel that allows users to access various components on board. The host computer communicates with the board via USB port. The tool can be used to verify the functionality of components.

|

|

Kit Contents

Manufacturer BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Poland sprzedaz@kamami.pl 22 767 36 20

Responsible person BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Poland sprzedaz@kamami.pl 22 767 36 20

No product available!

No product available!

No product available!

No product available!

No product available!

No product available!

No product available!

No product available!

No product available!

No product available!

No product available!

No product available!

Wixel Pair (Fully Assembled) + USB Cable

No product available!

No product available!

MinIMU-9 Gyro, Accelerometer, and Compass (L3G4200D and LSM303DLM Carrier)

No product available!

Rechargeable NiMH Battery Pack: 6.0 V, 350 mAh, 3+2 2/3-AAA Cells, JR Connector

No product available!

Altera DE3 Development System