zł21,487.65 tax excl.

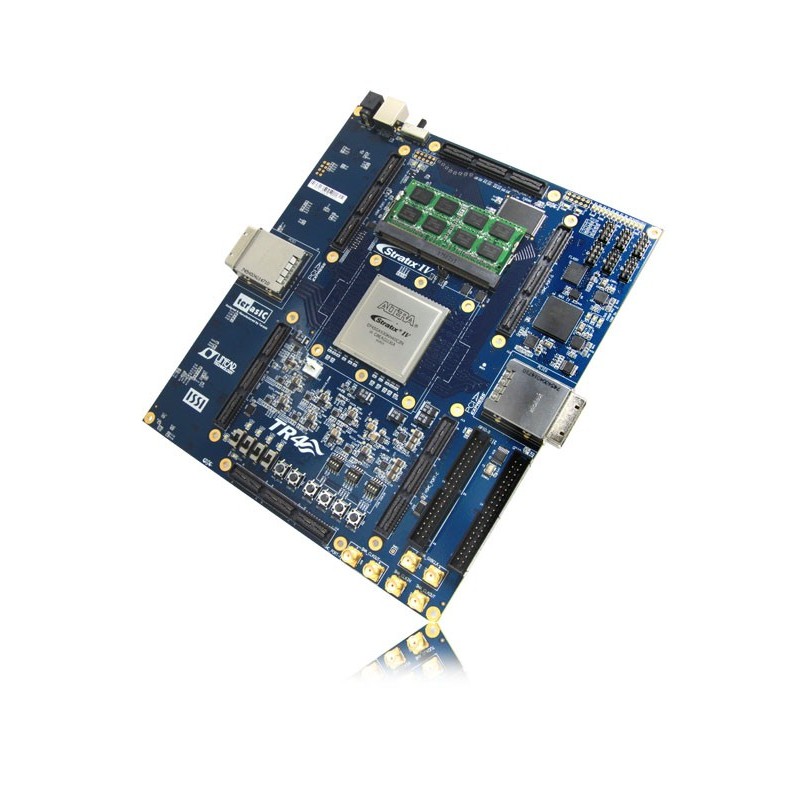

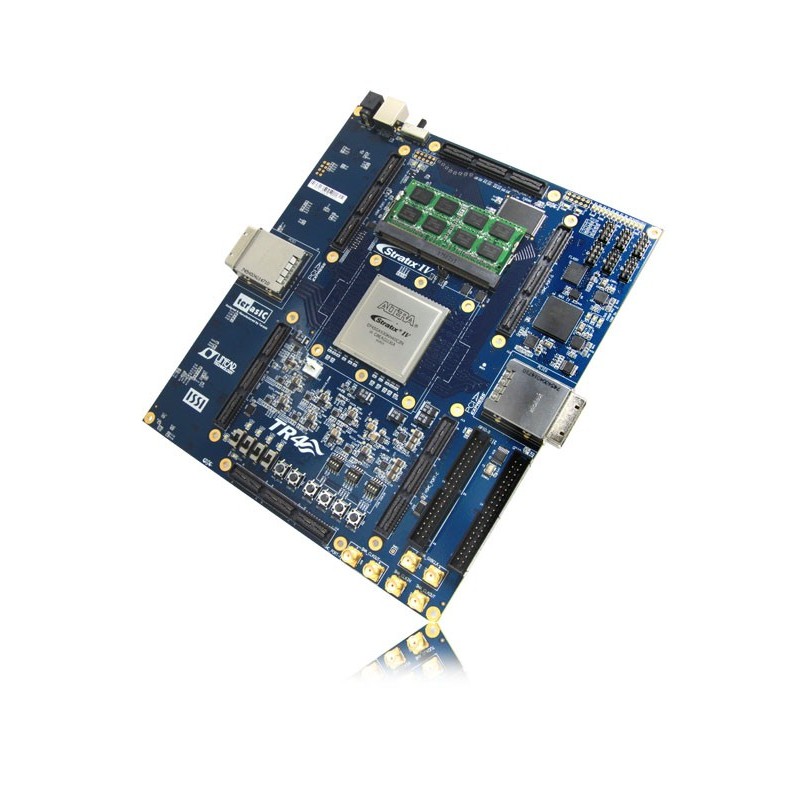

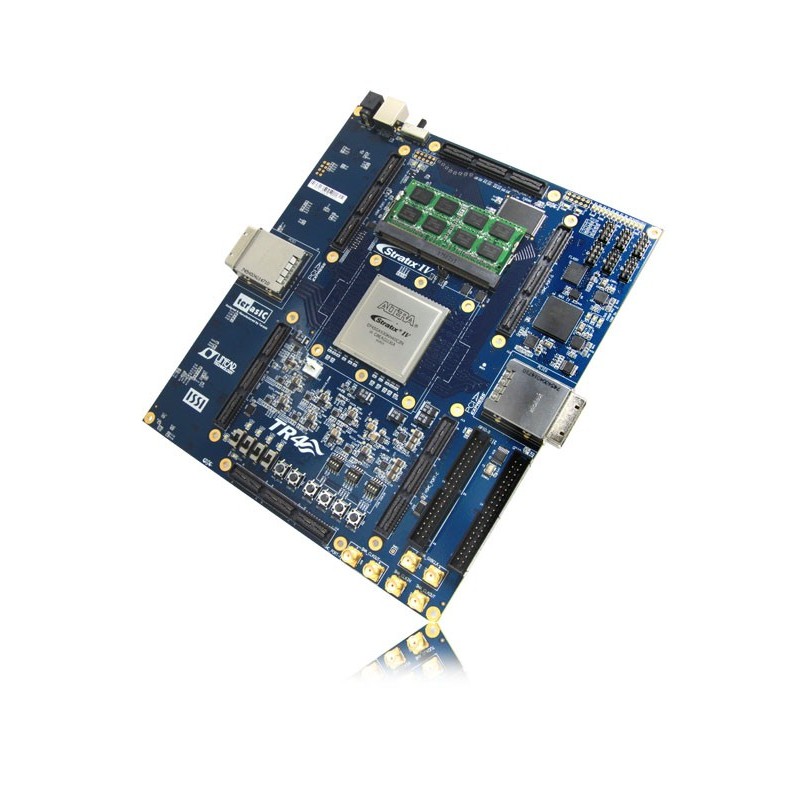

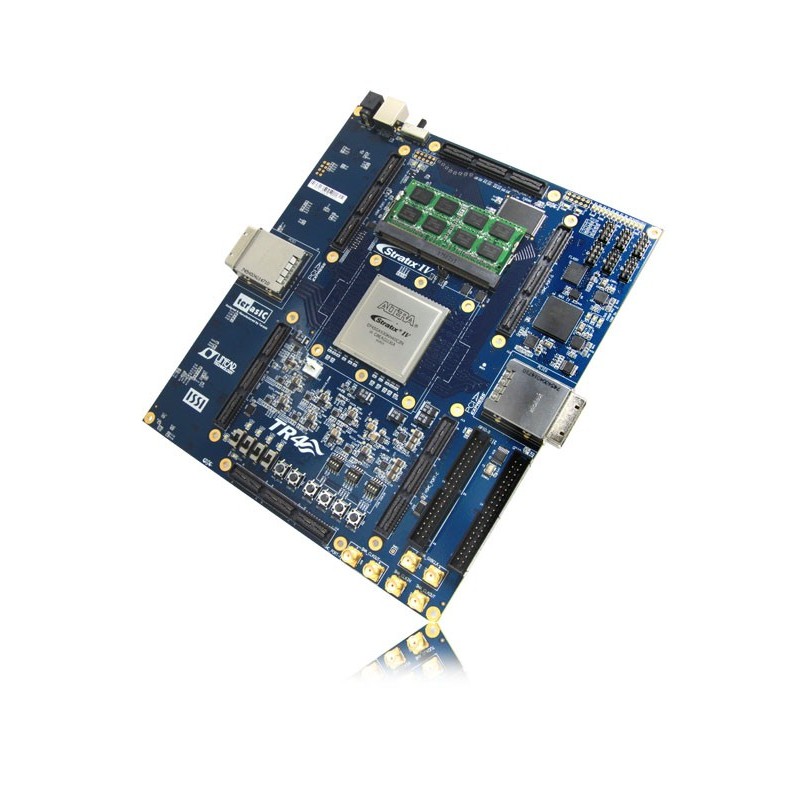

TerasIC TR4-230 (P0107) provides a development platform based on the Stratix IV GX FPGA, featuring a wide range of interfaces and support for PCI Express projects and high-speed DDR3 memory. The solution is designed for communication systems, ASIC prototyping, and applications requiring high logic resource capacity.

The TR4-230 development kit provides an advanced hardware platform designed for digital systems requiring high bandwidth, substantial logic performance, and extensive memory interface support. The Stratix IV GX EP4SGX230 FPGA delivers 228,000 logic elements, 1,288 18×18 multipliers, and 17,133 Kbit of embedded memory, making it ideal for applications that heavily utilize FPGA resources.

The board features a DDR3 SO-DIMM socket supporting up to 4 GB of memory at up to 533 MHz, providing a theoretical bandwidth of up to 68 Gb/s. It also includes 64 MB of Flash and 2 MB of SSRAM. The MAX II CPLD EPM2210 manages FPGA configuration, while the built-in USB Blaster enables direct programming and debugging through the Quartus II software suite.

Expansion capabilities are ensured by six HSMC connectors, two PCIe x4 slots, and two 40-pin expansion headers. With support for transceivers operating up to 8.5 Gb/s and 52 LVDS channels, the board enables development of high-speed communication systems and multi-board FPGA designs. Power is supplied via a 19 V DC input, and SMA connectors allow for connection to external clock sources and differential signal testing.

Manufacturer BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Poland sprzedaz@kamami.pl 22 767 36 20

Responsible person BTC Korporacja sp. z o. o. Lwowska 5 05-120 Legionowo Poland sprzedaz@kamami.pl 22 767 36 20

The Video and Embedded Evaluation Kit - Multi-touch, Second Edition, on Cyclone® V SoC Development Board (VEEK-MT2-C5SoC)

No product available!

The A-Cute Car is an FPGA-based three-wheeled robotic car kit. This car can provide higher operation performance than the MCU based robotic car, because the FPGA provides more powerful computing power than the MCU. P0467

No product available!

No product available!

No product available!

The Terasic VEEK-MT2 set provides a complete hardware-software platform for designing embedded and multimedia systems using FPGA chips. It enables the creation and testing of interactive, control, and measurement applications thanks to an extensive base of interfaces, memory, and sensors.

No product available!

Compact FPGA kit with Intel Arria 10 GX chip equipped with 8 GB DDR4-2133 memory and Thunderbolt 3 communication connector. Can be used directly on laptops or other portable devices. Terasic FLIK P0642

No product available!

Computation accelerator module based on Intel® Agilex ™ FPGA. It has a PCI Express Gen 4.0 x16 slot, two 200G QSFP-DD connectors, and offers 32GB DDR4. Terasic DE10-Agilex (P0701)

No product available!

The DE10-Standard Development Kit presents a robust hardware design platform built around the Intel System-on-Chip (SoC) FPGA, which combines the latest dual-core Cortex-A9 embedded cores with industry-leading programmable logic for ultimate design flexibility. P0493

No product available!

Programmable Logic IC Development Tools Cyclone V SE 5CSEMA4U23C6N + 800MHz Dual-core ARM Cortex-A9 processor. Terasic P0496

TerasIC ADA-GPIO is an AD/DA conversion card enabling compatibility with multiple FPGA boards through GPIO and HSMC interfaces. With high sampling speed and wide compatibility, it is well-suited for DSP, educational, and communication applications.

No product available!

TerasIC CLR-HSMC (P0079) enables the integration of industrial cameras with a Camera Link interface into FPGA boards via the HSMC connector, supporting image transmission in base, medium, and dual base modes. The module is used in vision systems, production lines, and projects involving real-time image processing.

No product available!

SoM module with SoC connecting the FPGA with the ARM Cortex-A9 core. The board is equipped with DDR4 Eadge connector (with 3.3 V power supply). P0553

No product available!

DE1-SoC + 5 points multitouch display MTL2

No product available!

[EDUCATIONAL PRICE] FPGA starter kit equipped with Cyclone V GT with 301K LE and supports PCIe Gen 2x4. The board has 1 GB DDR3 memory, 64 MB SDRAM memory, UART-USB interface and extensions such as GPIO and Arduino. Terasic P0559

No product available!

TerasIC TR4-230 (P0107) provides a development platform based on the Stratix IV GX FPGA, featuring a wide range of interfaces and support for PCI Express projects and high-speed DDR3 memory. The solution is designed for communication systems, ASIC prototyping, and applications requiring high logic resource capacity.